ApostArqIok

-

Upload

elias-santos -

Category

Documents

-

view

214 -

download

0

description

Transcript of ApostArqIok

Arquitetura de um microcomputador

PAGE

Centro Federal de Educao Tecnolgica do Rio Grande do Norte

Unidade de Ensino de Natal

Gerncia de Tecnologia da Informao e Educacional de Telemtica

Apostila de Curso

Verso 01.2000

Professora:

Anna Catharina

Material adaptado da apostila da disciplina de Microprocessadores do prof. MSc. Jos Alberto Nicolau de Oliveira, DEE, UFRNFevereiro/2000

Sumrio

11Introduo a Microprocessadores

1.1Arquitetura de Computadores11.2Arquitetura Bsica de Microprocessadores31.3Evoluo dos Microprocessadores52Anlise de um Microprocessador Genrico72.1Arquitetura Interna72.1.1Unidades Funcionais72.1.2Estrutura Pipelined82.2Funo dos Pinos102.3Sistema de Clock e Ciclos de Barramento133Sistema de Memria de Computadores143.1Estrutura de Memria143.1.1Terminologia143.1.2Armazenamento de Informaes na Memria173.2Organizao da Memria Principal193.2.1Organizao Modular da Memria193.2.2Organizao Lgica203.2.3Organizao Fsica213.2.4Acesso Memria223.3Memria Cache233.3.1Arquitetura de um Sistema Cache233.3.2Taxa de Acerto244Arquitetura de Software de um Microprocessador254.1Modelo de Software254.2Registradores264.2.1Registradores de Dados (Registradores de Uso Geral)264.2.2Registradores de Segmento274.2.3Registradores Ponteiros e de ndice (Registradores de Deslocamento)294.2.4Registrador de Flags294.3Pilha314.4Modos de Endereamento de Memria324.4.1Modo de Endereamento por Registro334.4.2Modo de Endereamento Imediato344.4.3Modo de Endereamento Direto354.4.4Modo de Endereamento Indireto por Registro364.4.5Modo de Endereamento por Base374.4.6Modo de Endereamento Direto Indexado384.4.7Modo de Endereamento por Base Indexada395Programao em Linguagem Assembly415.1Segmentao e Estrutura de Programao (Programa Bsico)415.1.1Sintaxe dos Comentrios415.1.2Sintaxe das Instrues e Diretivas do Assembly425.1.3Modelo de Programa Assembler Simplificado (.EXE)425.1.4Diretivas Simplificadas de Definio de Segmentos435.1.5Operadores de Referncia a Segmentos no Modo Simplificado445.2Ferramentas para Montagem, Ligao e Depurao de Programas445.2.1Montador Assembler (TASM)445.2.2Ligador (TLINK)445.2.3Depurador Turbo Debugger (TD)455.3Diretivas do Assembler465.3.1Diretivas de Equivalncia para o Programa (Definio de Constantes)465.3.2Diretiva de Definio de Base Numrica465.3.3Diretivas de Definio de rea de Armazenamento de Dados (Variveis)465.3.4Diretivas de Definio de Procedimentos485.3.5Diretivas de Controle do Assembly485.4Operadores do Assembler485.4.1Operadores para Dados485.4.2Operadores de Especificao de Tamanho495.5Conjunto de Instrues Assembly505.5.1Instrues para Transferncia505.5.2Instrues Aritmticas515.5.3Instrues Lgicas535.5.4Instrues que Modificam Flags545.5.5Instrues de Chamada e Retorno de Subrotinas545.5.6Instrues para Manipulao de Pilha555.5.7Instruo NOP555.5.8Instrues de Entrada e Sada555.5.9Instruo de Comparao565.5.10Instrues de Desvio565.5.11Instrues de Repetio585.6Programao Estruturada em Assembly595.6.1Ferramentas Utilizadas em Controle de Fluxo595.6.2Estrutura Se-Ento-Seno595.6.3Estrutura Repita-At que605.6.4Estrutura Repita-Enquanto605.6.5Estrutura Enquanto-Repita605.6.6Estrutura For (Para)615.6.7Estrutura Case616Interrupes e Excees626.1Vetores e Descritores de Interrupo636.2Interrupo por Software: Comandos INT e IRET656.3Interrupo por Hardware: Controlador de Interrupes 8259676.4Habilitao, Desativao ou Mascaramento de Interrupes686.5Interrupes Internas e Excees69Anexo A Tabela ASCII70Anexo B Cdigo Estendido do Teclado72Anexo C Interrupes BIOS e DOS72Interrupes do BIOS72Interrupes do DOS72

1 Introduo a Microprocessadores

1.1 Arquitetura de Computadores

Embora tenham ocorrido revolucionrias transformaes na rea de Eletrnica, os microcomputadores de hoje ainda mantm a mesma concepo funcional dos primeiros computadores eletrnicos. Tal concepo, conhecida como Arquitetura de Von Neumann, definida da seguinte forma:

Uma unidade central de processamento recebe informaes atravs de uma unidade de entrada de dados, processa estas informaes segundo as especificaes de um programa armazenado em uma unidade de memria, e devolve os resultados atravs de uma unidade de sada de dados.

A Figura 1 mostra, por diagrama de blocos, a organizao de um sistema com estas caractersticas. O sistema de computador envolve, como pode ser visto, o computador e os elementos geradores e receptores de informaes.

Figura 1 Organizao de um sistema de computador Unidade Central de Processamento (CPU) SYMBOL 174 \f "Symbol" a unidade gestora do computador capaz de administrar todas as operaes de leitura/escrita da memria ou de uma unidade de entrada/sada de dados, de executar operaes aritmticas ou lgicas e de interpretar todas as instrues recebidas de um programa que est em execuo.

Microprocessador SYMBOL 174 \f "Symbol" dispositivo LSI (large scale integration alto grau de integrao) que condensa em um nico chip a maioria das funes associadas a uma unidade central de processamento.

Microcomputador ou sistema a microprocessador SYMBOL 174 \f "Symbol" computador que se caracteriza por apresentar blocos lgicos de CPU, memria e E/S bem definidos e onde todas as funes de processamento da unidade central so desempenhadas por um processador (Figura 2).

Figura 2 Sistema de microcomputador

Perifrico SYMBOL 174 \f "Symbol" qualquer elemento gerador ou receptor de informao em sistemas de computadores (Figura 3).

Figura 3 Perifricos de um microcomputador

Unidades de Entrada/Sada SYMBOL 174 \f "Symbol" blocos internos responsveis pelas transferncias de dados entre o microcomputador e qualquer dispositivo perifrico. atravs de uma unidade de entrada de dados que as informaes de perifrico de entrada so levadas CPU ou memria. De forma similar, atravs de uma porta de sada de dados que as informaes so levadas da CPU ou da memria para um perifrico de sada.

Hardware e Software

Hardware o conjunto de dispositivos eltricos/eletrnicos que englobam a CPU, a memria e os dispositivos de entrada/sada de um sistema de computador. O hardware composto de objetos tangveis (circuitos integrados, placas de circuito impresso, cabos, fontes de alimentao, memrias, impressoras, terminais de vdeo e teclados).

O software, ao contrrio, consiste em algoritmos (instrues detalhadas que dizem como fazer algo) e suas representaes para o computador ou seja, os programas.

Qualquer instruo efetuada pelo software pode ser implementada diretamente em hardware e qualquer operao executada pelo hardware pode tambm ser simulada pelo software.

A deciso de se colocar certas funes em hardware e outras em software se baseia em fatores, tais como: custo, velocidade, confiabilidade e possibilidade/facilidade de modificao.

1.2 Arquitetura Bsica de Microprocessadores

Para se compreender bem a arquitetura bsica de um microprocessador (Figura 4) basta associar as operaes que caracterizam uma unidade central de processamento com os elementos funcionais que permitem a sua realizao.

Figura 4 Arquitetura bsica de um microprocessador com FPU e cache interna

1 Para administrar operaes de leitura/escrita da memria ou de uma E/S de dados so necessrias:

uma unidade de controle, que oriente a busca ou o envio das informaes;

uma pequena capacidade de memria onde estas informaes possam ficar temporariamente armazenadas (registrador de uso geral); e

alguns barramentos (ou vias) onde possam ser manipulados os dados, os endereos e os sinais de controle.

2 Para executar operaes aritmticas e lgicas necessria a presena de uma ALU (arithmetic and logic unit unidade lgica/aritmtica) e, nos processsadores mais avanados, uma FPU (float point unit unidade de ponto flutuante) para operaes com nmeros reais. A incluso da FPU veio permitir a execuo de operaes antes s possveis com o auxlio de um coprocessador aritmtico (operaes em ponto flutuante).

3 Para interpretar as instrues estabelecidas por um programa devem existir:

um decodificador de instruo (microcdigo) e;

um registrador de instruo, no qual a instruo recebida fica temporariamente armazenada.

Barramentos

Um barramento ou via ou bus um conjunto de pinos do microprocessador por onde trafegam um ou mais sinais de hardware. Um microprocessador possui trs tipos de barramentos utilizados para transporte: bus de dados, bus de endereos e bus de controle.

Barramento de dados: Barramento bidirecional, utilizado para realizar o intercmbio de dados e instrues com o exterior. Uma das principais caractersticas de um microprocessador o nmero de bits que o barramento de dados pode transferir, que determina se o processador de 8, 16, 32 ou 64 bits. Determina o nmero de bits da palavra de dados que pode ser transferida de/para o microprocessador e, tambm (quase sempre) o tamanho da palavra de dados que pode ser operada pela ALU.

Barramento de endereos: Barramento unidirecional, constitudo de um conjunto de linhas de endereo que indicam a posio de memria onde se encontra o dado requisitado. Uma vez dada a posio, a informao armazenada na memria passar CPU atravs do barramento de dados. Define a quantidade de posies de memria e/ou de portas de entrada/sada que podem ser acessadas pelo microprocessador (para n bits do barramento de endereos, 2n bytes de memria podem ser endereados, ou seja, 2n endereos fsicos podem ser acessados capacidade de endereamento).

Barramento de controle: Barramento bidirecional, formado por um nmero varivel de linhas, atravs das quais se controlam as unidades complementares (habilitao e desabilitao das memrias para leitura e escrita, permisso para perifricos ou coprocessadores acessarem as vias de dados e endereos). Transfere, para as diversas partes do sistema, sinais que definem e orientam toda a sua operao.

Sinais de controle tpicos de um microprocessador so:

leia de uma posio de memria (memory read);

leia de uma porta de E/S (I/O read);

escreva em uma posio de memria (memory write);

escreva em uma porta de E/S (I/O write);

pedido de interrupo de programa (interruption request);

pedido de uso de vias (bus request ou hold request);

pedido de espera (wait ou ready);

sinal de relgio (clock); e

sinal de partida/reincio (reset).1.3 Evoluo dos Microprocessadores

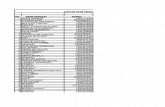

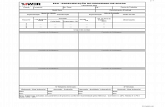

MicroprocessadorBits InternosBits do bus

de dadosBits do bus de endereosCache

L1Observaes

1a Gerao

Intel 4004444Primeiro microprocessador (1971)

Intel 8008888Calculadoras ou sistemas de controle dedicados

Intel 8080/80858816Arquitetura escalar com estrutura seqencial; Outros fabricantes: Motorola (6800) e Zilog (Z80)

2a Gerao

Intel 8086/808816/816/820IBM PC/XT; Arquitetura escalar e estrutura pipelined; Outros fabricantes: Zilog (Z8000) e Motorola (68000)

Intel 80286161624IBM PC/AT 286; Arquitetura escalar e estrutura pipelined; Outro fabricante: Motorola (68010)

3a Gerao

Intel 386DX323232Primeira CPU de 32 bits a incluir gerenciamento de memria; Ambiente multi-usurio; Arquitetura escalar e estrutura pipelined melhorada; Possibilidade de cache L2; Outro fabricante: Motorola (68020/68030)

Intel 386SX321624Idntico ao 386DX, exceto pelos barramentos

4a Gerao

Intel 486DX3232328KBArquitetura escalar e estrutura pipelined otimizada; Possui FPU

Intel 486DX23232328KBPossui FPU; Utiliza duplicao do clock

Intel 486DX432323216KBPossui FPU; Utiliza triplicao do clock

Intel 486SX3232328KBNo possui FPU (coprocessador interno)

Cyrix 486DLC3232321KBSemelhante ao Cyrix 486SLC, com 32 bits

AMD 5x86 32323216KBSemelhante a um 486 de 133MHz, com desempenho de um Pentium-75

Cyrix 5x86 (M I)32323216KBPossui FPU; Caractersticas do Pentium e pinagem do 486DX4

5a Gerao

Intel Pentium32643216KBCache L1 = 8KB instrues + 8KB dados; Projeto hbrido CISC/RISC

AMD K532643224KBSemelhante ao Pentium; Projeto hbrido CISC/RISC; Cache L1 = 16KB instrues + 8KB dados

Cyrix 6x86 (M II)32643264KBCaractersticas do Pentium Pro e pinagem do Pentium; FPU (64 bits); Tecnologia MMX; Arquitetura superescalar; Execuo dinmica

6a Gerao

Intel Pentium Pro32643216KBExecuo dinmica; Tecnologia DIB; Cache L2 de 256 e 512KB

Intel Pentium MMX32643216KBPentium com tecnologia MMX; Esquema duplo de tenso nos circuitos interno (core) e externo

AMD K632643264KBTecnologia MMX; Arquitetura superescalar; FPU (64 bits); Cache L1 = 32KB instrues + 32KB dados

AMD K6-2 (K6 3D)32643264KBSemelhante ao K6. Mais velocidade (barramento externo de 100MHz)

AMD K6-3 (K6+)32643264KBSemelhante ao K6-2. Cache L2 (256KB) integrado ao processador. Cache L3 na placa-me.

Intel Pentium Celeron32643232KBCache L1 = 16KB instrues + 16KB dados; Cache L2 de 128KB integrada; Tecnologia MMX;

FPU (32 e 64 bits); Execuo dinmica; Arquitetura superescalar

Intel Pentium II32643232KBCache L1 = 16KB instrues + 16KB dados; Tecnologia DIB; Tecnologia MMX; Execuo dinmica; Cache L2 de 512KB; Suporte memria expandida de 36 bits (endereamento de memria > 4GB)

Intel Pentium II Xeon32643232KBCache L2 de 1MB ou 2MB; Pentium II projetado para servidores e estaes de trabalho

Intel Pentium III32643232KBCache L2 de 512KB; FPU (32, 64 e 80 bits); Tecnologia MMX; Tecnologia DIB; Execuo dinmica; Suporte memria expandida de 36 bits; Internet Streaming SIMD Extensions; Intel Processor Serial Number

Intel Pentium III Xeon32643232KBCache L2 de 512KB, 1MB ou 2MB; Pentium III projetado para servidores e estaes de trabalho

Durante muito tempo uma disputa desleal vinha sendo travada entre empresas dedicadas produo e comercializao de microprocessadores: de um lado a poderosa Intel, lder de mercado, dominadora de avanadas tecnologias e manipuladora de tcnicas e estratgias que no deixavam folga para concorrncia; de outro lado, todas as outras empresas que sempre tiveram de se contentar em receber migalhas da fatia do mercado restante, sempre com produtos de tecnologia licenciada e atrasados em relao aos produtos da Intel. Entretanto, esta situao comea a mudar. Competidores como AMD, Cyrix, NexGen, Sun Microsystems e algumas outras empresas associadas comeam a introduzir no mercado novos processadores com significativas diferenas dos integrados Intel. Estes projetos originais e altamente otimizados prometem melhor desempenho do que os Pentiums da Intel, ao mesmo tempo mantendo total compatibilidade com os softwares DOS e Windows. O Pentium marca uma bifurcao entre a era exclusiva da Intel e uma nova era, quando diferentes tecnologias esto surgindo, com o desenvolvimento de novas microarquiteturas, capazes, dizem os fabricantes, de superar o desempenho do Pentium.

Percebe-se, com a evoluo tecnolgica e a reduo nos custos de desenvolvimento dos componentes eletrnicos, que:

1. as mquinas CISC (complex instruction set computer) aos poucos absorvem caractersticas tpicas de RISC (reduced instruction set computer), como estrutura superescalar e cache otimizados de memria interna; e

2. as mquinas RISC, em contrapartida, aos poucos vo barateando seus custos, mantendo excelente rapidez na execuo de programas, e passando a competir de igual para igual com as mquinas CISC de ltima gerao.

Dentre as novas tecnologias adotadas, podemos comentar:

MMX (multimedia extensions): Tecnologia projetada para acelerar aplicaes de multimdia e comunicao, adicionando novos conjuntos de instrues e diferentes tipos de dados, alm de explorar o paralelismo (SIMD single instruction multiple data).

DIB (dual independent bus): Arquitetura composta pelo barramento de cache L2 e o barramento de sistema (entre o processador e a memria principal), ambos podendo ser usados simultaneamente.

Cache L2 acoplada (integrada) ao processador dentro de um nico encapsulamento.

Execuo dinmica (Microarquitetura P6): Previso de mltiplos desvios nos programas em execuo, acelerando o fluxo de trabalho do processador; Anlise de fluxo de dados, reordenando o escalonamento das instrues; e Execuo especulativa, antecipando as instrues do programa e executando as que provavelmente sero necessrias.

Internet Streaming SIMD Extensions: Conjunto de novas instrues, incluindo SIMD para ponto flutuante e instrues SIMD adicionais e de controle de cache.

Intel Processor Serial Number: nmero de srie eletrnico do processador que permite sua identificao por redes e aplicaes.

Tenso dupla de operao Intel: 2,0 ou 2,8V para os circuitos internos (core) e 3,3V para os circuitos que fazem ligao externa.

Encapsulamento S.E.C. (single edge contact): integra todas as tecnologias de alto desempenho do processador.

2 Anlise de um Microprocessador Genrico

Por questes didticas, ser feita, nesse captulo, a anlise de um processador genrico com muitas caractersticas comuns aos microprocessadores da famlia 80x86 da Intel.

Para trabalhar com um novo microprocessador, o programador ou projetista deve conhecer detalhes sobre: a arquitetura interna; a funo dos pinos e o timing (temporizao) durante os ciclos de barramento; e a estrutura de software.

Pela anlise da arquitetura interna ser possvel saber quais so e como esto organizados os seus registradores, qual o nmero de bits nos barramentos de dados, de controle e de endereos, quais as caractersticas da ALU, e quais as suas lgicas de decodificao e de controle.

Conhecendo as funes dos pinos e o timing durante os ciclos de barramento, ser possvel ao usurio definir, com exatido, dentre outras coisas, qual a relao pino/tarefa, como e quando uma dada ao do processador se realizar ou, at mesmo, se determinado pedido de servio ser (e quando) ou no atendido pelo processador.

Conhecendo a estrutura de software de ser possvel desenvolver programas sem ter que entrar em detalhes de implementao do chip.

Caractersticas do processador genrico proposto para anlise:

alimentao por fonte nica, baixa potncia de dissipao, sadas bufferizadas;

vias independentes para dados, endereo e controle;

capacidade de endereamento de 1 Mbyte de memria e 64 kbytes de portas de E/S;

grupo de aproximadamente 150 instrues;

instrues diferenciadas para acesso a memria ou a E/S;

lgica interna para controle de pedidos de interrupo de programa e de DMA;

lgica de controle para operao com coprocessador aritmtico; e

arquitetura escalar pipelined implementada por 4 unidades funcionais bsicas: unidades de barramentos, decodificao, execuo e gerao de endereos (UB, UI, UE e UA).

2.1 Arquitetura Interna

2.1.1 Unidades Funcionais

A arquitetura interna do microprocessador caracterizada pela existncia de quatro unidades funcionais bsicas: UB, UI, UE e UA.

A unidade de interfaceamento de barramentos (UB), atravs das interfaces de controle de vias, da interface do bus de endereos e da interface do bus de dados, manipula todos os sinais de controle, endereos e dados necessrios para que ocorram os acessos memria e E/S requeridos pela CPU. Ela tambm responsvel pelo tratamento dos sinais necessrios interface de unidades coprocessadoras e outros barramentos mestres. Alm disso, incorpora uma pequena memria de 8 bytes: a fila de pr-busca (prefetch), onde so armazenados os ltimos dados buscados da memria ou de uma E/S. A UB opera tipicamente por looking ahead, buscando instrues na memria e colocando-as na fila de pr-busca.

A unidade de decodificao de instrues (UI) recebe possveis instrues da fila de pr-busca, decodifica-as (atravs do decodificador de instrues), e gera uma nova fila de instrues pr-decodificadas para a unidade de execuo.

A unidade de execuo (UE) executa as instrues pr-decodificadas pela UI. Caso a instruo exija acessos a memria ou a alguma E/S, as pr-buscas so suspensas e a instruo em curso na UE ter acesso aos barramentos, atravs da UB. UE esto relacionados todos os registradores de uso geral e de controle da ALU.

A unidade de gerao de endereos (UA) responsvel pela gerao dos endereos fsicos necessrios operao da CPU.

Figura 5 Arquitetura interna do processador

2.1.2 Estrutura Pipelined

Os processadores da 1a gerao possuiam uma arquitetura escalar com estrutura seqencial. Dessa forma, a quantidade de ciclos necessrios para executar um conjunto de instrues era sempre igual quantidade total de ciclos alocados para as unidades, uma vez que apenas uma das unidades poderia estar sendo utilizada a cada ciclo.

A partir da 2a gerao, uma estrutura pipelined comeou a ser adotada pelos processadores. Nesse caso, em um determinado ciclo, pode haver mais de uma unidade sendo utilizada, dependendo da alocao de recursos (unidades) das instrues a serem executadas.

A execuo de uma instruo pode ser distribuda nas seguintes fases lgicas para um pipeline de instrues (Figura 6):

1. Determinao do endereo da instruo e busca na memria [IF = instruction fetch]

2. Decodificao da instruo a ser executada [ID = instruction decode]

3. Gerao dos endereos e busca dos operandos [OF = operand fetch]

4. Execuo da instruo [EX = execution]

5. Armazenamento do resultado [WB = write back]

Figura 6 Fases lgicas e recursos fsicos necessrios execuo de instrues em um pipeline

Aps a execuo das instrues possvel determinar a quantidade total de ciclos gastos e calcular a taxa mdia de ciclos por instruo (CPI), dada por: . O CPI significa a quantidade mdia de ciclos necessrios para executar uma instruo.

Uma outra medida que pode ser determinada o ganho da estrutura pipelined sobre a estrutura seqencial. O ganho, tambm conhecido como Speedup, dado por: ou . S(n) ( 1, significa que o desempenho da estrutura pipelined melhor que ou igual ao da seqencial; caso contrrio, teremos 0 < S(n) < 1.

Exemplo: Dado o seguinte conjunto de instrues e os recursos necessrios para sua execuo, calcule o CPI, considerando que as filas presentes nas unidades comportam apenas uma instruo.

I1 = {UB, UI, UE, UA, UB}

I2 = {UB, UI, UE, UE}

I3 = {UB, UI, UE}

I4 = {UB, UI, UA, UB, UE, UA, UB}

I5 = {UB, UI, UE, UA, UB}

I6 = {UB, UI, UE}

A Figura 7 ilustra como instrues so executadas na arquitetura escalar com estrutura pipelined do processador. Observe que, no exemplo, as execues das instrues 1, 4 e 5 exigem acesso aos barramentos externos, enquanto as execues das demais instrues so feitas internamente. Um dado importante para a execuo no pipeline a capacidade das filas presentes na UI e na UB (de instrues decodificadas e de pr-busca), que determina a quantidade mxima de instrues que podero estar presentes nessas unidades. Uma observao deve ser feita quanto UB: a fila de pr-busca armazena instrues a serem decodificadas, no impedindo que outra instruo esteja acessando barramentos para leitura ou escrita de dados na memria. Portanto, a exigncia na UB que apenas uma instruo pode acessar os barramentos em um determinado ciclo. A existncia de uma unidade ociosa configura uma bolha (() no pipeline.

UBI1I2I3I4I1

I4I5I6I4(I5I4

UI(I1I2I3I3I4I5I6I6((

UE((I1I2I2I3(I5I4I6(

UA(((I1((I4(I5I4(

Ciclos1234567891011

Figura 7 Execuo das instrues do exemplo numa estrutura pipeline

Clculos para o Exemplo:

Estrutura pipelined:

Total de Ciclos = 11

N de Instrues = 6

CPI = = 1,83 ciclos/instruo

Estrutura seqencial:

Total de Ciclos = 5+4+3+7+5+3 = 27

N de Instrues = 6

CPI = = 4,5 ciclos/instruo

Ganho da estrutura pipelined sobre a seqencial: S(n) = = 2,45

2.2 Funo dos Pinos

Pela Figura 8, o processador apresenta: um barramento de dados de 16 bits; um barramento de endereos de 20 bits; e um barramento de controle. O barramento de controle, por sua vez, encontra-se dividido nos grupos de:

controle de memria e I/O;

controle de interrupo;

controle de DMA (direct memory access acesso direto memria); e

controle de operao com coprocessador (somente em alguns processadores).

Figura 8 Funo dos pinos do processador genrico

A Tabela 1 lista cada um destes sinais, especificando o nome do pino, sua funo, tipo e nvel ativo.

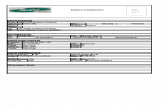

Tabela 1 Tabela descritiva dos pinos do processador genricoNomeFunoTipoNvel

Lgico

CLKClock do sistemaE

A0-A19Bus de endereo (20 bits)S1

D0-D15Bus de dados (16 bits)E/S1

BHE, BLEByte enables Selecionam parte alta (BHE) e baixa (BLE) do bus de dadosS0

HOLDPedido de uso do bus de dados (pedido de DMA)E1

HLDAReconhecimento HOLD (reconhecimento de DMA)S1

INTRPedido de interrupo mascarvelE1

NMIPedido de interrupo no-mascarvelE1

RESETReinicializao do sistemaE1

PEREQRequisio de dados pelo coprocessadorE1

BUSYCoprocessador ocupadoE0

ERRORErro no coprocessadorE0

W/RReferente a escrita (W) ou leitura (R)S1/0

D/CReferente a dados (D) ou controle/cdigo (C)S1/0

M/IOReferente a memria (M) ou E/S (IO)S1/0

ADSStatus de endereo (indicador de ciclo de barramento vlido)S0

READYPedido de espera (por um perifrico) E0

LOCKIndicador de barramento ocupadoS0

Atravs do barramento de dados de 16 bits do processador , possvel se transferir informaes da largura de um byte (8 bits) ou de uma word (16 bits). Os sinais e so usados para indicar se a transferncia de um byte est ocorrendo pela parte menos significativa do barramento de dados (parte baixa: BHE=1 e BLE=0), pela parte mais significativa (parte alta: BHE=0 e BLE=1), ou se est ocorrendo a transferncia de uma word (parte alta + parte baixa: BHE=0 e BLE=0). Enquanto todos os 20 bits do bus de endereos podem ser usados para acessar uma posio de memria, apenas os 16 menos significativos podem ser usados para acessar uma E/S. Desta forma, embora o espao enderevel de memria seja de 1 Mbyte (220), o de E/S de apenas 64 kbytes (216).

Dos trs sinais disponveis para controle de interrupo, o INTR pode ser mascarado por software, o NMI sempre atendido, independentemente da programao, e o de RESET reinicializa o sistema.

Para controle de DMA so disponveis os sinais HOLD e HLDA, os quais permitem que o processador tome conhecimento e sinalize o atendimento de um pedido de uso de vias feito por um outro dispositivo mestre (controlador de DMA). Enquanto durar a concesso do uso de vias (sinal HOLD permanece ativo aps o HLDA), o processador mantm seus pinos de sada em estado de alta impedncia (estado indefinido entre 0 e 1). Durante o DMA, transferncias diretas de dados podem ser feitas entre a memria e o dispoditivo de E/S.

Seguindo o padro das mquinas anteriores ao 486DX, o processador s executa operaes aritmticas com nmeros inteiros. Operaes com nmeros reais s so possveis atravs de bibliotecas matemticas em ponto flutuante ou atravs do uso de um coprocessador aritmtico, o qual partilha com o processador a execuo do programa, tomando para si a execuo das tarefas com nmeros reais. Para viabilizar o uso de um coprocessador aritmtico, so disponibilizados os sinais PEREQ, BUSY e ERROR, os quais permitem que o processador tome conhecimento de um pedido de dados pelo coprocessador, do seu tempo de ocupao e da ocorrncia de erros no tratamento matemtico.

2.3 Sistema de Clock e Ciclos de Barramento

Toda sincronizao de barramento feita a partir do sinal de clock denominado de clock do processador (PCLK). Este sinal, gerado internamente, tem como base de tempo o sinal fornecido na entrada CLK (clock do sistema/externo). Para o processador 8086, o PCLK compreende um perodo igual a duas vezes o do CLK (freqncia de PCLK = ( freqncia de CLK), com ciclo de trabalho (duty cycle) de 50% (Figura 9).

Figura 9 Temporizao genrica

Qualquer operao externa de leitura ou escrita feita pelo processador ocorrer em um ciclo de barramento e ter uma durao mnima de dois perodos de PCLK (T1 e T2). Os ciclos de barramento possveis so mostrados na Tabela 3 e o seu reconhecimento feito atravs da decodificao dos sinais de sada M/ (memria/IO), D/(dados/cdigo) e W/(escrita/leitura).

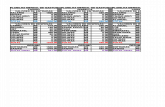

Tabela 2 Sinais M/IO, D/C, W/RM/

D/

W/

Tipo de ciclo de barramento

000Reconhecimento de interrupo

001Processador ocioso (nenhum ciclo de barramento est sendo processado)

010Leitura de dados numa interface de E/S

011Escrita de dados numa interface de E/S

100Leitura de cdigo na memria

101Parado (halt/shutdown)

110Leitura de dados na memria

111Escrita de dados na memria

A sada ADS indica que o os sinais de definio de ciclo de barramento (M/IO, R/W, D/C), cdigo de byte enable (BHE, BLE) e os sinais de endereo (A0 a A15) esto estveis. Esse sinal geralmente aplicado a um circuito de lgica de controle de barramento externo para indicar que uma definio de ciclo de barramento vlido e um endereo esto disponveis. Atravs da entrada READY, possvel estender o ciclo de barramento corrente pela incluso de estados de espera, permitindo que uma memria ou um dispositivo de E/S lento possa ser atendido pelo processador.

Em sistemas multiprocessados, comum o partilhamento de vias de dados, endereos e controle. Para suprir o uso exclusivo de vias durante a execuo de tarefas prioritrias, o processador dispe do sinal de sada LOCK (ativado por software), durante o qual qualquer outro sistema ou dispositivo ficar devidamente informado que nenhuma concesso de vias poder ocorrer naquele momento.

A Figura 10 mostra um timing genrico no qual os seguintes ciclos de barramento possveis esto representados:

C1: leitura de cdigo na memria (W/=0, D/=0 e M/=1); C2: leitura de dados na memria (W/=0, D/=1 e M/=1); C3: ocioso (W/=1, D/=0 e M/=0); e C4: escrita de dados numa interface de E/S (W/=1, D/=1 e M/=0) com pedido de espera (feito atravs da linha READY).

Figura 10 Temporizao genrica

3 Sistema de Memria de Computadores

3.1 Estrutura de Memria

Segundo a Arquitetura de Von Newmann, uma unidade central recebe dados dos dispositivos de entrada, processa-os segundo as especificaes de um programa, e devolve-os atravs de um dispositivo de sada. As instrues do programa e os dados processados residem na memria do computador. Esta memria dividida em uma srie de locaes, cada qual com um endereo associado. Cada locao denominada de byte, o qual formado por 8 bits (unidade binria).

3.1.1 Terminologia

Endereo e locao de memria: O endereo um nmero que identifica a posio (locao) de uma palavra na memria. Cada palavra armazenada em qualquer dispositivo ou sistema de memria possui um nico endereo, expresso como nmeros binrios ou, por convenincia, hexadecimais. Cada locao de memria possui um endereo associado, onde esto presentes os dados a serem acessados.

Operao de leitura: Ao ler o contedo de um endereo, o computador faz uma cpia do contedo. Dessa forma, a operao de leitura chamada de no destrutiva (operao de busca).

Operao de escrita: Quando o computador acessa uma posio de memria e escreve um dado, o contedo anterior completamente perdido. Assim, toda operao de escrita pode ser chamada de destrutiva (operao de armazenamento).

Tempo de acesso: Medida da velocidade do dispositivo de memria. Quantidade de tempo necessria efetivao de uma operao de leitura (tempo decorrido entre o momento da recepo pela memria de um novo endereo e o instante em que a informao daquele endereo fica disponvel).

Memria voltil: Memria que necessita de energia eltrica para reter a informao armazenada. Se a energia for retirada, toda a informao armazenada ser perdida.

Memria no-voltil: Memria que no necessita de energia eltrica para reter a informao armazenada.

ROM (read only memory) memria apenas para leitura: So memrias a semicondutor usadas para armazenar dados e instrues permanentes, que o computador deve executar freqentemente ou durante a inicializao do sistema. Normalmente o contedo de uma ROM gravado no circuito integrado, no podendo ser alterado (no volteis). Aplicaes: firmware, memria de partida fria (bootstrap), tabelas de dados, conversores de dados, geradores de caracteres e de funes.

A principal caracterstica da memria ROM o fato de que suas informaes vm geralmente gravadas de fbrica e so, portanto utilizadas durante toda sua vida til para as mesmas atividades.

Os diversos tipos de ROMs existentes no mercado diferem no modo de programao e na possibilidade de apagamento e de reprogramao. Algumas variaes da ROM so:

EPROM (erasable programmable read-only memory) ROM apagvel programvel: Basicamente uma memria ROM na qual informaes podem ser apagadas atravs de exposio a luz ultravioleta de alta intensidade e reprogramadas eletricamente.

EEPROM (electrically erasable programmable read-only memory) ROM apagvel programvel eletricamente: verso mais barata e prtica da EPROM, a qual utiliza sinais eltricos tanto para sua microprogramao quanto para que suas informaes sejam apagadas. As chamadas memrias flash ou EEPROM flash possibilitam a atualizao do BIOS, por exemplo, sem a necessidade de substituio do chip. Uma vantagem das EEPROMs sobre as EPROMs a possibilidade de apagamento e reprogramao de palavras individuais, em vez da memria inteira.

RAM (random access memory) memria de acesso aleatrio: So memrias de leitura e escrita, usadas para o armazenamento temporrio de dados. As memrias RAM so volteis. Nas memrias RAM, a localizao fsica real de uma palavra no tem efeito sobre o tempo de leitura ou escrita (o tempo de acesso constante para qualquer endereo). Aplicao: memria principal e caches.

Entre os principais tipos de RAM temos:

DRAM (dinamic random access memory) RAM dinmica: Memrias RAM a semicondutor nas quais a informao armazenada no permanecer armazenada, mesmo em presena de alimentao do circuito, a no ser que a informao seja reescrita na memria com determinada freqncia (operao de recarga ou refresh da memria). Caractersticas: alta capacidade de armazenamento, baixo consumo de potncia, velocidade de operao moderada e custo/byte relativamente baixo. Principal tecnologia de implementao de memrias RAM, constituindo-se na representao de nmeros binrios 0 e 1 a partir do carregamento de milhares ou milhes de microcapacitores reenergizados pela passagem de correntes pelas clulas a cada dezena de milissegundos.

SRAM (static random access memory) RAM esttica: Memrias RAM nas quais a informao permanecer armazenada enquanto houver energia eltrica aplicada memria, sem que haja necessidade da informao ser permanentemente reescrita na memria. Caractersticas: baixa capacidade de armazenamento, alta velocidade de operao (baixo tempo de acesso) e alto custo/byte. A principal limitao da DRAM, a velocidade, a principal vantagem da SRAM. Estima-se que o tempo de acesso aos dados na SRAM sejam cerca 25% do tempo de acesso a DRAMs. Uma outra vantagem diz respeito a desnecessidade de reenergizao. No entanto, uma grande limitao decorrente de seu alto custo, o que faz com que esta tecnologia seja usada mais comumente em estruturas cache. Utilizam flip-flops (bipolares ou MOS) como clulas de armazenamento.

Memrias de acesso seqencial (SAM): Utilizam registradores de deslocamento para armazenar os dados que podem ser acessados de forma seqencial, no podendo ser utilizadas na memria principal (baixa velocidade de acesso). Aplicaes: armazenamento e transmisso seqencial de dados codificados em ASCII, osciloscpios digitais e analisadores lgicos, memrias FIFO.

Memrias FIFO (first in first out) primeiro a entrar, primeiro a sair: Memria seqencial que utiliza registradores de deslocamento, na qual as palavras so descarregadas na sada de dados na mesma ordem em que entraram pela entrada de dados. Aplicao: operao de transferncia de dados entre sistemas operando em velocidades muito diferentes (buffers de impressora ou teclado).

Hierarquia de memria: a hierarquia de memria de um computador caracterizada por cinco parmetros: tempo de acesso, tamanho da memria, custo por byte, largura de banda (bandwidth) da transferncia e unidade de transferncia (bytes). A hierarquia de memria em microcomputadores, representada na Figura 11, possui quatro nveis, compostos de: memria secundria, memria principal, caches e registradores.

Figura 11 Hierarquia de memriaMemria secundria ou de massa ou auxiliar: Armazena uma grande quantidade de informao, sendo bem mais lenta que a memria principal, e sempre no-voltil. As informaes armazenadas nos dispositivos de memria de massa so transferidas para a memria principal quando forem necessrias ao computador. Exemplos deste tipo de elemento so as fitas magnticas, os disquetes e os HDs (hard disks).

Memria principal ou primria: Serve para armazenar as instrues e os dados que esto sendo usados pelo processador. Implementada por chips de memrias DRAM. Controlada por uma MMU (memory manegement unit unidade de gerncia de memria) em cooperao com o sistema operacional.

Memria cache: Formada por uma pequena quantidade de memria SRAM, com alta velocidade de acesso. Armazena dados com grande probabilidade de reutilizao, evitando outros acessos memria principal, diminuindo o tempo de acesso ao dado. Existem dois tipos de memria cache, dependendo da localizao em relao ao microprocessador: cache interna ou primria ou L1 (com pequena capacidade, geralmente de 32 kbytes), e cache "externa" (integrada) ou secundria ou L2 (com capacidade mdia de 256 a 512 kbytes).

3.1.2 Armazenamento de Informaes na Memria

A menor quantidade de informao disponvel em qualquer computador o bit. A principal unidade de informao um grupo de bits, denominado palavra. O nmero de bits que formam uma palavra denominado tamanho da palavra do computador. Muitas vezes os computadores so descritos em termos do tamanho da sua palavra, que tambm indica a largura do barramento de dados.

Uma palavra armazenada numa posio de memria pode conter dois tipos de informao: instrues ou dados. Para as instrues, armazenadas em cdigo binrio, o contedo armazenado na memria so comandos que levam execuo de alguma tarefa. Os dados podem ser informaes numricas ou alfanumricas, que podem estar em vrios formatos: nmeros binrios com e sem sinal, nmeros em BCD compactado, nmeros em ponto flutuante, caracteres em BCD ou ASCII.

Apesar de existirem diversos formatos lgicos de armazenamento para dados, no se deve esquecer que, fisicamente, informaes so armazenadas como seqncias de 0 e 1 e que, mais importante ainda, o computador no tem como saber a diferena entre dois contedos. responsabilidade do programador conhecer os tipos de dados que esto sendo armazenados, para assegurar que o programa possa interpret-los e process-los corretamente.

O processador armazena dados na memria de forma linear, em grupos de 8 bits. Primeiro armazenado o byte menos significativo (LSB least significative byte) de uma word e em seguida o byte mais significativo (MSB most significative byte). Por exemplo, o nmero A3C1h armazenado na forma indicada na Figura 12.

Figura 12 Armazenamento de dados na memria

Nmeros binrios no sinalizados e nmeros hexadecimais: Uma forma mais clara de representao dos valores o sistema hexadecimal, que utiliza um conjunto de 16 smbolos: os algarismos de 0 a 9 e as letras de A a F. A cada conjunto de 4 bits em um byte atribui-se um dgito hexadecimal. Ateno! Nmeros em hexadecimal so apenas uma representao de nmeros binrios!!!Caracteres: A cada uma das 256 combinaes possveis em um byte, pode-se atribuir um caractere do alfabeto, minsculos e maisculos, algarismos e smbolos especiais do teclado, caracteres de controle, caracteres semigrficos, smbolos matemticos e letras do alfabeto grego (cdigo ASCII american standard code for information interchange). No se pode esquecer que a cada cdigo ASCII (ou a cada caractere), est associado um nmero de um byte, e portanto, podemos dizer que, por exemplo, A = 65d = 41h = 01000001b.

Valores em BCD compactado: O cdigo BCD (binary decimal code cdigo binrio decimal) utilizado para armazenar dois dgitos decimais em um byte na memria, especialmente para realizar clculos aritmticos. Para isto, pode-se usar a tabela dos nmeros hexadecimais com as combinaes para os algarismos de 0 a 9.

Exemplo: 15310 = 0001 0101 0011BCD = 1001 10012 = 9916

Para cada dgito decimal existe um nibble (quarteto) correspondente em BCD.

Operaes BCD so realizadas como operaes com nmeros binrios. Entretanto, necessrio fazer um ajuste no resultado para que o valor seja um BCD vlido. Portanto, uma soma BCD nada mais que uma soma binria com um ajuste. O ajuste feito adicionando-se 610 = 01102 ao nibble cuja representao binria seja superior a 910.

Exemplo: 4910 + 2110= 0100 1001BCD + 0010 0001BCD = 0110 1010Ajuste:+0110 101020000 01102

0111 0000BCD

Aps o ajuste, o resultado da soma :

0111 0000BCD = 7010 (Tabela 3 Equivalncia entre os sistemas numricos

Valor

BinrioDgito

HexadecimalValor

DecimalDgito

BCD

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

11110

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

150

1

2

3

4

5

6

7

8

9

(((((

Valores sinalizados: Um byte pode armazenar 256 valores diferentes (00h a FFh), atribuindo a cada combinao um valor decimal positivo (010 a +25510). Para armazenar na memria valores positivos e negativos (-12810 a +12710), o bit mais significativo de um byte utilizado para indicar o sinal: 0 para positivo e 1 para negativo em complemento de 2 (ou seja, -B = Complemento de 2(B)). O complemento de 2 consiste em duas operaes: realizao do complemento de 1 (negao bit a bit) e adio com 1.

Exemplo: A = 1210 = 0000 11002

-A = C2(A) = C1(A) +1 = 1111 01002

Internamente, os computadores no realizam operaes de subtrao. A subtrao (AB) feita atravs da soma (A+(-B) = A+Complemento de 2(B)).

Exemplo: A = 710 e B = 810. Calcular, por complemento de 2, o valor C = A B.

A = 0000 01112 e B = 0000 10002Operao 1 ( C1(B): 1111 01112Operao 2 ( adio com 1 (1+0=1, 1+1=0 vai 1):

+1111 0111

0000 0001

1111 1000= C2(B)

Adio (A + C2(B)):

+0000 0111

1111 1000

1111 1111

Logo, A B = 1111 11112.

Note que o dado sinalizado armazenado na memria da mesma forma que um no sinalizado. Para saber quanto vale o nmero, s refazer o complemento de dois, uma vez que [-(-B)=B]. Dessa forma, teramos:

+ 0000 0000

0000 0001

0000 0001

Portanto, 1111 11112 = -1.

3.2 Organizao da Memria Principal

3.2.1 Organizao Modular da Memria

A memria freqentemente separada em mdulos com funcionalidade independente como forma de aumentar a velocidade e a confiabilidade, e flexibilizar possveis mudanas de tamanho. Existem duas formas de organizao modular: high-order interleave e low-order interleave.

High-order interleave: sucessivos endereos de memria presentes no mesmo mdulo (Figura 13). O aumento do desempenho resulta da probabilidade de instrues, tabelas de referncias e dados residirem em mdulos diferentes. Esta separao pode ser forada pelo sistema operacional. Caso isto venha a ocorrer, existe pouca probalidade de uma referncia memria por uma instruo ter de esperar pelo trmino de uma referncia uma tabela ou a um dado.

Figura 13 Organizao high-order interleaveLow-order interleave: endereos sucessivos alocados em mdulos diferentes (Figura 14). Oferece vantagem quanto localidade de programas e dados. Neste mtodo, um dado ou uma instruo tende a estar na localidade de memria mais prxima do ltimo item de dado ou instruo buscado. Existe tambm a possibilidade de um fluxo de palavra poder ser transferido ao processador a uma velocidade maior que aquela organizada em endereos sucessivos.

Figura 14 Organizao low-order interleave

difcil fazer um julgamento sobre qual forma de organizaes melhor. A organizao high-order interleave certamente produz alta confiabilidade ao sistema, uma vez que o processamento pode continuar quando um mdulo no est operando, principalmente nos casos em que um contedo pode ser recuperado da memria secundria e realocado em outro mdulo.

Considerando as duas formas, mais importante que se incorpore uma organizao de memria compatvel com a estrutura do restante do sistema do computador e com a organizao do processador. Com isso, a memria passa a acomodar as caractersticas do resto do sistema.

Uma unidade de gerncia de memria (MMU) utilizada para fazer o endereamento ou acesso memria. A MMU um processador especial usado particularmente para coordenar transferncias de bytes, words e doublewords. Isto tambm facilita o projeto de diferentes computadores usando microprocessador e memrias padres. Funes tpicas de uma MMU incluem: controle de endereamento por segmento e pgina, separao do espao do usurio e do sistema e suporte de hardware para proteo de memria.

3.2.2 Organizao Lgica

Vamos considerar um processador com barramento de endereo de 32 bits, o que possibilita o acesso a 4 Gbytes (232) posies de memria. Essa capacidade de endereamento, entretanto, s possvel quando o microprocessador est trabalhando no modo protegido. No modo real, apenas 20 bits de endereamento so utilizados e, consequentemente, a capacidade de endereamento diminui para 1 Mbyte (220), semelhante ao processador proposto para anlise.

Memria Convencional: at 640 kbytes.

Memria Superior: regio de memria entre 640 kbytes e 1 Mbyte, que abriga a memria de vdeo, a UMB e a EMS Page Frame.Blocos de Memria Superior (UMB): armazenamento de programas residentes e drivers que estariam na memria convencional. Localizao: de 800 a 896 kbytes da memria superior.

EMS Page Frame: bloco de 64 kbytes da memria superior, atravs do qual feito o chaveamento de bancos da memria EMS. Configurao: 4 pginas de 16 kbytes = 64 kbytes. Localizao: 896 a 960 kbytes da memria superior.

Memria Alta (HMA): utilizada para armazenar partes do ncleo do sistema operacional DOS, que poderiam ocupar espao na memria convencional ou na memria superior.

Memria Estendida (XMS): memria acessvel apenas em modo protegido, localizada a partir de 1 Mbyte, abrigando a memria HMA e a memria expandida.

Memria Expandida (EMS): fornece acesso superior a 1 Mbyte de memria em modo real, independente da capacidade de endereamento do processador. Localizao: placas de expanso EMS (XT e 286), ou final da memria estendida (386 ou superior). Utilizao de recursos (drivers) de gerncia de memria que permitem a funo de chaveamento de bancos sem necessidade de hardware adicional (EMM386.EXE e HIMEM.SYS). Total de memria: 64 blocos (frames) de 16 kbytes = 1 Mbyte. Apenas 4 blocos de 16 kbytes podem ser acessados a cada instante. Apesar de no poder armazenar programas a serem executados, possibilita o armazenamento dos dados utilizados pelos programas.

Figura 15 Organizao da memria principal

3.2.3 Organizao Fsica

O espao de endereamento de memria visto como um conjunto de quatro bancos independentes onde cada banco apresenta 1Gbyte de memria (modo protegido) ou de 256 kbytes (modo real).

Os bancos esto relacionados diretamente com os 4 sinais byte enables (BE0, BE1, BE2 e BE3) do processador. A ativao de cada byte enable coloca o banco de memria correspondente em operao.

Caractersticas da organizao fsica:

a memria est organizada em seqncias de doublewords; os bits de endereo (A2 a A31) so aplicados aos quatro bancos em paralelo;

os byte enables selecionam quais bytes da doubleword sero manipulados;

cada doubleword alinhada possui endereo inicial mltiplo de 4; e

cada banco de memria utiliza 8 das 32 linhas do barramento de dados.

Figura 16 Organizao fsica da memria principal3.2.4 Acesso Memria

As Figuras a seguir mostram a forma de acesso a dados de 1, 2 e 4 bytes, respectivamente, a partir do endereo inicial X. importante notar que apenas os bancos selecionados atravs dos byte enables podero realizar operao de escrita ou leitura e a transferncia dos dados feita atravs das linhas correspondentes do barramento de dados.

Figura 17 Acesso a um dado de 1 byte

Figura 18 Acesso a um dado de 2 bytes

Figura 19 Acesso a um dado de 4 bytes

Nem sempre possvel, entretanto, ter todas as words e doublewords alinhadas. Nesse caso, a transferncia ser feita em dois ciclos de barramento. No primeiro, a parte alta do dado ser acessada; no segundo, a parte baixa.

3.3 Memria Cache

Quando um sistema de computador explora um subsistema de memria principal muito grande, esta memria normalmente implementada com DRAMs e EPROMs de alta capacidade de armazenamento, mas de muito baixa velocidade. As DRAMs disponveis apresentam tempos de acesso elevado em relao velocidade do processador, inviabilizando a operao sncrona de um sistema a microprocessador com estes dispositivos de memria. Como no existe disponibilidade de dispositivos com tempo de resposta compatvel, estados de espera so introduzidos em todos os ciclos de acesso a memria de programa ou de dados. Estes estados de espera degradam a performance global do sistema a microprocessador.

Para suprir esta deficincia, um pequeno subsistema de memria, conhecido por memria cache, inserido entre o processador e a memria principal. O sistema de memria cache armazena os dados e cdigos mais recentemente utilizados, permitindo que, ao invs de realizar novos acessos memria principal, estes dados e cdigos sejam acessados diretamente da cache, com a possibilidade de zero estados de espera. Um outro dispositivo, o controlador de memria cache determina, de acordo com as necessidades, quais os blocos de memria a serem movimentados de/para o bloco cache, ou de/para a memria principal.

A observao de que referncias memria feitas em qualquer intervalo de tempo curto de tempo tendem a usar apenas uma pequena frao da memria total chamada princpio da localidade e forma a base de todos os sistemas cache.

Para aumentar ainda a mais o desempenho, os processadores de ltima gerao incorporam caches de dados e de cdigo internamente ao chip (cache L1).

3.3.1 Arquitetura de um Sistema Cache

A Figura 20 apresenta a arquitetura de um sistema cache. interessante notar que um dos lados da memria cache esta ligado ao barramento local do microprocessador e o outro lado est ligado ao barramento da memria principal.

Figura 20 Microcomputador com memria cache L2

A primeira vez que um microprocessador executa um segmento de programa, uma instruo aps a outra lida da memria principal e executada. O grupo de instrues mais recentemente lido ento copiado na memria cache. Como normalmente os softwares implementam seqncias de instrues que so executadas repetidas vezes, o acesso a essas informaes poder ser feito diretamente da cache.

Considere, por exemplo, uma seqncia de instrues em loop. Durante a primeira iterao, o cdigo lido da memria principal pelo microprocessador e automaticamente copiado para a memria cache (Figura 21). As demais iteraes do loop no mais requisitaro acessos memria principal. Durante a execuo do loop, tanto os dados como o cdigo podem ser copiados para a memria cache. Quanto mais acessos memria cache e menos memria principal, melhor ser o desempenho do sistema.

Figura 21 Exemplo de funcionamento da memria cache

3.3.2 Taxa de Acerto

A cache pode reduzir significativamente o tempo de acesso se organizada de forma a conter os dados e o cdigo requeridos pelo processador. Obviamente, quanto maior a cache, maior a chance de que ele contenha as informaes desejadas. Quando o processador necessita de uma informao, o subsistema de memria cache verifica seu contedo. Se a informao estiver presente na cache, o ciclo de memria denominado cache hit (acerto de cache) e a cpia da informao acessada. Caso contrrio, diz-se que ocorreu um cache miss e a informao deve ser buscada na memria principal.

A taxa de acerto (hit rate) a razo entre o nmero de acessos cache e o nmero total de acessos memria.

ou

Se o tempo de acesso de um dado na cache c e da memria principal m, o tempo mdio de acesso de um dado, considerando o sistema de memria cache + memria principal, pode ser calculado por: tmed = c + (1 h) ( m. medida que h (1, todas as referncias podem ser satisfeitas pela cache, e tmed (c. Por outro lado, medida que h (0, uma referncia memria necessria toda vez, de forma que tmed ( (c + m), tempo para verificar o cache (sem sucesso) e para fazer a referncia memria.

Quanto maior a taxa de acerto, maior a eficincia do subsistema de memria cache. A taxa de acerto no uma valor fixo e depende da dimenso e da organizao da cache, do algoritmo de controle usado pela cache e do cdigo em execuo, de tal forma que pode ser completamente distinta para cdigos diferentes.

4 Arquitetura de Software de um Microprocessador

O conhecimento da arquitetura de software de um microprocessador permite o desenvolvimento de programas sem a necessidade de detalhes de implementao do chip. A arquitetura de software de um processador compreende:

a forma de organizao da memria e da E/S;

que tipos de registradores esto disponveis internamente e quais as suas funes;

que tipos de dados servem de operando;

quais os modos de endereamento existentes para se acessar um operando na memria, numa E/S ou num dos registradores internos; e

quais os comandos que constituem o seu conjunto de instrues.

4.1 Modelo de Software

O modelo de software inclui (Figura 22):

um espao contnuo e enderevel de 1 Mbyte de memria (20 bits do barramento de endereos);

um espao para endereamento de portas de E/S de 64 kbytes (16 bits do barramento de endereos); e

uma estrutura com 14 registradores internos disponveis.

Figura 22 Modelo de software de um processador

4.2 Registradores

4.2.1 Registradores de Dados (Registradores de Uso Geral)

Os registradores de dados podem ser usados como:

4 registradores de 16 bits (AX, BX, CX e DX), para manipulao de words (16 bits); ou

8 registradores de 8 bits (AL, AH, BL, BH, CL, CH, DL e DH), para manipulao de bytes (8 bits).

A terminao L (low) ou H (high) define onde ser armazenado o byte de mais baixa ordem ou o de mais alta ordem de uma palavra de 16 bits.

Embora considerados de uso igualitrio pela maioria das instrues aritmticas, lgicas ou de transferncia de informao, os registradores de dados apresentam algumas caractersticas prprias que os diferenciam:

as instrues de multiplicao, diviso ou de transferncia de dados de uma E/S exigem o registrador AX como acumulador e, o registrador DX como registrador de dados auxiliar;

as instrues que usam forma de endereamento de memria mais complexa, exigem o registrador BX como registrador de base; e

as instrues que manipulam strings ou loops de contagem exigem o registrador CX como registrador de contagem.

4.2.2 Registradores de Segmento

Um programa executvel deve ser constitudo por mdulos de cdigo e de dados. Para suportar esta estrutura de programa modular, o processador aloca cada unidade lgica de um programa em regies especficas da memria denominadas de segmentos. Por razes de implementao fsica, cada um destes segmentos no poder exceder o limite de 64 kbytes.

Como apenas um pequeno nmero de mdulos de programa e dados so necessrios em um dado instante, este mecanismo, chamado de segmentao de memria, permite que os programas sejam executados rapidamente e tomem pouco espao na memria principal, alm de facilitar o desenvolvimento de programas e a sua manuteno.

Em qualquer instante, um programa em execuo s poder ter acesso a 4 segmentos:

um segmento de cdigo, onde ser alocado o mdulo executvel (instrues);

um segmento de dados, onde sero alocadas tabelas, mensagens, variveis ou constantes (dados) necessrias execuo do programa;

um segmento de pilha, onde sero manipulados principalmente os endereos de retorno de subrotinas e as variveis locais de mdulos de programa em execuo; e

um segmento extra de dados, onde sero alocadas tabelas, mensagens, variveis ou constantes no suportadas pelo segmento de dados.

Para identificar e apontar cada um destes segmentos na memria, o processador utiliza 4 registradores de 16 bits:

CS como registrador de segmento de cdigo;

DS como registrador de segmento de dados;

SS como registrador de segmento de pilha; e

ES como registrador de segmento extra de dados.

A alocao fsica de um segmento pode se apresentar totalmente dissociada, parcialmente sobreposta ou totalmente sobreposta. Na Figura 23, por exemplo, o segmento de pilha est parcialmente sobreposto ao segmento de cdigo, o segmento de cdigo est totalmente dissociado do segmento de dados e o segmento extra de dados est totalmente sobreposto ao segmento de dados.

Figura 23 Segmentos parcialmente sobrepostos, totalmente dissociados e totalmente sobrepostos

Gerao de Endereo Fsico em Segmentos

Para poder gerar o endereo fsico de memria correspondente ao incio de um segmento de cdigo, de dados, de pilha ou de dados extra, o processador busca o contedo do registrador de segmento CS, DS, SS ou ES (de 16 bits), e multiplica-o por 16 (quatro deslocamentos com zeros esquerda). Como resultado, tem-se uma quantidade da largura do barramento de endereos, ou seja, 20 bits. Isso significa que um segmento poder se localizar, no espao de 1 Mbyte, a partir de qualquer endereo mltiplo de 16.

Como o contedo de um registrador de segmento permite a definio apenas do endereo da base do segmento, a manipulao de um dado dentro do espao fsico ocupado por todo o segmento s ser completamente determinada (Figura 24) se for fornecido um deslocamento, que caracterize a distncia relativa do dado a esta base. A fonte para este deslocamento (offset) depende do tipo de referncia feita memria: poder ser o contedo do registrador de instruo (busca do cdigo de uma operao), ou do registrador de ndice (acesso a uma rea de memria de dados), ou de um registrador de base de pilha (acesso a uma rea de memria de pilha), ou ainda uma associao de um ndice e uma base. Esta definio possvel atravs da anlise dos modos de endereamento de memria do processador.

Figura 24 Endereo fsico

Formalmente, o endereo fsico (EF) de um determinado dado presente na memria estar perfeitamente definido se referenciado pelo contedo de um registrador de segmento e um deslocamento dentro do segmento, ou seja:

EF = registrador de segmento : deslocamento

(representao do endereo fsico)

EF = registrador de segmento ( 16 + deslocamento

(valor do endereo fsico)

Exemplo:

Se o contedo em CS 0200h e o contedo em IP 0450h, a prxima instruo a ser buscada estar no endereo

EF = CS ( 16 + IP = 0200 ( 16 + 0450 = 02000 + 0450 = 02450h

+02000

0450Base

Deslocamento

02450Endereo Fsico

representado por 0200h : 0450h (CS : IP).

Logo, 0200h : 0450h a representao para o endereo fsico 02450h, dentro do segmento de cdigo.

4.2.3 Registradores Ponteiros e de ndice (Registradores de Deslocamento)

Os registradores ponteiros e de ndice so usados para armazenar valores de deslocamento no acesso a instrues (IP) ou no acesso a certas posies da memria pilha (SP e BP), ou ainda, na manipulao de dados ou de blocos de dados tipo matrizes ou tabelas nos segmentos de dados (SI e DI). Especificamente tm-se:

IP como apontador de instruo no segmento de cdigo CS.

SP como ponteiro do topo do segmento de pilha corrente (SS);

BP como ponteiro de base do segmento de pilha (deslocamento);

SI como ndice fonte de estruturas de dados presentes em DS ou ES;

DI como ndice destino de estruturas de dados presentes em DS ou ES; e

No tratamento de transferncias de dados controladas pelos ponteiros de ndice, o SI normalmente especifica um ndice fonte no segmento DS, enquanto DI especifica um ndice destino no segmento ES.

4.2.4 Registrador de Flags

O registrador de flags (Figura 25) composto de 16 bits independentes, sendo que apenas 9 bits so utilizados como flags:

6 flags de estado (status flags): descrevem os resultados gerados por uma instruo;

3 flags de controle: controlam a operao do processador; e

Figura 25 Registrador de flagsFlags de Estado:

Os flags de estado, usados normalmente pelo programador como auxiliares na hora de uma tomada de deciso, so setados (1) ou resetados (0) aps a execuo de instrues aritmticas e lgicas, refletindo propriedades caractersticas do resultado.

Todos os flags de estado vo para o nvel lgico 1 para indicar uma ao correspondente ao seu nome.

Os flags de estado presentes no processador so:

ZF zero flag (flag zero): indica que o resultado de uma operao zero.

SF sign flag (flag de sinal): indica que o resultado de uma operao negativo.

OF overflow flag (flag de estouro): indica que o resultado de uma operao com nmeros sinalizados excede o limite de possvel de representao do operando destino.

CF carry flag (flag de carregamento): indica, em operaes com nmeros no sinalizados, que o resultado de uma operao no cabe no operando destino (transporte ou emprstimo em operaes aritmticas, ou bit expulso em deslocamento ou rotao);

AF auxiliar carry flag (flag de carregamento auxiliar): indica que um ajuste, aps uma operao com nmeros BCD, necessrio.

PF parity flag (flag de paridade): usado para indicar se o resultado de uma operao possui um nmero par de bits 1 (comunicaes de dados).

Flags de Controle:

O flags de controle controlam operaes do processador, modificando o comportamento de instrues que sero executadas.

Os flags de controle presentes no processador so:

DF direction flag (flag de direo): controla, nas instrues com string, se os registradores SI e DI tero seus contedos automaticamente incrementados (DF=0) ou decrementados (DF=1) ( acesso direto ou inverso a strings.

IF interrupt flag (flag de interrupo): mascara, com IF=0, pedidos de interrupo feitos atravs da entrada INTR do microprocessador.

TF trap flag: coloca, com TF=1, o processador no modo de operao passo a passo.

No modo de operao passo a passo, aps a execuo de cada instruo do programa, ocorre uma interrupo de passo nico a qual, aciona uma rotina de depurao. Quando o microprocessador executa a interrupo de passo nico, o TF=1 salvo na pilha e resetado para permitir a execuo normal da rotina de depurao. No retorno desta rotina, a condio TF=1 ser novamente reativada (Figura 26).

Figura 26 Modo de operao passo a passo

4.3 Pilha

A pilha de um processador uma rea de memria usada para guardar dados, normalmente valores presentes nos registradores, que, devido complexidade do programa, precisam ser alterados, mas que devem depois recuperar seu antigo valor. As instrues que fazem isso so, basicamente PUSH e POP.

Os usos mais comuns da pilha so:

para salvar endereos de retorno para instrues na chamada e nos retornos de subrotinas e ocorrncias de interrupes;

para salvar o contedo de registradores quando ocorre uma chamada a subrotina;

para passar informaes de uma rotina para outra; e

para armazenar, temporariamente, resultados durante operaes complexas.

No processador temos o registrador SS que contm o valor do segmento reservado para a pilha e o ponteiro SP que indica, dentro desse segmento, qual o offset do topo da pilha.

Aps a execuo de instrues que acessam dados na pilha, o registrador SP automaticamente alterado (decrementado na insero e incrementado na retirada), indicando o novo topo da pilha. SP assume, inicialmente o valor 0000h, quando nenhum dado est presente na pilha

O registrador BP indica um deslocamento qualquer dentro da pilha, entre os endereos da base e do topo da pilha. BP assume, inicialmente, o valor 0000h (offset 0000), apontando para a base do segmento, podendo receber atribuies durante a execuo do programa.

Todo acesso pilha feito em words, isto , no se pode acess-la para guardar apenas o contedo dos registradores AL ou CL, sendo necessrio guardar todo o AX ou o CX.

Uma caracterstica interessante e que deve ser notada que a pilha do processador tem sua base num endereo de memria alto dentro do segmento de pilha, crescendo em direo memria de endereo baixo (Figura 27).

Figura 27 Segmento de pilha4.4 Modos de Endereamento de Memria

Quando um processador executa uma instruo, ele realiza uma determinada funo sobre um ou dois dados. Estes dados, chamados de operandos, podem ser parte da instruo, podem residir em um registrador interno do processador, podem estar armazenados em um endereo de memria, ou podem estar presente em uma porta de E/S. Para acessar estas diferentes localizaes dos operandos, o processador apresenta sete modos de endereamento de dados: endereamento por registro, endereamento imediato, endereamento direto, endereamento indireto por registro, endereamento por base, endereamento indexado, e endereamento por base indexada. Em geral, as instrues Assembly utilizam dois operandos: um operando deve ser um registrador e o outro operando (dado imediato, offset ou registrador) identifica o modo de endereamento utilizado.

Devemos entender os modos de endereamento como as formas possveis de se manipular dados de/para a memria. Portanto, os casos no includos nos endereamentos apresentados devem ser entendidos como no possveis, uma vez que provocam erros de compilao.

Para entender as figuras que explicam os modos de endereamento, deve-se imaginar o comportamento adotado pelo processador para executar uma instruo. Os seguintes passos devem ser seguidos:

Busca da instruo na memria (segmento de cdigo): Gerao do endereo fsico correspondente instruo que ser executada (composio CS : IP). Decodificao da instruo: Transformao de Assembly para linguagem de mquina. Busca dos operandos para execuo da instruo: Quando o operando estiver localizado na memria (dado por um deslocamento), gerao do endereo fsico correspondente ao deslocamento do dado no segmento correspondente (DS, ES ou SS), atravs da composio registrador de segmento : deslocamento. Execuo da instruo: Verificao das modificaes em registradores e segmentos de memria. Algumas observaes quanto modificao em registradores devem ser feitas:

Os registradores de segmento (CS, DS, ES, SS) no modificam seu valor durante a execuo de um programa a menos que seja feito algum redirecionamento.

O ponteiro de instruo (IP), aponta sempre para a instruo corrente, sendo incrementado automaticamente aps a execuo de uma instruo. O IP, portanto, no deve receber atribuies num programa.

O registrador SP aponta sempre para o topo da pilha e seu valor alterado (incrementado ou decrementado) automaticamente aps a execuo de instrues para manipulao de pilha.

Os registradores AX, BX, CX, DX, SI, DI e BP podem receber atribuies e, dessa forma, ter seus valores alterados.

O registrador de flags (F) pode ser alterado a partir de atribuies (atravs das instrues para manipulao de flags) ou depois da execuo de alguma instruo (flags de estado).

Uma observao importante deve ser feita quanto utilizao de variveis. As variveis, largamente utilizadas por linguagens de alto nvel, nada mais so que simples representao de um deslocamento de memria. Dessa forma, todas as observaes feitas para os modos de endereamento que manipulam deslocamentos so vlidas para utilizao com variveis.

4.4.1 Modo de Endereamento por Registro

No modo de endereamento por registro, os dois operandos so registradores.

Outro operando: registrador.

Exemplo (Figura 28): MOV AX, BX

AX ( BX

Figura 28 Modo de Endereamento por Registro

4.4.2 Modo de Endereamento Imediato

No modo de endereamento imediato, um dos operandos est presente no byte seguinte ao cdigo da instruo (opcode). Se bytes de endereamento seguem o opcode, ento o dado a ser transferido de maneira imediata vir logo aps os bytes de endereamento.

Outro operando: nmero (dado imediato).

Exemplo (Figura 29): MOV AL, 17h

AL ( 17h

Figura 29 Modo de Endereamento Imediato

4.4.3 Modo de Endereamento Direto

O modo de endereamento direto feito somando-se os dois bytes seguintes ao opcode ao DS, para compor um novo endereo absoluto.

Outro operando: deslocamento dado por um nmero.

O deslocamento pode ser o nome de uma varivel, uma vez que uma varivel um rtulo de uma posio de memria de dados.

Exemplo (Figura 30): MOV BX, [1102h]

BX ( (DS : 1102h)

[ ] indica um deslocamento no segmento de dados (DS).

Para fazer o endereamento atravs de ES ou SS, o segmento deve ser especificado explicitamente. Por exemplo, MOV BX, (ES:1102h)

Figura 30 Modo de Endereamento Direto

4.4.4 Modo de Endereamento Indireto por Registro

Nesse modo de endereamento, qualquer registrador pode ser utilizado.

Outro operando: deslocamento dado por um registrador.

Exemplo (Figura 31): MOV AX, [BX]

AX ( (DS : BX)

BX aponta (ponteiro) para um dado no segmento de dados (DS).

[BX] contedo do endereo apontado por BX no segmento de dados.

Figura 31 Modo de Endereamento Indireto por Registro

4.4.5 Modo de Endereamento por Base

Utilizado no tratamento de vetores. Apenas os registradores BX ou BP (quando estiver usando a pilha) podem ser utilizados como base.

Os vetores so armazenados no segmento de dados de forma linear, de acordo com a ordem imposta pelos ndices correspondentes. Para referenciar um elemento vi ( v[i] de um vetor v formado por n elementos

v = {v0, v1, v2, ... , vn-1} ( {v[0], v[1], v[2], ... , v[n-1]}

o processador utiliza a noo de deslocamento, que depende no somente do ndice, mas tambm da quantidade de bytes de cada elemento. Dessa forma, cada elemento do vetor representado a partir do elemento inicial v[0] ( v+0 = v, adicionado de um deslocamento. A Figura 32 ilustra a o armazenamento e a representao de vetores com elementos de 1 byte na memria. De forma geral, para um vetor cujos elementos so de b bytes, o elemento i ser dado por: v[i] = v + i ( b.

Figura 32 Forma de armazenamento e representao de vetores na memriaOutro operando: deslocamento dado por um registrador (base) + nmero (deslocamento).

Exemplo (Figura 33): MOV CX, [BX+0102h]CX ( (DS : (BX+0102h))

[BX+0102h] = base (v) + deslocamento adicionaldeslocamento adicional = ndice ( quantidade de bytes

Figura 33 Modo de Endereamento por Base

Regras para Especificao de ndices:

As seguintes regras devem ser observadas para endereamento de dados:

os ndices podem estar em qualquer ordem;

nomes de registradores devem estar sempre entre colchetes [ ];

podem ser combinados nomes de registradores e nmeros (endereos constantes) em um nico par de colchetes [ ], desde que separados pelo sinal +; e

se o nmero vier antes do registrador, no necessrio usar o sinal +.

Notao mais recomendada: varivel [registrador de base] [registrador de ndice] + constante

Exemplos: A[BX][SI]+8 ( A[BX][SI+8] ( A[8+SI+BX] ( [A+SI+BX+8]

Matriz: A[BX][SI] ( [A+BX+SI]

Vetor: A[BX] ou A[SI] ( [BX+A] ou [A+SI] ( [BX+SI] (BX contm o endereo de A)4.4.6 Modo de Endereamento Direto Indexado

Esse modo de endereamento tambm usado para manipulao de vetores e feito utilizando-se os registradores SI ou DI como indexadores. Um deslocamento somado a um desses registradores.

Outro operando: deslocamento dado por um nmero (base) + um registrador de ponteiro de ndice (deslocamento adicional).

Exemplo (Figura 34): MOV DX, [0100h+SI]

DX ( (DS : 0100h+SI)

[0100h+SI] = base (v) + deslocamento adicional (ndice do elemento ( nmero de bytes)

Figura 34 Modo de Endereamento Indexado

4.4.7 Modo de Endereamento por Base Indexada

Utilizado para a manipulao de matrizes na forma Amxn. Usa BX ou BP (quando estiver usando a pilha) para indicar o nmero da linha, e SI ou DI para o nmero da coluna.

Outro operando: deslocamento dado por um nmero (base) + um registrador (nmero da linha) + um registador de ponteiro de ndice (nmero da coluna), ou, alternativamente, um registrador (base) + um nmero (nmero da linha) + um registador de ponteiro de ndice (nmero da coluna).

As matrizes, apesar de serem entendidas como dados bidimensionais, so armazenadas no segmento de dados de forma linear, linha a linha. Uma matriz A formada por m(n elementos, possui representao matemtica dada por

A = (

e representao computacional equivalente dada por

A =

ou, alternativamente,

A =

podendo ser representada por um vetor correspondente, composto por m sub-vetores na forma

A =

no qual cada sub-vetor A[i] possui n elementos.

Para referenciar um elemento Aij ( A[i][j] de uma matriz A formada por m(n elementos o processador utiliza, da mesma forma que para vetores, a noo de deslocamento. No caso de vetores, apenas um deslocamento adicional suficiente para caracterizar um elemento. Para matrizes, no entanto, dois deslocamento so necessrios: um para indicar o nmero da linha e outro para o nmero da coluna s quais o elemento pertence. Dessa forma, cada elemento da matriz representado a partir do elemento inicial a[0][0] ( A+0+0 =A, adicionado de dois deslocamentos (linha+coluna). A Figura 35 ilustra o armazenamento e a representao de matrizes com elementos de 1 byte na memria, bem como o vetor linear correspondente a esta representao.

De forma geral, para uma matriz cujos elementos so de b bytes, o elemento (i, j) ser dado por: a[i][j] = A + i ( n ( b + j ( b.

Figura 35 Forma de armazenamento e representao de matrizes na memria

Exemplo (Figura 36): MOV AH, [BX+0100h+SI]

AH ( (DS : (BX+0100h+SI))

[BX+0100h+SI] = linha ( bytes + base (A) + coluna ( bytes ( base (A) + linha ( bytes + coluna ( bytes

Figura 36 Modo de Endereamento por Base Indexada5 Programao em Linguagem Assembly

5.1 Segmentao e Estrutura de Programao (Programa Bsico)

As declaraes de um programa fonte escrito em assembly (o que corresponde a cada linha de entrada) podem ser:

Comentrios;

Instrues assembly (linguagem); ou

Diretivas do assembler (montador).

Os comentrios permitem que explicaes sobre determinadas linhas de programa sejam realizadas sem ocasionar erro de compilao. As instrues assembly indicam as ordens que devem ser executadas pela CPU e so transcries (ou notaes) simplificadas, que correspondem aos cdigos binrios das instrues de mquina. As diretivas do assembler (pseudo-operaes) so comandos especiais com o objetivo de facilitar a escrita de um programa sob forma simblica. No so incorporadas ao programa objeto (extenso .obj) e servem simplesmente como orientao para o montador. Tanto as instrues assembly quanto as diretivas do assembler podem incluir operadores. Os operadores do ao assembler informaes adicionais acerca dos operandos, nos locais onde possam existir ambigidades.

Apesar das declaraes poderem ser escritas comeando em qualquer posio na linha, a Figura 37 ilustra a conveno de alinhamento mais utilizada.

Figura 37 Conveno para alinhamento de declaraes

As instrues e diretivas de um programa Assembly podem ser escritas em maisculas ou minsculas (Assembly uma linguagem no case-sensitive); entretanto, as seguintes sugestes so dadas de forma a tornar o programa mais legvel:

palavras reservadas (instrues e diretivas) devem ser escritas em letras maisculas; e

nomes em geral (comentrios e variveis) podem ser utilizadas letras minsculas ou maisculas, dando-se preferncia s minsculas.

5.1.1 Sintaxe dos Comentrios

Os comentrios podem ser utilizados de trs formas diferentes:

como uma linha em branco;

como uma linha iniciada com o caractere ponto e vrgula (;) e seguida de texto; ou

depois de uma instruo, bastando adicionar o caractere (;) para delimitar o incio do comentrio.

Exemplos de comentrios:

; comentario como uma linha iniciada com ponto e virgula

MOV AX, 1234H ; comentario depois de uma instrucao

5.1.2 Sintaxe das Instrues e Diretivas do Assembly

Para os montadores MASM (Macro ASseMbler) e TASM (Turbo ASseMbler), as instrues devem ser escrita, obrigatoriamente, uma por linha, podendo ter at quatro campos, delimitados de acordo com a seguinte ordem:

[label:]mneumnico [operando(s)]

[; comentrio]onde label o rtulo dado ao endereo da instruo (no segmento de cdigo), mneumnico representa a instruo, operandos so os dados operados pela instruo e comentrio qualquer texto escrito para elucidar ao leitor do programa o procedimento ou objetivo da instruo. Destes, apenas o campo mneumnico sempre obrigatrio. O campo operandos depende da instruo includa na linha e os campos label e comentrio so sempre opcionais. Todos os valores numricos esto, por default, em base decimal, a menos que outra base seja especificada.

5.1.3 Modelo de Programa Assembler Simplificado (.EXE)

;

definio do modelo desejado

; ****************************************************************************

DOSSEG

.MODEL modelo

;

definio da base numrica desejada

; ****************************************************************************

[.RADIXbase]

;

definio do segmento de pilha

; ****************************************************************************

.STACK [tamanho]

;

rea de definio de equivalncias

; ****************************************************************************

; equivalncias

;

criao do segmento de dados

; ****************************************************************************

.DATA

; variveis

;

incio do segmento de cdigo

; ****************************************************************************

.CODE

;

procedimento principal

; ****************************************************************************

Principal PROC NEAR ; incio do procedimento principal MOV AX, @DATA ; instrues para que DS e ES

MOV DS, AX ; apontem para a rea de

MOV ES, AX ; dados criada

; corpo do programa principal

MOV AH, 4Ch ; funo para trmino de programa

INT 21h ; atravs da INT 21hPrincipal ENDP ; final do procedimento principal END Principal ; final do programa

Observao: Quando um programa carregado, os registradores de dados DS e ES no vm apontando para os segmentos de dados, devendo ser implementado atravs das instrues (primeira linha do cdigo do programa principal):

MOV AX, @DATA

; copia para AX o endereo da rea de dados

MOV DS, AX

; faz DS apontar para a rea de dados

MOV ES, AX

; faz ES apontar para a rea de dados

5.1.4 Diretivas Simplificadas de Definio de Segmentos