Circuitos lógicos

-

Upload

carlos-mateus -

Category

Documents

-

view

28 -

download

1

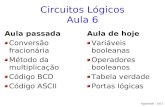

Transcript of Circuitos lógicos

Disciplina: SISTEMAS DIGITAIS

Curso Profissional de Eletrnica, Automao e Comando

Sistemas Digitais 10. ano

Mdulo 2 - Circuitos Lgicos

Rui Marques/2013

SISTEMAS DIGITAISsd10peac_Circuitos lgicos

LGEBRA DE BOOLE E CIRCUITOS LGICOS Os circuitos lgicos digitais operam de modo que, quer as entradas quer as sadas apenas assumem valores 0 ou 1. A cada um destes valores correspondem gamas de tenses predefinidas, de que se representa um exemplo.

Figura 1 - Valores tpicos de tenso num sistema digital, para a famlia TTLNeste exemplo, ao nvel de tenso entre 0 e 0,8 V (nvel lgico baixo) corresponde o valor lgico 0.Ao nvel de tenso entre 2 e 5 V (nvel lgico alto) corresponde o valor lgico 1.Isto quer dizer que o circuito digital responde da mesma maneira a todas as tenses que se encontrem dentro de cada uma das zonas referenciadas.De 0,8 V a 2 V, o nvel lgico indeterminado. Esta zona no deve ser usada.So estas caractersticas dos circuitos lgicos que permitem a utilizao da lgebra de Boole para a anlise dos sistemas digitais.CONSTANTES E VARIVEIS DE BOOLE Na lgebra de Boole, tanto as constantes como as variveis apenas podem tomar dois valores possveis: 0 e 1. As variveis de Boole so usadas para representar nveis de tenso presentes entrada/sada de um circuito, ou num fio condutor. No exemplo, o valor 0 designa qualquer tenso entre 0 V e 0,8 V, enquanto o valor 1 pode designar qualquer tenso da gama 2 V a 5 V. Deste modo, os valores de Boole 0 e 1 no representam nmeros, mas o estado de uma varivel, que designamos por nvel lgico. Num circuito digital diz-se que a tenso est no nvel lgico 0 ou no nvel lgico 1, conforme o valor numrico que assume. vulgar surgirem outras nomenclaturas para designar 0 e 1, de onde destacamos Baixo/Alto (Low/High).Porque apenas so possveis dois valores, a lgebra de Boole bastante mais simples que a clssica, pois no existem fraes, decimais, nmeros negativos, razes quadradas e cbicas, logaritmos, etc. Na lgebra de Boole apenas existem 3 operaes bsicas:entradassada

CBAF

000?

001?

010?

011?

100?

101?

110?

111?

Adio lgica (+), adio OU (OR) ou operao OU (OR) Multiplicao lgica (), multiplicao E (AND) ou operao E (AND) Complementao ( ), inverso lgica, negao ou operao NO (NOT).TABELAS DE VERDADEMuitos circuitos tm mais que uma entrada e apenas uma sada. A sada de um circuito lgico o seu estado.Uma tabela de verdade mostra como a sada do circuito varia com as diversas combinaes lgicas dos nveis nas entradas. As possveis combinaes das entradas so listadas no lado esquerdo e o correspondente valor lgico surgir direita, como se ilustra para o caso de 3 variveis C, B, e A.

Figura 2OPERAO OU (OR)F = A + B (soma lgica)O resultado de uma operao OR 1 se pelo menos uma das variveis de entrada for 1.

ABFCircuito eltrico equivalente

Interruptor aberto: 0Interruptor fechado: 1Lmpada apagada: 0Lmpada acesa: 1

F 1 ( a lmpada acende) se A OU B for 1 (se o interruptor A ou o interruptor B estiver fechado).As duas variveis so representadas pelas letras A e B. Quando se combinam A e B atravs da operao OR, o resultado pode expressar-se por: F = B + A Na expresso o sinal + no significa a clssica adio, mas representa a operao OR, cujas regras se representam na tabela de verdade, de onde se constata que, exceo de A = B = 1, a operao OR a mesma que a operao de adio vulgar. No caso de A = B = 1, o resultado da operao OR 1 (e no dois como na adio vulgar). Torna-se fcil de lembrar que o maior valor que se pode obter de uma operao OR 1. O mesmo resultado se obteria se tivssemos 3 entradas C, B e A.Teramos com A = B = C =1F=1+1+1=1Podemos referir que:O resultado de uma operao OR 1 se uma ou mais das variveis de entrada for 1.Smbolos lgicosOs smbolos lgicos dos circuitos que implementam estas operaes sofreram alteraes em 1984 passando a ser representadas de acordo com a norma IEEE/ANSI Standard 91. No entanto, as anteriores ainda se mantm em muitas publicaes, pelo que sero apresentadas ambas as normas que designaremos por antigas (anteriores a 1984) e modernas

BAF = B + A

000

011

101

111

1

Figura 3 - Tabela de verdade da operao OR e smbolos antigo e moderno, respetivamente, para uma OR de duas entradas

GATE OR A gate (porta) OR opera de modo que a sua sada ser High (Alta, nvel lgico 1 ) se ou a entrada B ou a A ou ambas estiverem no nvel lgico 1. A sada da porta OR apenas ser Low (Baixa, nvel lgico 0) se todas as entradas estiverem no nvel lgico 0. No mercado, estas gates esto disponveis nos circuitos integrados: 7432 qudrupla OR de duas entradas (famlia TTL) 74802tripla OR/NOR de 4 entradas (famlia TTL) 4071 qudrupla OR de duas entradas (famlia CMOS) 4072 dupla OR de quatro entradas (famlia CMOS) 4075tripla OR de trs entradas (famlia CMOS)

1 Figura 4 - Smbolos e configurao dos pinos (pin-out) de um 7432Exerccio:Determinar a sada da gate OR, quando as entradas variam de acordo com os diagramas temporais representados. Figura 5Resoluo: Como se representa, a sada da porta OR vai para o estado Alto, cada vez que qualquer das entradas esteja Alta. Quando A vai para o estado alto, em t , a sada fica no estado Alto, a permanecendo at ao instante t4, altura em que fica no nvel Baixo, pois ambas as entradas esto nesse estado. Note-se que as variaes em t2 e em t3 no afetam a sada, pois uma das entradas permanece Alta.Exerccio:Complete o diagrama temporal seguinte, em que A e B so entradas de uma porta OR com sada F:

ABF

OPERAO E (AND)F = B A (multiplicao lgica)Na expresso, o smbolo representa a operao da multiplicao AND.O resultado de uma operao AND 1 se todas as variveis de entrada forem 1.Circuito eltrico equivalente

ABFInterruptor aberto: 0Interruptor fechado: 1Lmpada apagada: 0Lmpada acesa: 1

F 1 ( a lmpada acende) se A E B for 1 (se o interruptor A e o interruptor B estiverem fechados).As duas variveis so representadas pelas letras A e B. Quando se combinam A e B atravs da operao AND, cujas regras se representam na tabela de verdade.Podemos constatar que a tabela da multiplicao AND exatamente idntica clssica multiplicao. Sempre que A ou B zero, o produto tambm ser zero. Quando A e B so 1 ento o produto tambm ser 1. Podemos indicar que na operao AND o resultado ser 1 se e s se todas as entradas forem 1. Nos casos restantes ser 0.BAF=B.A

000

010

100

111

&

Figura 6 - Tabela de verdade da operao AND e smbolos para uma AND de duas entradasO sinal da multiplicao geralmente omitido pelo que a sua expresso se torna F=BA. Para a operao AND devemos recordar-nos que ela idntica vulgar multiplicao sendo as variveis 0 e 1.GATE AND A gate (porta) AND opera de modo que a sua sada ser High (Alta, nvel lgico 1 ) se e s se todas as entradas forem altas. As gates AND de 2 entradas apresentam-se no mercado no C.I. 7408, do qual representamos o respetivo pin-out.

&Figura 7 - Smbolos e Pin-out do 7408 - qudrupla AND de 2 entradasA mesma operao ocorrer para AND com mais de duas entradas. Por exemplo para a AND de trs entradas a expresso de sada ser F = CBA e para 4 entradas a expresso ser F = DCBA.Em tecnologia TTL surgem os C.I: 7411 tripla AND de 3 entradas7421 dupla AND de 4 entradas, de que se representa os respetivos smbolo lgico, o pin-out e tabela de verdade. (X quer dizer indiferente, podendo a entrada assumir quer o valor alto = H quer o baixo = L.)Em tecnologia CMOS existem: 4081 - qudrupla AND de 2 entradas, 4073 - tripla AND de 3 entradas e4082 - dupla porta AND de 4 entradas.

Figura 8 - 7421: smbolo lgico, o pin-out e tabela de verdade. (X quer dizer indiferente, podendo a entrada assumir quer o valor alto = H quer o baixo = L.)Exerccio:Determinar a sada F da gate AND para as ondas de entrada representadas.Resoluo:

Nos intervalos t2 - t3 e em t6 - t7, tanto B como A esto em nvel alto pelo que alta a respetiva sada.Note-se que as variaes de nvel numa entrada, quando a outra se encontra a zero, no produzem qualquer efeito na sada.

Exerccio:Determinar a forma de onda F da sada da gate AND representada

Resoluo: A sada F 1 desde que tanto B como A o sejam. Note-se que quando B est a 0, a sada 0 independentemente de A. Quando B est a 1 a onda de sada igual a A.Assim a entrada A assume funes de controlo, determinando quando deve ou no a entrada A atingir a sada.A entrada B funciona como ENABLE (permisso). Quando B =1, a condio de enable conseguida, pelo que A vai para a sada; na situao em que B = 0, a gate ser INIBIDA, e a sada ser 0.Voltaremos a este assunto mais tarde.OPERAO NO (NOT)Trata-se agora, ao contrrio das operaes OR e AND, de uma operao com uma nica varivel de entrada. Assim se a sua entrada for A a respetiva sada ser:F = onde a barra superior representa a operao NOT.Esta expresso l-se: "F igual a no A" ou "F igual ao inverso de A" ou "F igual ao complemento de A".A operao NOT tambm designada por inverso ou complementao, pelo que poderemos utilizar estes termos equivalentes, ao longo do texto, de forma indistinta.Alguns autores usam o smbolo "/" para representarem a inverso, resultando ento /A = A, mas no iremos usar essa notao.

Interruptor aberto: 0Interruptor fechado: 1Lmpada apagada: 0Lmpada acesa: 1Circuito eltrico equivalente

AF

F 1 ( a lmpada acende) se A for 0 (se o interruptor A estiver aberto).

1A presena de um pequeno tringulo representa sempre a inversoGATE NOT (INVERSOR)AF = A

01

a)10

Figura 9 - a) Tabela de verdade; b) Smbolos do circuito NOT; c) Formas de onda

Em circuito integrado o inversor surge no 7404 em tecnologia TTL, e nos 4009, 4049 e 4069 em CMOS, que contm seis gates, como se verifica:Figura 10 4049 4069 Podemos resumir as operaes OR, AND e NOT como se indica:

OR AND NOT 0+0=0 0.0=0 0=1 0+1=1 0.0=0 1=0 1+0=1 1.0=0 1+1 =1 1.1=1

Qualquer circuito lgico, por mais complexo que seja, poder ser realizado com gates OR, AND e NOT. PORTAS NAND E NORPORTA NANDConsiste na combinao de uma porta AND e de uma NOT. O seu smbolo idntico ao da AND, acrescido do pequeno crculo de sada, que indica a inverso. A NAND ento anloga a uma AND seguida de um INVERSOR. A expresso da sada ser

BA

001

011

101

1d)10

&

c)c)

Figura 11 - a) Smbolo da NAND; b) Circuito equivalente; c) Smbolo moderno; d) Tabela de verdadeDa tabela constata-se que a sada da NAND fica no estado Baixo s quando todas as entradas forem Altas.

As gates NAND apresentam-se em C.I., sendo: TTL CMOS 7400 4011 qudrupla NAND de 2 entradas 7410 4023 tripla NAND de 3 entradas 7420 4012 dupla NAND de 4 entradas 7430 4068 NAND de 8 entradas 74133 NAND de 13 entradasApresentamos o pin-out de alguns destes C.I. PORTA NOR O smbolo de uma gate NOR de duas entradas representa-se na figura seguinte. Trata--se dum smbolo anlogo gate OR, seguido de um pequeno crculo que representa a inverso. A expresso da sada ser:

BA

001

010

100

110

A sada apenas assume o nvel Alto quando as entradas esto no nvel baixo. Se qualquer das entradas ficar Alta, a sada da NOR ficar no nvel baixo.

1

c)

d)

Figura 12 - a) Smbolo da NAND; b) Circuito equivalente; c) Smbolo moderno; d) Tabela de verdadeOs circuitos integrados que contm gates NOR, e dos quais representamos os de tecnologia TTL, so: TTL CMOS 7402 4001 qudrupla NOR de 2 entradas 7427 4025 tripla NOR de 3 entradas 7425 4002 dupla NOR de 4 entradas 74260 ----- dupla NOR de 5 entradas ----- 4078 porta NOR de 8 entradas

PORTAS EXCLUSIVE-OR E EXCLUSIVE-NORPORTA EXCLUSIVE-OREsta operao representada pelo smbolo , realizada com apenas duas entradas, no existindo portas com 3, 4 ou mais entradas.

=1A expresso da sua sada ser

Figura 13 - Porta EX-OR: a) Circuito; b) Tabela de verdade; c) Smbolos moderno e antigoDa tabela de verdade conclui-se que a sada 1 se uma entrada 1, ou a outra, mas no ambas. Doutro modo: a sada ALTA sempre que as duas entradas so diferentes. Tanto da tabela de verdade como do circuito a) poderemos constatar que:1. S tem duas entradas e a sua sada

2. A sada F ALTA sempre que os nveis das entradas so diferentes. H portas EX-OR (XOR) em diversos circuitos integrados: 7486 qudrupla EX-OR (Famlia TTL) . 74C86 qudrupla EX-OR (Famlia CMOS) 4070 qudrupla EX-OR (Famlia CMOS) 74HC86 qudrupla EX-OR (Famlia CMOS alta velocidade) Exerccio:Determinar a onda de sada para as entradas representadas.

Resoluo: A resoluo deste exemplo revela os seguintes pontos: 1. A sada acompanha a entrada A sempre que a outra entrada B se encontra a 0. 2. Na sada surge a onda A invertida, quando a entrada B =1, o que sucede entre t1 e t2. 3. Conclui-se que a porta EX-OR um INVERSOR CONTROLADO; uma das entradas pode ser utilizada para fazer com que o sinal presente na outra entrada surja na sada invertido ou no.EXCLUSIVE-NOREste circuito, abreviadamente EX-NOR, realiza uma operao oposta ao EX-OR. Da tabela de verdade, conclui-se que a expresso da sada ser F=BA+BA, indicando que a sada ser ALTA sempre que as duas entradas tm o mesmo nvel.Esta porta tambm apenas dispe de duas entradas, sendo bvio que a respetiva sada o inverso da porta EX-OR e a sua expresso ser:BAF=

001

010

100

1b)11

F= ouF=B A

=1=1

d)

Figura 14- Porta EX-NOR: a) circuito; b) Tabela de verdade; c) Smbolo antigo; d) Smbolo modernoEm resumo, a porta EX-NOR caracteriza-se por: 1. S ter duas entradas e a sua sada ser 2. A sada F ALTA sempre que os nveis das entradas so iguais.

Os circuitos integrados seguintes contm portas EX-NOR:74L5266 qudrupla EX-NOR (Famlia TTL)74C266 qudrupla EX-NOR (Famlia CMOS)4077 qudrupla EX-NOR (Famlia CMOS)74HC266 qudrupla EX-NOR (Famlia CMOS de alta velocidade)

SMBOLOS LGICOS IEEE/ANSI

Figura 15Os smbolos que fomos utilizando tm sido aplicados pela indstria h muitos anos. No que respeita s portas lgicas bsicas, esses smbolos funcionam adequadamente. No entanto, para circuitos mais complexos, tais como flip-flops, contadores, descodificadores, multiplexeres, memrias e microprocessadores, os smbolos clssicos no fornecem a informao adequada.Para promover mais informao, o American National Standards Institute (ANSI) e o Institute of Electrical and Electronic Engineers (IEEE) desenvolveram conjuntamente uma reviso que designaram por Standard IEEE / ANSI 91-1984.Estes novos smbolos comeam a ser cada vez mais vulgarizados, mesmo na literatura da especialidade.A principal diferena dos novos smbolos reside na utilizao de formas retangulares em vez das formas clssicas.Vejamos as diferenas entre as duas simbologias:1. A nova simbologia usa um pequeno tringulo ( ) em vez do crculo. Este tringulo representa de igual modo uma inverso do nvel lgico. A existncia ou no deste smbolo se a entrada ou sada ativa baixa ou ativa alta.2. Um smbolo especial dentro de cada retngulo indica qual a relao entre as entradas e a sada.O smbolo 1 dentro do inversor indica que apenas existe uma entrada ativa. A entrada ativa alta e a sada ativa baixa.O smbolo & significa a funo ou gate AND.O smbolo 1, representando a gate OR, foi assim escolhido para indicar que necessrio uma ou mais entradas ativas para que a sada seja ativada.O smbolo = 1, representando a porta EX-OR, refere que se torna necessria uma e uma s entrada ativa para ativar a sada.

Figura 16O smbolo identifica um buffer ou um elemento com maior capacidade de sada que a usual (a orientao do smbolo feita no sentido do fluxo do sinal). O buffer no altera o nvel lgico da entrada.Para se representarem pela nova simbologia a totalidade dos circuitos integrados, cada porta lgica representada por um retngulo. O smbolo representativo da operao apenas inscrito no bloco inicial, entendendo-se que tal se aplica aos restantes blocos. Elucidamos o que se descreveu com o 7400 (Figura 16 a) 4 portas AND) e 7404 (Figura 16 b) 6 portas NOT).

A concluir este captulo apresenta-se um sumrio das funes e respetiva simbologia.Apresenta-se tambm o smbolo para o buffer, que consiste num tringulo sem inverso. O buffer no muda o nvel lgico da entrada; trata-se de um circuito capaz de fornecer uma corrente de sada superior normal. , pois, um amplificador de corrente.

ANLISE DE CIRCUITOS COMBINATRIOSQualquer circuito lgico por mais complexo que seja poder ser realizado com gates OR, AND e NOT.Assim e considerando o simples exemplo da figura seguinte, facilmente obtemos a expresso de Boole da sada. A expresso da sada da gate AND B.A. Esta ligada a uma entrada de uma porta OR, sendo C a outra entrada.A expresso de sada da OR F = B.A + C. Esta expresso pode ser escrita na formaF = C + B.A.Figura 17 - Circuito lgico e expresso booleana da sada Pode haver confuso de qual a operao que se realiza em primeiro lugar, podendo a mesma expresso ser interpretada de dois diferentes modos. Pode entender-se como sendo uma operao OR entre C e B. A, ou uma operao AND entre C + B e A. Para evitar esta confuso realamos que, se numa expresso surgirem ANDs e ORs, considera-se que se realiza em primeiro lugar a operao AND, a no ser que haja parntesis na expresso, o que dar prioridade operao que esteja no seu interior. Deste modo e num circuito anlogo ao anterior, verifique-se a utilizao do parntesis.

Figura 18 - Circuito lgico cuja expresso booleana da sada requer parntesis Sempre que surjam INVERSORES no circuito lgico, a expresso da sada ser idntica da entrada, acrescida de uma barra sobre ela.Figura 19Apresentam-se ainda dois outros circuitos, realando-se a necessidade da utilizao de parntesis retos.

Figura 20

SNTESE DE CIRCUITOS LGICOS COMBINATRIOSTrata-se agora de representar logigramas a partir de expresses lgicas.Seja, por exemplo a expresso Em primeiro lugar deveremos representar as operaes AND e depois as OR.

FABC&

1

Suponhamos agora que uma funo F de 3 variveis (C, B e A) definida, atravs da sua tabela de verdade, do seguinte modo:CBAF

0000

0010

0100

0111

1001

1010

1100

1111

Veremos mais adiante que, a partir da tabela de verdade se pode obter a expresso booleana desta funo:

Figura 21&1&&ABCFPodemos agora, a partir desta expresso booleana, desenhar o respetivo diagrama lgico ou logigrama. Como as variveis de entrada aparecem negadas e no negadas, podemos desenhar o logigrama desta forma:

No entanto, pode pr-se a questo: ser esta a expresso mais simples de F?, ou ser este o circuito que mais economicamente o realiza?No captulo seguinte vamos estudar as formas de simplificar funes booleanas.

lgebra de BoolePostulados e teoremas da lgebra de BooleVrios postulados e teoremas da lgebra de Boole podem ser usados para simplificar expresses e circuitos lgicos.Vejamos cada um dos teoremas acompanhados de circuitos lgicos que comprovam a sua validadeTeoremas de uma varivelA + 1 = 1A1

A + 0 = AA0

A + A = AAA

A

Princpio da dualidadeQualquer teorema ou identidade em lgebra de Boole permanece vlido se trocarmos entre si 0s por 1s e + por Com este princpio possvel escrever um teorema a partir de outro.

Teoremas duais dos quatro apresentados

A 0 = 0A0

A 1 = AA1

A A = AAA

A

Dupla negao

Teoremas de duas ou mais variveisPropriedade comutativa

dual: Propriedade associativaA + (B + C) = (A + B ) + C =A + B + Cdual: A (B C) = (A B ) C =A B C

Propriedade distributivaA (B + C) = (A B) + (A C)dual: A + (B C) = (A + B) (A + C)Regras da absoro1. regra da absoroA + (A B) = Adual: A (A + B) = ADemonstraoSendo A = 1, 1+ (1 B) = 1: o primeiro membro da equao 1 e o segundo tambm 1.Sendo A = 0; A B = 0; 0 + 0 = 0: o primeiro membro da equao 0 e o segundo tambm 0.A regra tambm pode demonstrar-se da seguinte maneira:A + (A B) = A + AB = A (1+B) = A 1 =AComprovao pela tabela de verdadeABA BA + A B

0000

0100

1001

1111

A + A B = AComprovao pelo circuito de contactos

AAB

Qualquer que seja B, quando A 1, a sada 1, quando A 0, a sada 0.A regra dual comprovada de modo idntico.

2. regra da absoro

dual: Demonstrao

Comprovao pela tabela de verdadeAB

001000

011111

100011

110011

Comprovao pelo circuito de contactos

AB

Quando A 1 ou B 1, a sada 1. A regra dual comprovada de modo idntico.

3. regra da absoro

dual: Demonstrao

Comprovao pela tabela de verdadeAB

001000

010000

101011

110101

BAAComprovao pelo circuito de contactos

Quando A 0, a sada sempre 0. Quando A 1 e B 0, a corrente passa pelo ramo de baixo.Quando A 1 e B 1, a corrente passa pelo ramo de cima, logo, quando A 1, a sada sempre 1.A regra dual comprovada de modo idntico.Generalizao da 3. regra da absoroSe dois ou mais termos se combinam numa multiplicao ou numa soma, e se as variveis que esto dentro de um parntesis diferem das que esto dentro de outro apenas porque uma delas est negada num caso e no negada no outro, essa varivel pode omitir-se por completo.

Exemplos:

Nota: para simplificar a representao, num termo produto podem-se omitir os parntesis. Tambm o smbolo da multiplicao () pode ser omitido. Assim, a expresso do primeiro exemplo pode tambm ser escrita nesta forma:

Exerccios:Simplificar a expresso ResoluoPela regra da absoro generalizada, teremos:

Simplificar a expresso ResoluoPondo em evidncia o termo comum DC, teremos:

Como , vem .Simplificar a expresso ResoluoDesenvolvendo a expresso de F vir F= 0+ C A; F=CASimplificar a expresso Resoluo;;;Teoremas de De MorganSo dois importantes teoremas utilizveis na simplificao de expresses: A negao de uma soma de duas variveis igual ao produto das mesmas variveis negadas:

O complemento de um produto de duas variveis idntico soma das mesmas variveis, mas complementadas:

Apesar de termos enunciado estes teoremas para duas variveis, ele extensivo a expresses que contenham mais que duas variveis. Assim:

Se tratarmos AB como um produto vir:

Exemplo:Simplificar a expresso Resoluo

Consequncias dos teoremas de De MorganPela anlise do teorema poderemos constatar que o 1. membro da equao a sada de uma porta NOR, com entradas B e A. O 2. membro da equao consiste numa AND cujas entradas so previamente invertidas. Estas duas representaes so equivalentes.

Vejamos agora o teorema . O 1. membro da equao pode ser implementado por uma porta NAND com entradas B e A.O 2. membro pode ser implementado por uma porta OR com as entradas B e A previamente invertidas. Em alternativa poderemos ter uma porta OR com dois inversores em cada uma das entradas.

Exemplo:Implementar a funo utilizando portas NAND e NOT. ResoluoFaremos uma dupla inverso ao 2. membro, o que no altera o seu valor lgico.

pelo teorema de De MorganUniversalidade das portas NAND e NORComo j referimos, todas as funes booleanas podem ser realizadas pela conjugao das funes OR, AND e NOT. possvel, contudo, implementar qualquer expresso lgica usando apenas gates NAND.Com uma porta NAND, cujas entradas se encontram ligadas entre si, passa a atuar como inversor, sendo a sada Para se obter uma porta AND, mais no preciso que ligar sada de uma NAND uma outra porta NAND a funcionar como inversor, resultando a operao AND, pois, invertendo , obteremos , que uma funo AND.Para se realizar a operao OR, usando apenas portas NAND, basta utilizarmos o teorema de De Morgan, pelo que se usam duas NAND como inversores para negar as entradas de uma terceira NAND, pois

Figura 22Efetuando um raciocnio anlogo, obtemos as implementaes seguintes utilizando portas NOR. Para uma porta NOT, ligam-se as entradas da NOR, pois .Com duas NOR obtm-se a operao OR, efetuando a segunda porta a funo de inversor, pois, invertendo , teremos .Recorrendo ao teorema de De Morgan, -nos permitido encontrar a representao da funo AND, sendo necessrias trs NOR, duas das quais a funcionar como inversores, pois

Figura 23Exemplo:Implementar a funo F = DC + BA utilizando o nmero mnimo de CI. ResoluoA implementao direta conduz utilizao de 2 CI: um 7408 que contm 4 portas AND e um 7432 que contm 4 portas OR. Resulta:

Figura 24Por aplicao do teorema de De Morgan obteremos DC + BA= DC BA , a que corresponde a implementao seguinte, que apenas utiliza um nico circuito integrado, o 7400, de que se utilizaro 3/4.

Figura 25Exemplo:Implementar a funo F = utilizando apenas portas NAND de 2 entradas. ResoluoVamos utilizar dois mtodos:1 mtodoImplementamos diretamente a funo:

Figura 26Agora, e utilizando para as portas NOT a notao /, vamos negar duas vezes as entradas das portas OR e as sadas das AND.Redesenhamos o circuito, utilizando agora apenas portas lgicas NAND.

Figura 272 mtodoVamos colocando duplas negaes de modo a transformar a expresso da funo na forma de produtos de duas variveis complementados. Assim:

Implementamos a expresso assim obtida, que se pode constatar reproduziria aFigura 27.Representao alternativa das portas lgicasEmbora um grande nmero de circuitos lgicos ainda use exclusivamente os smbolos standard, existe um acrscimo de utilizao conjunta dos smbolos alternativos.Os smbolos alternativos so obtidos a partir dos standard, bastando, para isso:

Figura 281. Inverter as entradas e a sada do smbolo standard. Na prtica, tal obtido colocando pequenos crculos onde estes no existem e retirando-os se a j se encontrarem.2. Trocar o smbolo da operao de AND para OR ou de OR para AND. No caso do inversor o smbolo da operao no ser alterado.A validade destes smbolos alternativos ser facilmente comprovada pela aplicao dos teoremas de De Morgan.Destas equivalncias podemos constatar que:1. As equivalncias so vlidas para portas com qualquer nmero de entradas.2. Nenhum dos smbolos standard tem negaes nas entradas e todos os alternativos as tm.3. Para cada situao, os dois smbolos representam o mesmo circuito fsico.4. Nas portas NAND e NOR, tanto os smbolos standard como os alternativos possuem inverses, ou nas entradas ou na sada. Nas portas AND e OR, os smbolos alternativos possuem inverses tanto nas entradas como na sada.

Interpretao dos smbolos lgicosA interpretao destes smbolos lgicos alternativos facilmente obtida atravs do conceito de nveis lgicos ativos, que reafirmamos: se uma entrada ou sada no possui um crculo, diz-se que essa linha ativa alta; se uma entrada ou sada possui um crculo, diz-se que essa linha ativa baixa.Deste modo a interpretao do smbolo standard de uma porta NAND : A sada vai para o nvel baixo s quando todas as entradas so altas. Interpretando o smbolo alternativo da mesma porta NAND, teremos: A sada ser alta quando pelo menos uma das entradas for baixa.Usando a palavra todas para as entradas do smbolo AND e as palavras pelo menos uma para as entradas do smbolo OR, podemos descrever o funcionamento das portas, quer para os smbolos standard quer para os alternativos:

A utilizao destes smbolos alternativos promove uma mais fcil interpretao dos circuitos lgicos. Vejamos um exemplo.Exemplo:Pretende-se que a sada do circuito seja ativa alta. Promova as modificaes convenientes de modo a tornar mais evidente o respetivo funcionamento.ResoluoDeve obedecer-se ao princpio geral: sempre que possvel devem ligar-se sadas com inverso a entradas que contenham inverso e sadas no invertidas a entradas que tambm o no sejam.Deste modo, e representando a porta NOR pelo seu smbolo alternativo, obteremos o circuito representado na parte b1, de onde se conclui que a sada ser ativa quando as entradas C e D forem altas e as A e B forem baixas.Constate-se a dificuldade em obter esta concluso atravs da anlise do circuito original.

Figura 29

Simplificao de funes lgicas usando o mtodo grfico de KarnaughForma cannica de uma funo. Mintermos e maxtermosUsualmente, como ponto de partida do desenho de um circuito combinatrio, dispe-se de uma descrio do problema, que pode ser uma listagem das combinaes das entradas que colocam a sada a 1 ou a 0, ou de uma tabela de verdade ou ainda da expresso da funo na forma de Y - (somatrio) ou na forma de (produto), que passamos a descrever.Uma tabela de verdade para n variveis tem 2n linhas.Para n variveis, define-se mintermo como um produto das n variveis. H 2n mintermos.Para n variveis, um maxtermo ser uma soma das n variveis. H 2n maxtermos.Uma expresso booleana de n variveis est na forma cannica se tiver a forma de uma soma de produtos, todos com n variveis, ou seja, uma soma de mintermos; est ainda na forma cannica se tiver a forma de um produto de somas, todas elas contendo as n variveis, ou seja, um produto de maxtermos.Um mintermo de n variveis pode ser representado por um inteiro de n bits. Representaremos o mintermo por mi, sendo i a representao decimal do nmero do mintermo.Se, por exemplo, pretendermos representar a funo onde j colocamos os termos por ordem de numerao crescente, teremos:

000 011 100 110 111 0 3 4 6 7ou F(CBA) = mo + m3 + m4 + m6 + m7Refira-se que cada mintermo obtido atravs da representao binria do nmero, considerando-se C o bit de maior peso e A o de menor peso e representando-se logicamente cada varivel por 1 se no estiver negada e por 0 se o estiver. Assim, atendendo aos pesos respetivos, podemos elaborar a lista de mintermos:F (CBA) = m (0, 3, 4, 6, 7) F(CBA) = (0, 3, 4, 6, 7)Esta representao da funo a soma dos mintermos correspondentes s linhas da tabela de verdade, para as quais a funo assume o valor 1 na sada.Efetuando raciocnio anlogo para uma representao de maxtermos, teramos, por exemplo:

F(CBA) = M1 M2 M5 M6 M7ou ainda de forma mais compacta, podemos elaborar a lista de maxtermos: F(CBA) = M (1, 2, 5, 6, 7) F(CBA) = (1, 2, 5, 6, 7)Esta representao da funo o produto dos maxtermos correspondentes s combinaes das entradas, para as quais a funo assume o valor 0 na sada.Cabe referir que cada maxtermo constitudo por uma soma das variveis da funo, sendo agora entendidos como 0 se a correspondente varivel no estiver negada e por 1 se estiver negada. Como regra prtica para obter os maxtermos, poderemos escrever previamente o mintermo, obtendo-se o correspondente maxtermo, complementando todas as variveis e passando o produto a soma.

Para as variveis CBA teremos:LinhaCBAFMintermoMaxtermo

0000F(0,0,0)

1001F(0,0,1)

2010F(0,1,0)

3011F(0,1,1)

4100F(1,0,0)

5101F(1,0,1)

6110F(1,1,0)

7111F(1,1,1)

Tabela 1 Mintermos e maxtermos para uma funo de 3 variveisExemplo:CBAF

0000

0010

0101

0110

1001

1011

1100

1111

Representando a funo na forma cannica como soma de mintermos, temos:

Ou na forma de lista de mintermos:

Representando a funo na forma cannica como produto de maxtermos, temos:

Ou na forma de lista de maxtermos:

MTODO DOS MAPAS DE KARNAUGHO mtodo grfico dos mapas de Karnaugh um mtodo eficaz e rpido para simplificar funes at quatro variveis. Embora seja vlido para cinco ou seis variveis, desaconselhvel utiliz-lo nestes casos porque apresenta mais dificuldades que vantagens. Para aplicao do mtodo grfico necessrio construir um quadriltero que, por sua vez, se divide em 2n quadrculas elementares ou clulas. O expoente n o nmero de variveis da funo. A

B01

0

1

Na Figura 30 apresentam-se os grficos adequados para a reduo de funes de duas, trs e quatro variveis, respetivamente. A melhor aplicao do mtodo nestes casos. BACD00011110

00

01

11

10

BAC00011110

0

1

(a)(b)

(c)

Figura 30 - Grficos ou mapas de Karnaugh para reduo de funes de duas (a), trs (b) e quatro (c) variveis.Nas linhas e colunas devem aparecer todas as combinaes que se podem fazer ao atribuir os dois possveis valores que as variveis podem tomar. A ordem de colocao das combinaes deve ser tal que, de uma coluna ou linha para a seguinte, apenas muda uma varivel. Diz-se ento que, entre duas clulas consecutivas, existe adjacncia algbrica. Portanto, nos casos de duas, trs e quatro variveis, existe uma total coincidncia entre as adjacncias grfica e algbrica. A primeira clula, tanto no sentido horizontal como vertical, adjacente ltima.Para explicar melhor os passos necessrios para reduzir uma funo, partiremos de um caso concreto. Suponhamos que, partindo do enunciado de um problema, se chega tabela de verdade da Figura:CBAF

0000

0011

0101

0111

1000

1011

1100

1111

A expresso booleana correspondente, na forma de soma de mintermos, :

.Vejamos como podemos simplific-la.Colocando um 1 em cada clula onde a funo 1, obtemos o mapa de Karnaugh: BAC 00011110

0111

111

Para obter a expresso lgica mais simplificada combinam-se em grupos as clulas contendo 1s. Cada grupo s pode ter um nmero de 2n clulas (2, 4, 8 ...). O objetivo reunir as clulas em poucos grupos de grandes dimenses. Cada grupo ir fornecer um termo para a expresso lgica e quanto maior for a sua dimenso maior a simplificao.Devem-se observar as seguintes regras: Cada grupo s pode ter 2n clulas. Todos os 1 devem ser considerados. Os 0 no podem fazer parte do agrupamento. S se podem agrupar clulas adjacentes. Os agrupamentos devem ter a maior dimenso possvel. Os agrupamentos podem (devem) ser sobrepostos. A cada agrupamento corresponde um termo. O termo correspondente ao agrupamento obtido considerando apenas as variveis comuns a todas as clulas do grupo.BAC 00011110

0111

111

A cada grupo de 1s corresponde um termo. Fazem parte desse termo as variveis que mantm o valor no grupo. No grupo maior, o de quatro clulas, a varivel A mantm o valor 1, enquanto as variveis B e C tomam os valores 0 e 1, por isso no so consideradas. O termo correspondente ao agrupamento maior ento simplesmente A. No agrupamento menor B sempre 1, C sempre 0 e A toma os valores 1 e 0. Fazem parte do termo as variveis que mantm o valor, C=0 e B=1. Quando o valor for 0, a varivel aparece no termo negada. O termo correspondente ento CB.Ligando os termos pela operao OU, obtemos a expresso simplificada pretendida, Repare-se que a expresso do agrupamento menor . Mantendo B e C os seus valores, podemos p-los em evidncia: A soma lgica em termos que difiram apenas por uma varivel faz desaparecer (absorve) a varivel diferente. a coincidncia entre as adjacncias algbrica e grfica que justifica o mtodo.Na figura seguinte podemos observar agrupamentos das clulas nos extremos, uma vez que so adjacentes, resultando o termo .

BACD 00011110

00

01

1111

10

Observemos mais alguns agrupamentos possveis:

BACD00011110

00111

011

111

10111

Quanto maior for o agrupamento, mais simplificado o termo:BACD 00011110

001111

011111

11

10

Quanto maior for o agrupamento, mais simplificado o termo:BACD 00011110

001111

011111

111111

101111

F = 1

As 4 clulas dos cantos tambm so adjacentes e podem formar um grupo:

BACD 00011110

0011

01

11

1011

Seguem-se alguns exemplos de agrupamentos incorretos:

BACD 00011110

001

01

11

101

INCORRETO: clulas no adjacentes

BA

CD 00011110

00

011

111

101

INCORRETO: associao de 3 elementos, diferente de 2n.

Refira-se que possvel usar o mtodo dos mapas de Karnaugh para funes expressas na forma de produtos de somas, usando o princpio da dualidade . Nesse caso, seriam agrupados os 0s. O mtodo um pouco menos intuitivo que a minimizao de somas de produtos. Para se saber qual o mtodo que d melhores resultados necessrio experimentar ambos.Uma maneira de ultrapassar as dificuldades deste segundo mtodo complementar a funo dada, usar o mtodo de Karnaugh para a sua simplificao e, finalmente, complementar o resultado usando o teorema de De Morgan generalizado para obter uma expresso mnima na forma de produtos de somas.

Exerccios:

1. Simplifique, atravs do mtodo de Karnaugh, as funes obtidas das tabelas de verdade das figuras A e B:DCBAF

00001

00010

00101

00110

01001

01011

01101

01111

10001

10010

10101

10110

11000

11010

11100

11110

CBAF

0001

0010

0100

0110

1001

1011

1100

1110

Fig. A

Fig. BUsando mapas de Karnaugh, obtenha a expresso mais simplificada, na forma de soma de produtos, das seguintes funes:a. b.

Usando mapas de Karnaugh, desenhe o logigrama do circuito mais simples que implementa a seguinte funo:

O sistema de abertura da porta exterior de um banco funciona da seguinte forma: Se a chave mestre estiver desligada (m=0), a porta nunca abre (P=0). Estando a chave mestre ligada a porta abre se for acionado o boto de abertura (a=1) e o contacto da segunda porta estiver fechado (c=1) Estando a chave mestre ligada a porta abre sempre que o boto de emergncia for acionado (e=1). Estabelea a tabela de verdade que traduz a situao (P em funo de m, e, a, c), escreva a expresso booleana, simplifique-a e desenhe o logigrama correspondente.

Famlias LgicasOs circuitos integrados digitais esto agrupados, fundamentalmente em duas famlias lgicas: bipolares e MOS Da famlia bipolar a mais importante a TTL e da MOS a mais importante a CMOS.A tenso nominal para os circuitos integrados TTL ( Transstor Transstor Logic) de + 5 V com uma variao mxima de 5%, pelo que a alimentao s pode variar entra 4,75 V e 5,25 V).Para os circuitos integrados CMOS (Complementary Metal-Oxide Semiconductor) a alimentao pode variar de 3 a 8 V. Para efeitos de melhor comparao das duas famlias, assumiremos a mesma tenso nominal de + 5 V como sucede em TTL.Famlias lgicas bipolares:RTL Resistor Transistor Logic Lgica de transstor e resistncia.DTL Dode Transistor Logic Lgica de transstor e dodo.TTL Transistor Transistor Logic Lgica transstor-transstor.HTL High Threshold Logic Lgica de transstor com alto limiar.ECL Emitter Coupled Logic Lgica de emissores ligados.I2L Integrated-Injection Logic Lgica de injeo integrada.Interessa-nos particularmente a famlia TTLFamlias lgicas MOS (Metal xido Semicondutor)CMOS Complemantary MOS MOS de pares complementares NMOS/PMOSNMOS Utiliza s transstores MOS-FET canal N.PMOS Utiliza s transstores MOS-FET canal P.Interessa-nos particularmente a famlia CMOSCaratersticas da famlia TTL Transistor Transistor Logic rpida Ocupa muito espao Consome muita energia Funciona com alimentao de 5 V Srie 54 (-55 a +125 C) utilizaes militares Srie 74 ( 0 a +75 C) utilizaes industriais Sub-famlias: STD, S, LS, ALS, ASA famlia TTL principalmente reconhecida pelo facto de ter duas sries que comeam pelos nmeros 54 para os componentes de uso militar e 74 para os componentes de uso comercial.Caratersticas da famlia CMOS Complementary MOS A que menos consome Ocupa pouco espao lenta (verso standard) Funciona com alimentao entre 3 e 18 V Problemas na interface TTL para CMOS Em grande desenvolvimento. As primeiras sries da famlia CMOS foram as 4000/14000. Destacam-se atualmente as sub-famlias de alta velocidade HC e HCT que funcionam com tenses de alimentao de 2 a 6 V e so pino a pino e funo por funo compatveis com TTL. 74HC (compatvel, pino a pino e funo por funo, com os dispositivos TTL) 74HCT (inteiramente compatvel com TTL, eletricamente, pino a pino e funo por funo)Nveis lgicos e de rudo das famlias TTL e CMOSDefinies de nveis de tensoUOHmin - valor mnimo de tenso na sada no estado alto (HIGH - H)UIHmin - valor mnimo de tenso na entrada reconhecido como estado alto (HIGH - H).UILmax - valor mximo de tenso na entrada reconhecido como estado baixo (LOW - L) UOLmax - valor mximo de tenso na sada no estado baixo (LOW - L)Para garantir a compatibilidade de nveis de tenso, a tenso de sada deve estar contida nos intervalos de variao admissveis para a tenso de entrada. Nveis de rudoOs sinais eltricos esprios, que podem provocar tenses indesejveis entre os condutores eltricos, designam-se por rudo. Existe um rudo de baixa frequncia como o das variaes da tenso de alimentao, e um rudo de frequncia aleatria geralmente provocado por sinais em circuitos de comutao.Entende-se por imunidade ao rudo a capacidade denotada por um circuito de suportar uma certa variao da tenso de entrada sem que a sua sada mude de estado.A medida da imunidade ao rudo de determinada porta designada por margem de rudo. A margem de rudo, que se expressa em volts, pois o mximo valor do rudo que pode ser suportado por uma porta.Existem duas margens de rudo, respetivamente de nvel ALTO e de nvel BAIXO. Assim, teremos para margem de rudo de nvel ALTO: UOHmin - UIHmin e para margem de rudo de nvel BAIXO UILmx - UOLmx , respetivamente.Famlia Lgica TTLPara os circuitos TTL, a gama de valores da tenso de entrada que significam um nvel lgico BAIXO varia de 0V a 0,8V. De igual forma, a gama de valores da tenso de entrada que significam um nvel lgico ALTO varia de 2 V a 5 V. Os valores compreendidos entre 0,8 V e 2 V, porque produzem sadas imprevisveis, uma vez que podem ser interpretados pelas portas lgicas quer como nvel ALTO quer como nvel BAIXO, no so vlidos para uma correta operao das portas.Para a sada, os nveis de tenso so de 2,4 V para UOHmin, que sempre superior mnima tenso de entrada nvel ALTO, e de 0,4 V para UOLmx, que sempre inferior ao mximo valor da tenso de entrada, que ainda interpretado como um nvel BAIXO.

UOHmin (2,4 V) UOLmx (0,4 V)UIHmin (2 V)UILmx (0,8 V)UCC = +5 VFigura 31Margem de rudo: 0,4 VCompatibilidade de tenses: UOHmin > UIHmin UOLmx < UILmx Famlia Lgica CMOS

UOHmin (4,9 V) UOLmx (0,1 V)UDD = +5 VUIHmin (3,5 V)UILmx (1,5 V)Figura 32Margem de rudo: 1,4 VCompatibilidade de tenses: UOHmin > UIHmin UOLmx < UILmx Definies de nveis de correnteIILmax corrente mxima debitada pela entrada no estado baixo IIHmax corrente mxima absorvida pela entrada no estado alto IOLmax corrente mxima que pode ser absorvida pela sada no estado baixo IOHmax corrente mxima que pode ser debitada pela sada no estado alto

Compatibilidade de correntesPara a sada no estado baixo (L):IOLmax IILmax

Figura 33Para a sada no estado alto (H):IOHmax IIHmax

Figura 34

Valores tpicos de tenses e correntesParmetroCMOSTTL

4000B74HC74HCT7474LS74AS74ALS

UIH min (V)3,53,52,02,02,02,02,0

UIL mx (V)1,51,00,80,80,80,80,8

UOH min (V)4,954,94,92,42,42,72,7

UOL mx (V)0,050,10,10,40,50,50,4

IIH mx (A)111402020020

IIL mx (A)1111600400500100

IOH mx (mA)0,4440,40,420,4

IOL mx (mA)0,444168208

Tabela 2Estrutura interna de uma porta TTL

Figura 35 sada em totem-pole na famlia TTLEstrutura interna de uma porta CMOS

Figura 36 sada em totem-pole na famlia CMOSTipo de sadasSadas em totem-poleA maioria das portas lgicas apresentam-se numa configurao totem-pole, designao que resulta da existncia de dois dispositivos de comutao (Sa,Sb) colocados conforme se indica na figura

Figura 37Internamente, o controlo dos dois comutadores realizado de modo a que esteja fechado um e s um dos comutadores.No possvel ligar entre si sadas totem-pole Existe a possibilidade de uma das sadas estar no estado alto e a outra estar no estado baixo, ocasionando um curto-circuito.

Figura 38Sadas em coletor aberto (open-collector/open-drain)Neste tipo de sada, em termos da representao simplificada com comutadores, apenas existe o comutador Sb que quando fechado coloca a sada no estado baixo.

Figura 39No circuito externo sada em coletor aberto deve existir uma resistncia ligada a Vcc (+5V) resistncia de pull-up - para que a sada apresente um valor aceitvel no intervalo de variao para o estado alto quando Sb est aberto. possvel ligar entre si sadas em coletor aberto.

Figura 40Sadas de trs estados (tri-state)As sadas de trs estados so idnticas s sadas em totem-pole, existindo, no entanto, uma entrada adicional (enable) que permite que os dois comutadores (Sa e Sb) estejam abertos simultaneamente.

Figura 41Nestas condies diz-se que a sada est num estado de alta impedncia (Hi-Z), como se estivesse desligada do circuito possvel ligar entre si sadas tri-state, desde que apenas uma esteja habilitada (enabled)

Figura 42S a porta B est enabled

18