Conversores Analógico-Digital para Controlo de Conversores ... · iii Resumo Este trabalho é...

Transcript of Conversores Analógico-Digital para Controlo de Conversores ... · iii Resumo Este trabalho é...

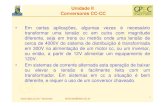

Conversores Analógico-Digital

para Controlo de Conversores CC-CC

Maria João Perdigão Barradas

Dissertação para obtenção do Grau de Mestre em

Engenharia Electrotécnica e de Computadores

Júri

Presidente Doutor Nuno Cavaco Gomes Horta

Orientador Doutor Marcelino Bicho dos Santos

Co-Orientador Doutora Maria Beatriz Mendes Batalha Vieira Vieira Borges

Vogal Doutor Jorge Manuel dos Santos Ribeiro Fernandes

Outubro de 2012

i

Agradecimentos

Para ser grande, sê inteiro: nada

Teu exagera ou exclui.

Sê todo em cada coisa. Põe quanto és

No mínimo que fazes.

Assim em cada lago a lua toda

Brilha, porque alta vive.

Fernando Pessoa

Agradeço primeiro que tudo aos meus pais, Joaquina e João Barradas, porque sem que eles primeiro me

tivessem formado como pessoa nunca me poderia ter formado como profissional. Por todo o apoio agradeço

da mesma forma aos meus avós Ermelinda Lopes e Manuel Barradas e aos saudosos Lídia e João Perdigão e

também à tia Didi. O vosso amor, confiança e dedicação são e sempre serão a maior inspiração.

Ao Pedro agradeço por ter sido a companhia mais presente destes anos de curso, o namorado mas também

amigo e colega que tornou mais suave esta caminhada, da mesma forma que trouxe mais luz ao caminho de

todos os dias.

Para a família Marçal o meu obrigado por sempre me terem feito sentir como parte da família.

Aos grandes amigos que souberam perdoar as minhas ausências durante os anos de cursos sem nunca deixar

de me tocar com a sua amizade. Obrigada Susana Monte, José Inverno, Elsa Laranjinho, Liliana Nunes, Janete

Ramos, José Luís Bailão e Joaquim César.

Aos meus colegas e acima de tudo amigos que me acompanharam nos últimos seis anos, agradeço-vos pelas

horas intermináveis de estudo e trabalho, sem as quais teria sido infinitamente mais difícil concluir o curso:

Pedro Domingos, José Carlos Santos, Ricardo Lucas, João Cabral, Rafael Ortega, Jean Mousinho, Guilherme

Fernandes, Ricardo Faria, Arleth Gonçalves, Marco Castanho e Carolina Moniz.

Não poderia esquecer os colegas do NEEC, das JEEC e dos Delegados do MEEC, junto com o Professor Leonel

Sousa, pela confiança que depositaram em mim para representar projectos que me proporcionaram

experiências organizativas e pessoais sem par durante todos os anos de curso.

Por fim, mas não menos importante, gostaria de deixar o meu agradecimento aos meus orientadores Professor

Marcelino Santos e Professora Beatriz Borges pelo profissionalismo e dedicação como docentes e orientadores

que inspirou a paixão Microelectrónica e Electrónica de Potência que fez com que esta tese fosse possível.

Agradeço de igual forma aos meus colegas do INESC-ID, Bruno Jacinto, Jorge Esteves, Carlos Moreira, Abílio

Parreira, Valter Sádio, João Pereira, Pedro Braga, Vítor Silva e Professor Júlio Paisana e aos engenheiros da

Silicon Gate, cujo apoio foi fundamental para construir este trabalho tal como está.

iii

Resumo

Este trabalho é motivado pela necessidade de procurar soluções eficientes no que toca a conversores A/D que

discretizem a diferença entre a tensão de saída do conversor CC-CC e a tensão de referência. Projectam-se dois

conversores A/D baseados cada um num único comparador com várias saídas, para integrar conversores CC-CC

a operar a 2 e 20MHz, com oito e duas saídas, respectivamente, e intervalos de discretização não-lineares.

Após o estudo de diversas topologias, opta-se por utilizar de um comparador baseado num pré-amplificador

seguido de andares de báscula, tantas quantas as saídas do comparador. As várias saídas são obtidas alterando

a capacidade dos nós de saída, seja alterando as dimensões da báscula seja ligando um transístor pMOS que

opera como capacidade à saída a deslocar. Obtêm-se assim conversores A/D implementados em tecnologia

UMC 130nm que permitem detectar variações na saída do CC-CC em menos 10% do período de relógio.

As especificações são cumpridas para ambos os comparadores. Obteve-se para o comparador com oito saídas a

2MHz um atraso máximo na detecção do transitório de carga de 4ns, com um consumo de13,21μA. Em regime

quase estacionário o consumo é de 11,85μA, sendo de 16,6μA para o pior corner. A tensão de desvio máxima é

de 6,52mV. Para o comparador com duas saídas a 20MHz obtém-se um atraso máximo de 2ns na detecção do

transitório de carga, com um consumo de 31,54μA. Em regime quase estacionário o consumo é 30,89μA,

consumindo 41,03μA no pior corner. A tensão de desvio máxima situa-se em 7,3mV.

Palavras-chave

Controlo digital de conversores CC-CC, Conversor A/D, Comparador, Comparador com múltiplas saídas

v

Abstract

This work is motivated by the research of efficient solutions for A/D converters that quantize the difference

between the output voltage of the DC-DC and the reference voltage. Two A/D converters, each one based on a

single comparator, were designed: one with eight outputs at 2MHz and other one at 20MHz with two outputs.

After studying several alternatives, the design of a clocked comparator was preferred. This comparator is based

on a pre-amplifier, followed by several latch stages, as many as the outputs of the comparator. The multiple

outputs were obtained by changing the capacity in the output nodes with two different alternatives: change

the dimensions in the latch stage or connecting a pMOS transistor working as capacity in the output where the

offset is created. This solution leads to the design of A/D converts in 130nm UMC technology that allow to

sense a DC-DC load transient in less 10% than a clock period.

Both circuits meet the specifications. The comparator with eight outputs at 2MHz has a maximum delay of 4ns

during the detection of a load transient with a current consumption of 13,21μA. In a steady-state the current

consumption is 11,85μA and 16,6μA in the worst corner. The maximum offset voltage is 6,52mV. For the

comparator with two outputs at 20MHz the detection of a load transient occurs in 2ns with a current

consumption of 31,54μA. In steady-state the power consumption is 30,89μA and 41,03μA for the worst corner.

The maximum offset voltage is 7,3mV.

Keywords

DC-DC Converters with digital control, A/D Converters, Comparators, Comparators with multiple outputs

Conteúdos

vii

Conteúdos

Lista de Figuras ........................................................................................................................................ xi

Lista de Tabelas ..................................................................................................................................... xvii

Lista de Acrónimos ................................................................................................................................ xxi

Capítulo 1 Introdução .............................................................................................................................. 1

1.1 Motivação ...................................................................................................................................... 2

1.2 Objectivos de Investigação e Principais Contribuições.................................................................. 3

1.3 Organização da Dissertação ........................................................................................................... 4

Capítulo 2 Conversores Analógico-Digital para Controlo de Conversores CC-CC .................................... 5

2.1 Introdução ..................................................................................................................................... 6

2.2 Conversor CC-CC Redutor .............................................................................................................. 6

2.3 Conversores Analógico-Digital e Comparadores ........................................................................... 9

2.3.1 Topologias Comuns de Conversores Analógico-Digital ........................................................... 9

2.3.2Topologias Comuns de Comparadores .................................................................................. 14

2.4 Estado da Arte ............................................................................................................................. 15

2.4.1 Conversores Analógico-Digital .............................................................................................. 16

2.4.2 Comparadores ...................................................................................................................... 20

2.5 Conversores Analógico-Digital para Controlo de Conversores CC-CC ......................................... 25

2.5.1 Comparador convencional rápido ........................................................................................ 27

2.5.2 Comparador misto ................................................................................................................ 27

2.5.3 Comparador comutado ........................................................................................................ 28

2.5.4 Comparador baseado num inversor ..................................................................................... 29

Capítulo 3 Implementação .................................................................................................................... 33

3.1 Fluxo de Projecto ......................................................................................................................... 34

3.2 Estudo de diversas topologias de comparadores ........................................................................ 34

3.2.1 Comparador convencional rápido ........................................................................................ 35

3.2.2 Comparador misto ................................................................................................................ 36

3.2.3 Comparador comutado ........................................................................................................ 37

3.2.4 Comparador baseado num inversor ..................................................................................... 39

3.2.5 Análise .................................................................................................................................. 43

3.3 Comparador para controlo a 20 MHz .......................................................................................... 43

3.4 Comparador para controlo a 2 MHz ............................................................................................ 45

Conteúdos

viii

Capítulo 4 Análise e Resultados ............................................................................................................ 49

4.1 Estudo de diversas topologias de comparadores ........................................................................ 50

4.1.1 Comparador convencional rápido ........................................................................................ 51

4.1.2 Comparador misto ................................................................................................................ 54

4.1.3 Comparador comutado ........................................................................................................ 56

4.1.4 Comparador baseado num inversor ..................................................................................... 59

4.1.5 Análise comparativa ............................................................................................................. 62

4.2 Comparador para controlo a 20 MHz .......................................................................................... 63

4.3 Comparador para controlo a 2 MHz ............................................................................................ 67

4.4 Análise ......................................................................................................................................... 71

Capítulo 5 Layout ................................................................................................................................... 73

5.1 Aspectos comuns ......................................................................................................................... 74

5.2 Comparador para controlo a 20 MHz .......................................................................................... 77

5.2 Comparador para Controlo a 2 MHz ........................................................................................... 80

Capítulo 6 Conclusão e Trabalho Futuro ............................................................................................... 83

6.1 Conclusões ................................................................................................................................... 84

6.2 Trabalho Futuro ........................................................................................................................... 85

Referências Bibliográficas ...................................................................................................................... 87

Apêndice A ............................................................................................................................................ 91

A.1 Estudo de diversas topologias de comparadores e circuitos comuns ......................................... 92

A.2 Comparador para controlo a 20 MHz .......................................................................................... 94

A.3 Comparador para controlo a 2 MHz ............................................................................................ 94

Apêndice B ............................................................................................................................................. 95

B.1 Estudo de diversas topologias de comparadores ........................................................................ 96

B.2 Comparador para controlo a 20 MHz .......................................................................................... 98

B.3 Comparador para controlo a 2 MHz ............................................................................................ 99

Apêndice C ........................................................................................................................................... 101

C.1 Comparador para controlo a 20 MHz ........................................................................................ 102

C.2 Comparador para controlo a 2 MHz .......................................................................................... 104

Lista de Figuras

xi

Lista de Figuras

Figura 2.1 Esquema eléctrico do Conversor CC-CC Redutor. 7

Figura 2.2 Estados do Conversor CC-CC Redutor: (a)estado Ligado; (b)estado Desligado. 8

Figura 2.3 Comportamento do CC-CC Redutor: (a)tensão na bobine em MCC; (b)corrente na bobine em MCC; (c)tensão na bobine na MCD; (d)corrente na bobine em MCD. 8

Figura 2.4 Corrente na bobine na fronteira entre os dois modos de condução. 9

Figura 2.5 Funcionamento do conversor de duplo declive: (a) esquema representativo; (b) diagrama temporal. 9

Figura 2.6 Esquema representativo do funcionamento do conversor de aproximações sucessivas. 10

Figura 2.7 Funcionamento do conversor algorítmico: (a) arquitectura; (b) fluxograma do algoritmo de procura binária. 10

Figura 2.8 Representação do conversor sigma-delta. 10

Figura 2.9 Esquema que representa a arquitectura do conversor flash. 11

Figura 2.10 Representação da arquitectura do conversor de dois passos. 11

Figura 2.11 Representação do conversor folding. 11

Figura 2.12 Conversor de interpolações: (a) arquitectura; (b) característica de transferência. 12

Figura 2.13 Esquema representativo do conversor pipelined. 12

Figura 2.14 Representação do conversor intervalado no tempo. 12

Figura 2.15 Representação do conversor de acompanhamento com contador. 13

Figura 2.16 Esquema representativo do conversor de acompanhamento com janela. 13

Figura 2.17 Par diferencial em malha aberta. 14

Figura 2.18 Característica em repouso do comparador: (a) sem tensão de desvio à entrada; (b) com tensão de desvio à entrada. 14

Figura 2.19 Característica temporal de um comparador com histerese. 14

Figura 2.20 Esquema eléctrico do comparador rápido. 15

Figura 2.21 Esquema representativo do comparador comutado. 15

Figura 2.22 Esquema simplificado do conversor A/D de aproximações sucessivas de Fotouhi e Hodges. 16

Figura 2.23 Esquema conceptual do conversor de 3 bits do conversor de aproximações sucessivas de Hamdé. 16

Figura 2.24 Ilustração do princípio de funcionamento do conversor de aproximações sucessivas com várias células. 17

Figura 2.25 (a) Arquitectura do conversor para aplicações de pó inteligente 8 bits; (b) Esquema do

conversor A/D de acompanhamento de 4 bits implementado por Allier et al. 17

Figura 2.26 Esquema do conversor A/D de acompanhamento de 4 bits implementado por Allier et al. 18

Figura 2.27 Conversor flash de elevada velocidade: (a) Esquema representativo da arquitectura; (b) Comparador. 18

Figura 2.28 Representação esquemática do A/D intervalado no tempo. 19

Figura 2.29 Arquitectura do conversor A/D de acompanhamento controlado por relógio. 19

Figura 2.30 Representação esquemática do conversor de acompanhamento assíncrono. 20

Figura 2.31 (a) Esquema eléctrico do comparador quantum; (b) característica de transferência do comparador quantum; (c) arquitectura do comparador TIQ; (d) característica de transferência do comparador TIQ. 21

Figura 2.32 Esquema do comparador dinâmico com clock booster: (a) comparador; (b) clock booster. 21

Figura 2.33 Esquema eléctrico do comparador dinâmico de elevada precisão. 21

Figura 2.34 Comparador para conversores A/D de alta velocidade: (a)pré-amplificador; (b)báscula. 22

Figura 2.35 Diagrama esquemático do comparador de correntes. 22

Figura 2.36 (a) Esquema eléctrico do comparador proposto por Schinkel et al.; (b) circuito implementado por Goll et al. 23

Figura 2.37 (a) Esquema eléctrico do comparador de Abbas et al.; (b) solução apresentada por Jeong e Kim. 23

Lista de Figuras

xii

Figura 2.38 Comparador com cancelamento de tensão de desvio à entrada. 24

Figura 2.39 Comparador proposto por Khosrov: (a)pré-amplificador; (b)báscula. 24

Figura 2.40 Topologia do Conversor CC-CC Redutor com controlo digital. 25

Figura 2.41 Conversor A/D baseado num comparador. 26

Figura 2.42 (a) Característica desejada para o conversor a 2 MHz; (b) característica pretendida para o conversor a 20 MHz. 27

Figura 2.43 Comparador convencional rápido: (a) esquema eléctrico; (b) corrente nos vários transístores e tensão de saída. 27

Figura 2.44 Esquema eléctrico do comparador misto. 28

Figura 2.45 Esquema eléctrico do latch de saída. 28

Figura 2.46 Comparador misto: (a) tensão de entrada e sinal de relógio; (b) tensão nos nós Di; (c) tensão de saída da báscula; (d) tensão à saída do comparador. 28

Figura 2.47 Esquema eléctrico do conversor comutado. 29

Figura 2.48 Comparador comutado: (a) tensão de entrada e sinal de relógio; (b) tensão nos nós Di. (c) tensão de saída da báscula; (d) tensão à saída do comparador. 29

Figura 2.49 (a) Dois andares de inversores; (b) característica de transferência (vermelho) tensão de

entrada; (azul) saída do primeiro inversor; (verde) saída do segundo inversor. 30

Figura 2.50 (a) Fenómeno de injecção de carga; (b) Cancelamento da injecção de carga por

introdução de transístores dummy. 30

Figura 2.51 Esquema eléctrico do comparador baseado num inversor. 31

Figura 2.52 Comparador baseado num inversor: (a) tensão de entrada e de referência; (b) tensão aos

terminais do condensador; (c) (d) sinais de relógio; (e) entrada do primeiro inversor;

(f) saída do primeiro inversor. 31

Figura 2.53 Comparador baseado num inversor: (a) saída do segundo inversor (b) (c) saídas do

comparador; (d) tensão de saída. 32

Figura 3.1 Metodologia de projecto. 34

Figura 3.2 Esquema eléctrico da solução proposta para o comparador convencional de dois níveis. 35

Figura 3.3 Comparador convencional: (a) corrente na saída do par diferencial; (b) corrente nos espelhos de corrente; (c) tensão na saída do circuito. 35

Figura 3.4 Esquema eléctrico da solução proposta para o comparador misto de dois níveis. 36

Figura 3.5 Comparador misto com dois níveis: (a) tensão de entrada e sinal de relógio; (b) saída do latch. 36

Figura 3.6 Comparador misto com dois níveis: (a) (b) tensão nos nós Di das básculas; (c) (d) tensão de saída das básculas. 37

Figura 3.7 Esquema eléctrico da solução proposta para o comparador comutado de 2 níveis. 38

Figura 3.8 Comparador comutado com dois níveis: (a)tensão de saída da báscula de -5mV; (b) tensão nos nós Di; (c) corrente nas básculas (d) tensão de saída da báscula de -5mV. 38

Figura 3.9 Comparador comutado com dois níveis: (a) tensão de saída da báscula de +5mV; (b) saída do latch. 38

Figura 3.10 Característica dos dois estágios de inversores que compõem o comparador. 39

Figura 3.11 Esquema eléctrico do comparador baseado num inversor com dois níveis. 40

Figura 3.12 Comparador baseado num inversor com dois níveis: (a) tensão de entrada e de referência; (b) tensão de saída. 40

Figura 3.13 Comparador baseado num inversor com dois níveis: (a) (b) sinais de relógio;

(c) (d) tensão aos terminais do condensador (+5mV); (e) tensão à saída do primeiro

inversor (+5mV); (f) tensão à saída do segundo inversor (+5mV). 41

Figura 3.14 Comparador baseado num inversor com dois níveis: (a) (b) saídas do comparador (+5mV); (c) (d) tensão aos terminais do condensador (-5mV); (e) tensão à saída do primeiro inversor (-5mV); (f) tensão à saída do segundo inversor (-5mV). 42

Figura 3.15 Comparador baseado num inversor com dois níveis: (a) (b) saídas do comparador (-5mV). 43

Figura 3.16 Diagrama de blocos do comparador a 20 MHz. 44

Lista de Figuras

xiii

Figura 3.17 Comparador a 20 MHz: (a) tensão de entrada e sinal de relógio; (b) tensão nos nós Di; (c) (d) tensão de saída das básculas; (e) corrente nas básculas; (f) saída do circuito. 44

Figura 3.18 Diagrama de blocos do comparador a 2 MHz. 45

Figura 3.19 Esquema eléctrico do comparador com oito saídas. 46

Figura 3.20 Comportamento esperado para o comparador a 2 MHz: (a) tensões de entrada e de referência; (b) relógio; (c) (d) corrente nas básculas; (e) tensão de saída dos latchs. 47

Figura 4.1 Simulação DC do comparador convencional com duas saídas. 51

Figura 4.2 Simulação em corners do comparador convencional com duas saídas. 52

Figura 4.3 Consumo em corners do comparador convencional com duas saídas. 52

Figura 4.4 Simulação de Monte Carlo do comparador convencional com duas saídas. 52

Figura 4.5 Resposta do comparador convencional com duas saídas a um transitório de carga. 53

Figura 4.6 Resposta em regime quase estacionário do comparador misto com duas saídas. 54

Figura 4.7 Simulação em corners do comparador misto com duas saídas. 55

Figura 4.8 Consumo em corners do comparador misto com duas saídas. 55

Figura 4.9 Simulação de Monte Carlo do comparador misto com duas saídas. 55

Figura 4.10 Resposta a um transitório de carga do comparador misto com duas saídas. 56

Figura 4.11 Resposta do comparador comutado com duas saídas em regime quase estacionário. 57

Figura 4.12 Simulação em corners do comparador comutado com duas saídas em regime quase

estacionário. 57

Figura 4.13 Consumo em corners em regime quase estacionário do comparador comutado com duas saídas. 58

Figura 4.14 Simulação de Monte Carlo do comparador comutado com duas saídas em regime quase estacionário. 58

Figura 4.15 Resposta do comparador comutado quando na entrada existe um transitório de carga. 59

Figura 4.16 Resposta do comparador baseado num inversor com duas saídas em regime quase estacionário. 59

Figura 4.17 Simulação em corners do comparador baseado num inversor com duas saídas em regime quase estacionário. 60

Figura 4.18 Consumo em corners do comparador baseado num inversor com duas saídas em regime quase estacionário. 60

Figura 4.19 Simulação de Monte Carlo do comparador baseado num inversor com duas saídas em regime quase estacionário. 61

Figura 4.20 Resposta do comparador baseado num inversor com duas saídas ao transitório de carga. 61

Figura 4.21 Consumo dos diversos comparadores em estudo em regime estacionário. 62

Figura 4.22 Análise do pior corner dos vários comparadores. 62

Figura 4.23 Tensão de desvio dos vários comparadores. 63

Figura 4.24 Atraso nos vários comparadores. 63

Figura 4.25 Simulação em regime quase estacionário do comparador comutado com duas saídas: (a) 20 MHz; (b) 200 MHz. 64

Figura 4.26 Consumo em corners do comparador comutado com duas saídas a 20 MHz e 200 MHz. 65

Figura 4.27 Simulação em corners do comparador comutado com duas saídas: (a) 20 MHz; (b) 200 MHz. 65

Figura 4.28 Simulação de Monte Carlo do comparador comutado com duas saídas: (a)20 MHz; (b) 200 MHz. 66

Figura 4.29 Simulação do transitório de carga no comparador comutado com duas saídas: (a) 20 MHz; (b) 200 MHz. 67

Figura 4.30 Simulação em regime quase estacionário para o comparador a 2 MHz. 68

Figura 4.31 Consumo em corners do comparador a 2 MHz com oito saídas. 69

Figura 4.32 Simulação em corners do comparador a 2 MHz com oito saídas. 69

Figura 4.33 Simulação de Monte Carlo para o comparador comutado com oito saídas a 2 MHz. 70

Figura 4.34 Resposta do comparador a 2 MHz a um transitório de carga. 70

Lista de Figuras

xiv

Figura 4.35 Desempenho dos circuitos em estudo: (a) consumo em regime quase estacionário; (b) consumo no pior corner; (c) tensão de desvio na pior saída (d) atraso da saída relativa ao relógio. 71

Figura 5.1 Organização do layout. 74

Figura 5.2 Interdigitação de transístores de carga do par diferencial. 75

Figura 5.3 Interdigitação dos transístores do par diferencial. 75

Figura 5.4 Dummy do par diferencial. 75

Figura 5.5 Desenho das pistas que transportam os sinais Di e de relógio. 76

Figura 5.6 Interruptor de polarização do par diferencial e inversores de regeneração do relógio. 76

Figura 5.7 Disposição espacial dos elementos de circuito. 77

Figura 5.8 Layout do comparador com duas saídas. 77

Figura 5.9 Simulação extraída do comparador com dois níveis em regime quase estacionário a 20 MHz. 78

Figura 5.10 Simulação extraída do comparador com dois níveis em regime quase estacionário a 200 MHz. 78

Figura 5.11 Resposta do comparador com duas saídas em condições de transitório de carga obtida

em simulação após layout a 20 MHz. 78

Figura 5.12 Resposta do comparador com duas saídas em condições de transitório de carga obtida

em simulação após layout a 200 MHz. 79

Figura 5.13 Comparação dos resultados pré e após layout a 20 MHz: (a) vFB-VREF para o qual as saídas comutam; (b) consumo do circuito; (c) atraso; (d) tensão de desvio em simulação de Monte Carlo. 79

Figura 5.14 Disposição espacial dos elementos de circuito no comparador com oito saídas. 80

Figura 5.15 Layout do comparador com oito saídas. 80

Figura 5.16 Simulação extraída em regime quase estacionário do comparador com oito saídas. 81

Figura 5.17 Resposta do comparador com oito saídas ao transitório de carga obtida em simulação após layout. 81

Figura 5.18 Comparação dos resultados pré e após layout a 2 MHz: vFB-VREF para o qual as saídas comutam. 81

Figura 5.19 Comparação dos resultados pré e após layout a 2 MHz: (a) consumo do circuito; (b) atraso; (c) tensão de desvio em simulação de Monte Carlo. 82

Figura 6.1 Característica do A/D baseado num comparador com oito níveis (azul) versus característica de um A/D de 4 bits (vermelho). 84

Figura A.1 (a) Inversor em tecnologia AMS 0,35μm; (b) Latch em tecnologia AMS 0,35μm. 92

Figura A.2 Comparador convencional com duas saídas. 92

Figura A.3 Comparador misto com duas saídas. 92

Figura A.4 Comparador comutado com duas saídas em tecnologia AMS 0,35μm. 93

Figura A.5 Comparador baseado num inversor (a) Inversor; (b) porta NAND. 93

Figura A.6 Comparador baseado num inversor com duas saídas. 93

Figura A.7 Comparador comutado com duas saídas em tecnologia UMC 130 nm. 94

Figura A.8 Esquema eléctrico da báscula. 94

Figura A.9 Comparador comutado com oito saídas. 94

Figura B.1 Simulação DC do comparador convencional. 96

Figura B.2 Simulação do transitório de carga do comparador convencional. 96

Figura B.3 Simulação em regime quase estacionário do comparador misto. 96

Figura B.4 Simulação do transitório de carga do comparador misto. 97

Figura B.5 Simulação em regime quase estacionário do comparador comutado a 2 MHz com duas saídas em AMS 0,35μm. 97

Figura B.6 Simulação do transitório de carga do comparador comutado a 2 MHz com duas saídas em AMS 0,35μm. 97

Figura B.7 Simulação em regime quase estacionário do comparador baseado num inversor a 2 MHz com duas saídas. 98

Lista de Figuras

xv

Figura B.8 Simulação do transitório de carga do comparador baseado num inversor a 2 MHz com duas saídas. 98

Figura B.9 Simulação em regime quase estacionário do comparador comutado a 20 MHz com duas saídas. 98

Figura B.10 Simulação do transitório de carga do comparador comutado a 20 MHz com duas saídas. 99

Figura B.11 Simulação em regime quase estacionário do comparador comutado a 2 MHz com oito saídas. 99

Figura B.12 Simulação do transitório de carga do comparador comutado a 2 MHz com oito saídas. 99

Figura C.1 Layout do comparador comutado com duas saídas. 102

Figura C.2 Detalhes do layout do comparador comutado com duas saídas. 103

Figura C.3 Layout do comparador comutado com oito saídas. 104

Figura C.4 Detalhes do layout do comparador comutado com oito saídas. 105

Lista de Tabelas

xvii

Lista de Tabelas

Tabela 1.1 Especificações do conversor A/D para o CC-CC a 2 MHz. 3

Tabela 1.2 Especificações do conversor A/D para o CC-CC a 20 MHz. 4

Tabela 2.1 Resumo do estado da arte no que aos Conversores A/D concerne. 20

Tabela 2.2 Resumo do estado da arte relativo aos comparadores. 25

Tabela 3.1 Dimensionamento do comparador convencional com duas saídas. 36

Tabela 3.2 Dimensionamento do comparador misto com duas saídas. 37

Tabela 3.3 Dimensionamento do comparador a 2 MHz. 39

Tabela 3.4 Dimensionamento do comparador a 2 MHz. 40

Tabela 3.5 Resultados do estudo preliminar. 43

Tabela 3.6 Dimensionamento do comparador com duas saídas a 20 MHz. 44

Tabela 3.7 Dimensionamento do comparador a 2 MHz. 46

Tabela 4.1 Definição dos corners de tensão, temperatura e processo dos transístores para a tecnologia AMS 0,35µm.

50

Tabela 4.2 Definição dos corners de tensão, temperatura e processo dos transístores e condensadores para a AMS 0,35µm.

50

Tabela 4.3 Definição dos corners de tensão, temperatura e processo dos transístores para a tecnologia UMC 130 nm.

51

Tabela 4.4 Resultados de simulação DC do comparador convencional com duas saídas. 51

Tabela 4.5 Resultados de simulação DC de Monte Carlo do comparador convencional com duas saídas.

53

Tabela 4.6 Resultados da resposta a um transitório de carga do comparador convencional com duas saídas.

53

Tabela 4.7 Atraso e consumo do comparador convencional com 2 saídas em função da corrente de polarização.

54

Tabela 4.8 Resultados de simulação em regime quase estacionário do comparador misto com duas saídas.

54

Tabela 4.9 Resultados de simulação de Monte Carlo em regime quase estacionário do comparador misto com duas saídas.

55

Tabela 4.10 Resultados de simulação de um transitório de carga do comparador misto com duas saídas.

56

Tabela 4.11 Resultados de simulação em regime quase estacionário do comparador comutado com duas saídas.

57

Tabela 4.12 Resultados de simulação de Monte Carlo do comparador comutado com duas saídas. 58

Tabela 4.13 Resultados de simulação do comparador comutado quando na entrada existe um transitório de carga.

59

Tabela 4.14 Resultados de simulação em regime quase estacionário do comparador baseado num inversor com duas saídas.

60

Tabela 4.15 Resultados de simulação de Monte Carlo em regime quase estacionário do comparador baseado num inversor com duas saídas.

61

Tabela 4.16 Resultados de simulação do comparador comutado quando na entrada existe um transitório de carga.

62

Tabela 4.17 Resultados de simulação em regime quase estacionário para o comparador a 20 MHz e 200 MHz.

64

Tabela 4.18 Resultados de simulação de Monte Carlo em regime quase estacionário do comparador a 20 MHz e 200 MHz.

66

Tabela 4.19 Resultados de simulação do comparador a 20 MHz quando na entrada existe um transitório de carga.

67

Tabela 4.20 Resultados de simulação em regime quase estacionário para o comparador a 2 MHz. 68

Tabela 4.21 Diferença entra saídas em simulação de Monte Carlo em regime quase estacionário do comparador a 2 MHz.

69

Tabela 4.22 Tensão de desvio das saídas do comparador. 69

xviii

Tabela 4.23 Resultados de simulação do comparador a 2 MHz quando na entrada existe um transitório de carga.

70

Tabela 6.1 Comparação dos resultados obtidos face ao estado da arte. 84

Lista de Acrónimos

xxi

Lista de Acrónimos

Acrónimo Significado

A/D Analógico-Digital

AMS Austria MicroSystems

ASIC Application-Specific Integrated Circuit

CC Corrente Contínua

CC-CC Conversor de Corrente Contínua para Corrente Contínua

CMOS Complementary Metal-Oxide Semiconductor

D/A Digital-Analógico

DRC Design Rule Checker

DSP Digital Signal Processor

FPGA Field-Programmable Gate Array

LSB Least Significant Bit

LVS Layout versus Schematic

MCC Modo de Condução Contínua

MCD Modo de Condução Descontínua

MOS Metal-Oxide Semiconductor

MLI Modelação de Largura de Impulso

MSB Most Significant Bit

ne Não especificado

nMOS MOS tipo-n

pMOS MOS tipo-p

RAS Registo de Aproximções Sucessivas

S & H Sample and Hold

S-R Set-Reset

TIQ Threshold Inverter Quantization

UMC United Microelectronics Corporation

1

Capítulo 1 Introdução

Conteúdos

1.1 Motivação 2

1.2 Objectivos de Investigação e Principais Contribuições 3

1.3 Organização da Dissertação 4

1. Introdução

2

1.1 Motivação

Nos anos mais recentes a indústria da Electrónica tem vindo a registar extraordinários avanços, motivados pela

satisfação das exigências constantes dos consumidores, ávidos pelas últimas novidades em telemóveis, tablets,

leitores de música e computadores. À medida que a sua utilização se massifica, cresce também a quantidade de

funcionalidades que os mesmos oferecem.

Veja-se o caso do telemóvel, que em menos de vinte anos passou de um aparelho para fazer chamadas com

quinhentos gramas de peso para um pequeno computador portátil com menos de cem gramas com uma

capacidade de processamento surpreendente. Para os consumidores é inaceitável que o aumento da

capacidade de processamento implique uma diminuição da portabilidade dos aparelhos. Como o mercado

requer que o tempo entre cargas da bateria não diminua, duas soluções se afiguram para os projectistas:

aumentar o tamanho da bateria ou diminuir a energia necessária à operação dos dispositivos. A primeira

solução é deveras desvantajosa dado que implicaria fabricar dispositivos mais caros e pesados. Sendo assim,

opta-se por gerir a energia da bateria de forma eficiente, o que conduz a uma redução da energia necessária ao

funcionamento dos circuitos que compõem os aparelhos aumentado a eficiência dos circuitos e o rendimento

dos conversores de energia que os alimentam. Nos circuitos projectados actualmente existe ainda a

necessidade de várias tensões de alimentação para vários circuitos, sendo que o dispositivo apenas possui uma

bateria.

A gestão da potência consumida pelos circuitos electrónicos fez surgir a necessidade de projectar fontes

comutadas com elevados rendimentos, que convertam a tensão da bateria numa outra tensão. Um dos

circuitos mais utilizados neste contexto é o Conversor de Corrente Contínua para Corrente Contínua (CC-CC),

nomeadamente o Conversor CC-CC Redutor, que como o próprio nome indica converte a tensão de entrada

numa tensão de saída de valor mais baixo. Este tipo de conversor é bastante eficiente, podendo atingir

rendimentos que vão dos 80% até aos 98%.

A complexidade do projecto dos conversores CC-CC em geral, e do conversor redutor em particular, deriva em

parte da necessidade de circuitos de controlo que comandem a condução dos dispositivos de potência. O

controlo dos conversores CC-CC surge como resposta às variações sofridas pela bateria e pela carga. As

variações associadas à tensão da bateria prendem-se com a descarga da mesma bem como com o facto de esta

reagir a condições ambientais e de carga. Pretende-se então que a tensão na saída dos conversores se

mantenha constante, independentemente das perturbações existentes na bateria.

Os controladores de fontes comutadas existentes são maioritariamente circuitos analógicos, no entanto, devido

às vantagens que apresentam, cada vez mais se utilizam circuitos electrónicos digitais para efectuar o controlo.

Apesar das saídas do conversor serem analógicas, motivo pelo qual se tem vindo a preferir o domínio analógico

no que toca a controladores, a exigência crescente ao nível de desempenho e custo dita a preferência pelo

digital, já que apresenta inúmeras vantagens [1]. O domínio digital torna-se desde logo vantajoso devido à

quantidade e qualidade da informação disponível neste tipo de circuitos, o que permite implementar

algoritmos avançados de controlo. Por outro lado os circuitos digitais apresentam maior flexibilidade que os

analógicos, sendo fácil ajustar os parâmetros de controlo do conversor. A flexibilidade é igualmente notória

quando se trata de migrar os circuitos para uma outra tecnologia, bastando reprogramar o dispositivo caso o

circuito seja implementado em Processador Digital de Sinais (DSP) ou Field Programmable Gate Array (FPGA)

ou recorrer às ferramentas de síntese para redesenhar o circuito em circuitos integrados de aplicação específica

(ASIC). Os circuitos digitais são ainda menos sensíveis às variações de processo, sendo os níveis lógicos

facilmente preservados [1]. Apesar das suas inúmeras vantagens, este tipo de controladores apresenta algumas

desvantagens, desde logo o facto de não ter disponível o valor de controlo ao longo do tempo, ao contrário do

analógico. Necessita também de uma fonte de tensão separada, cuja tensão ao atingir valores abaixo de

determinado limiar compromete a operação do controlador. Os circuitos digitais implicam conversores

analógico-digital (A/D) e digital-analógico (D/A) para fazer a interface entre os dois tipos de circuitos, o que por

si traz várias implicações, como o erro associado à conversão e o facto de ser necessário redesenhar estes

circuitos cada vez que se faz a migração para outra tecnologia.

1 Introdução

3

Interessa portanto projectar os conversores A/D e D/A por forma a que o desempenho destes, nomeadamente

ao nível da precisão, rapidez e consumo, não comprometam o desempenho do controlador [2]. Este tipo de

circuitos têm vindo a sofrer, tal como o conversor CC-CC, inúmeros avanços fruto das exigências do mercado.

1.2 Objectivos de Investigação e Principais Contribuições

O objectivo deste trabalho é a busca de soluções eficientes no que toca a Conversores A/D que permitam

discretizar a diferença entre a tensão medida à saída do conversor CC-CC redutor e a tensão de referência, que

corresponde ao valor desejado na saída. Pretende-se seguir uma metodologia de projecto que conduza à

concepção de conversores A/D optimizados para serem utilizados no controlo de conversores CC-CC com

controlo digital.

O desempenho dos referidos conversores A/D prende-se com diversos aspectos. Desde logo procura-se uma

solução de baixo consumo, contribuindo assim para que o rendimento desejado para o conversor CC-CC seja

atingido. Por outro lado interessa uma comparação tão rápida quanto possível, de forma a permitir uma

resposta rápida do circuito de controlo a perturbações na tensão de saída. Outro aspecto chave que dita o

desempenho da conversão analógico-digital está relacionado a distinção inequívoca entre níveis convertidos,

minimizando o erro associado. Pretende-se igualmente projectar um conversor A/D tão preciso quanto

desejado para ser capaz de reagir a pequenas variações na tensão de saída relativamente à referência. Este

último aspecto está directamente relacionado com a tensão de desvio de entrada dos comparadores utilizados.

Há ainda a salientar os desafios impostos pelas variações possíveis quer na lei de controlo quer na frequência

de relógio do conversor CC-CC, que ditarão diferentes metodologias e diferentes especificações no que toca à

implementação do conversor A/D. Pretende-se assim implementar dois tipos de soluções diferentes, que

consistem em dois conversores A/D distintos para operar em conversores CC-CC a operar às frequências de 2 e

20 MHz.

A implementação de soluções que vão ao encontro dos objectivos impostos pela aplicação pressupõe em

primeiro lugar um estudo e caracterização de diversas topologias de comparadores, com recurso ao software

Virtuoso® da Cadence e o simulador Spectre, utilizando a tecnologia AMS 0,35µm. Tal estudo conduz à escolha

dos conversores A/D para ambos os CC-CC, implementados em tecnologia UMC 130 nm e utilizando igualmente

o software Virtuoso e o simulador HSpice. Após a validação do funcionamento de ambos os circuitos projectou-

se o layout dos mesmos, com vista a integração futura.

A Tabela 1.1 descreve as especificações de projecto para o circuito a operar a 2 MHz, enquanto que a Tabela 1.2

apresenta as especificações para 20 MHz.

Tabela 1.1 Especificações do conversor A/D para o CC-CC a 2 MHz.

Frequência Símbolo Parâmetro Mínimo Típico Máximo Unidade

2 MHz

VDD avdd

Tensão de alimentação 3.0 3.3 3.7 V

Temp Temperatura -10 25 125 oC

VREF Tensão de Referência - 1.2 - V

Iqq Consumo de Corrente - - 20 μA

N Número de níveis de discretização - 8 - -

VOS Tensão de desvio em cada uma das saídas - - 8 mV

- Intervalo entre níveis 5 10 15 mV

TP Atraso de propagação - - 50 ns

1 Introdução

4

Tabela 1.2 Especificações do conversor A/D para o CC-CC a 20 MHz.

Frequência Símbolo Parâmetro Mínimo Típico Máximo Unidade

20 MHz

VDD avdd

Tensão de alimentação 3.0 3.3 3.7 V

Temp Temperatura -10 25 125 oC

VREF Tensão de Referência - 1.2 - V

Iqq Consumo de Corrente - - 50 μA

N Número de níveis de discretização - 2 - -

VOS Tensão de desvio em cada uma das saídas - - 8 mV

- Intervalo entre níveis - 10 - mV

TP Atraso de propagação - - 10 ns

1.3 Organização da Dissertação

O presente documento está organizado de acordo com a seguinte estrutura:

Capítulo 1 – Introdução

Apresentam-se as motivações, especificações e objectivos que regem este trabalho.

Capítulo 2 – Conversores Analógico-Digital para Controlo de Conversores CC-CC

No Capítulo2 é abordada em maior detalhe a problemática dos conversores A/D para controlo de conversores

CC-CC, primeiramente de forma introdutória, depois apresentando o conversor CC-CC. Discutem-se ainda

diversas topologias de conversores A/D e comparadores como seus constituintes, desde as mais comuns até às

que constituem o estado da arte. Por fim descreve-se a solução proposta para conversores A/D a serem

aplicados em conversores CC-CC a operar a diferentes frequências.

Capítulo 3 – Implementação

Neste capítulo descreve-se primeiramente o fluxo de projecto. Depois disso apresentam-se os detalhes sobre a

implementação de cada um dos comparadores em estudo, detalhando por fim acerca da implementação dos

circuitos escolhidos com base no estudo prévio.

Capítulo 4 – Análise e Resultados

Apresentam-se neste capítulo os resultados de simulação para os diversos conversores A/D implementados,

começando por analisar os resultados obtidos aquando do estudo prévio, para depois discutir acerca dos

resultados obtidos na simulação dos circuitos a implementar.

Capítulo 5 – Layout

Abordam-se neste capítulo os detalhes do desenho do layout dos circuitos projectados, apresentando ainda os

resultados obtidos em simulação após-layout.

Capítulo 6 – Conclusões e Trabalho Futuro

Este capítulo resume os resultados obtidos, bem como as vantagens e inconvenientes da solução

implementada. Apresenta-se ainda o trabalho futuro requerido para integrar o sistema projectado no conversor

CC-CC e poder adaptar o circuito a novas exigências de projecto.

5

Capítulo 2 Conversores Analógico-Digital para

Controlo de Conversores CC-CC

Conteúdos

2.1 Introdução 6

2.2 Conversor CC-CC Redutor 6

2.3 Conversores Analógico-Digital e Comparadores 9

2.3.1 Topologias Comuns de Conversores Analógico-Digital 9

2.3.2 Topologias Comuns de Comparadores 14

2.4 Estado da Arte 15

2.4.1 Conversores Analógico-Digital 16

2.4.2 Comparadores 20

2.5 Conversores Analógico-Digital para Controlo de Conversores CC-CC 25

2.5.1 Comparador convencional rápido 27

2.5.2 Comparador misto 27

2.5.3 Comparador comutado 28

2.5.4 Comparador baseado num inversor 29

2 Conversores Analógico-Digital para Controlo de Conversores CC-CC

6

2.1 Introdução

As técnicas de controlo aplicadas aos conversores CC-CC têm vindo a evoluir de forma a adaptar o

funcionamento dos conversores para que o desempenho destes aumente. Um contributo significativo para tal

evolução prende-se com a preferência dos controlos digitais em detrimento dos analógicos. Tal solução traz

consigo a necessidade de projectar conversores A/D, conversores estes cujas topologias mais utilizadas têm

como elemento chave o comparador.

Os comparadores constituem uma das principais limitações ao nível de velocidade e precisão de sistemas de

processamento de dados, nos quais se incluem os conversores A/D. Em particular nas topologias flash e de dois

estágios os comparadores constituem o principal factor que restringe os conversores A/D [3].

Relativamente aos conversores A/D, estes podem ser implementados de acordo com diversos tipos de

arquitecturas. Tais arquitecturas apresentam inúmeras limitações e compromissos que podem inviabilizar o tão

desejado desempenho dos circuitos de controlo do conversor CC-CC [4] [3].

Desde logo verifica-se que a velocidade de conversão limita cada vez mais a resolução dos conversores. Este

facto deve-se à incerteza no instante de comutação do relógio (aperture jitter) e faz com que numa gama entre

os 2 MS/s e os 4GS/s, de cada vez que se aumenta a velocidade para o dobro, a resolução deva ser reduzida em

cerca de 1 bit [4]. A preocupação com a redução da potência dissipada pelos conversores é outro factor que

limita a resolução. Esta é uma limitação principalmente das topologias tipo flash, uma vez que o aumento da

resolução para N bits pressupõe que o circuito tenha 2N-1 comparadores. Isto traz um compromisso entre

consumo e resolução, pois um aumento da resolução conduz a um aumento da potência dissipada que

inviabiliza praticamente o uso deste tipo de soluções para aplicações com resoluções acima de 8 bits. Aumentar

o ritmo de processamento de dados implica também um aumento do consumo. Mais uma vez no caso de

topologias que usam técnicas de conversão em paralelo, como os conversores flash verifica-se que o tempo de

conversão pode ser reduzido, no entanto o seu consumo é elevado. No caso de conversores que utilizam

algoritmos de conversão sequenciais, como o de aproximações sucessivas, reduz-se o número de comparadores

mas são precisas várias iterações para concluir a operação de conversão, podendo tornar estes demasiado

lentos para aplicações com elevado ritmo de processamento de dados. As diferenças em relação ao valor

convertido face ao caso ideal são outra das preocupações quando se desenham este tipo de circuitos.

Os comparadores constituem também um factor limitativo da eficiência da conversão analógico digital, já que à

medida que o ritmo de conversão aumenta verifica-se que os comparadores têm decisões cada vez mais

ambíguas. No que toca aos comparadores existem vários tipos de circuitos a considerar, desde o mais simples,

constituído por um par diferencial com um andar de saída em malha aberta, até outras topologias mais

complexas, como por exemplo os comparadores com báscula. No caso da primeira alternativa, este tipo de

comparadores sofrem de uma elevada tensão de desvio à entrada, desvantagem à qual acresce o facto de

serem lentos a efectuar a comparação. Os comparadores com báscula, constituídos por um pré-amplificador e

um andar de báscula, ambos comandados por um sinal de relógio, surgem como resposta a tais limitações. Este

é um dos motivos que torna este tipo de comparadores preferíveis quando se projectam conversores A/D. Uma

outra vantagem que decorre da utilização de comparadores comutados é que o instante em que a decisão é

tomada é definido pelo sinal de relógio, o que permite dispensar o uso de circuitos de amostragem e retenção

[5] [3].

Todos estes aspectos levam a que se procurem soluções alternativas de modo a lidar com as exigências de

maior velocidade e resolução dos conversores sem que estes dissipem elevada potência. Tais preocupações

conduziram a um estudo cuidado de diversas técnicas de conversão A/D e de comparação que permitem a

definição de topologias que implementam conversores A/D cujas saídas são as entradas que comandam a

operação do controlo do conversor CC-CC.

2.2 Conversor CC-CC Redutor

A importância do uso de conversores CC-CC integrados, mais à frente designado apenas por CC-CC, prende-se

2 Conversores Analógico-Digital para Controlo de Conversores CC-CC

7

com diversos aspectos, desde logo porque é necessário converter a tensão das baterias dos equipamentos

portáteis na tensão adequada para alimentação dos circuitos analógicos e digitais dos actuais sistemas

integrados. A importância do estudo deste tipo de circuitos está relacionada, de acordo com [6], com os

desafios que o projecto destes conversores encerra, tais como a necessidade de regular a tensão de saída para

responder a variações quer na tensão de alimentação quer na potência na carga, a redução da componente de

tremor na tensão de saída e ainda a protecção não só dos circuitos alimentados mas também da fonte de

alimentação de entrada contra Interferência Electromagnética.

Das diversas topologias de conversores CC-CC prefere-se neste trabalho o conversor redutor, uma vez que as

baterias de iões de lítio que alimentam a maioria dos dispositivos portáteis fornece um tensão superior do que

a suportadas pelos circuitos digitais actuais. A Figura 2.1 mostra um conversor CC-CC redutor, em que sw1 e sw2

são os interruptores de potência (tipicamente dois transístores), C é um condensador e L uma bobine,

constituindo os últimos dois o filtro de saída, sendo Z a carga do conversor. A carga do conversor Z é na maioria

das aplicações um circuito electrónico alimentado pelo conversor. A corrente requerida pela carga pode variar

entre zero, situação em que o circuito está desligado, e um valor máximo que em funcionamento normal

depende da carga. A tensão VIN é fornecida por uma bateria e pode variar ao longo do tempo.

Figura 2.1 Esquema eléctrico do Conversor CC-CC Redutor.

A necessidade de minimizar a potência consumida faz com que a solução usada em implementações discretas,

para tensões superiores, de utilizar um transístor e um díodo seja preterida em detrimento do uso de dois

transístores, uma vez que, para tensões de saída baixas, o consumo de potência no díodo não é desprezável

face ao nível de potência entregue à carga. Por outro lado o facto de o díodo ser lento a comutar poderia

originar fenómenos de condução simultânea entre ambos os dispositivos de potência, originando picos de

corrente e provocando um curto-circuito entre a fonte de alimentação e a massa, o que pode danificar

significativamente o conversor. Uma vez que a condução de ambos os transístores é controlada, é possível

através do circuito de controlo limitar os fenómenos de condução simultânea.

A operação do Conversor CC-CC Redutor pode reger-se por dois modos diferentes:

Modo de Condução Contínua (MCC) – o circuito está em MCC desde que durante o período de relógio

a corrente na bobine seja sempre superior a zero.

Modo de Condução Descontínua (MCD) – este modo de operação é caracterizado por um período em

que a corrente na bobine se anula. Neste ponto a tensão de saída depende apenas da energia

armazenada no condensador. Neste modo identificam-se três estados, ao invés de dois, como ocorre

em MCC: sw1 ligado e sw2 desligado, entre t=0 e t=DT; sw1 desligado e sw2 ligado, entre t=DT e

t=D2T; ambos sw1 e sw2 desligados, entre t=D2T e t=T.

Em cada período de comutação o circuito tem dois estados, no modo de condução contínua, conforme se ilustra na Figura 2.2:

Estado Ligado – sw1 está à condução e sw2 ao corte, permitindo que a corrente na bobine aumente

devido à tensão de alimentação. Em cada período ocorre entre t=0 e t=DT, sendo D o factor de ciclo,

que varia entre 0 e 1, e T o período de relógio.

Estado Desligado – sw1 passa ao corte, conduzindo sw2, fazendo com que a corrente na bobine

decresça. Ocorre entre t=DT e t=T.

Na Figura 2.3 apresentam-se as formas de onda da corrente e tensão na bobine em cada um dos modos de

condução.

2 Conversores Analógico-Digital para Controlo de Conversores CC-CC

8

(a) (b)

Figura 2.2 Estados do Conversor CC-CC Redutor: (a) estado ligado; (b) estado desligado.

(a) (b)

(c) (d)

Figura 2.3 Comportamento do CC-CC Redutor: (a) tensão na bobine em MCC; (b) corrente na bobine em MCC; (c) tensão na bobine na MCD; (d) corrente na bobine em MCD.

As equações 2.1 e 2.2 representam a tensão na bobine e o factor de ciclo em regime permanente, respectivamente, em MCC, enquanto que na equação 2.3 é expressa a corrente na bobine, também em MCC:

(2.1)

(2.2)

(2.3)

Para o conversor a operar em MCD representam-se as mesmas grandezas, nas equações de 2.4 a 2.6.

(2.4)

onde e representa a corrente de fronteira entre os dois modos de condução.

(2.5)

com

(2.6)

2 Conversores Analógico-Digital para Controlo de Conversores CC-CC

9

A fronteira entre os dois modos de condução ocorre quando a corrente na bobine iL se anula, sendo que nesse

ponto o valor médio da corrente na saída Io é igual ao valor fronteira , como se mostra na Figura 2.4.

Figura 2.4 Corrente na bobine na fronteira entre os dois modos de condução.

O valor da corrente na bobine para o qual ocorre a fronteira entre os dois modos é expresso na equação 2.7.

com

(2.7)

2.3 Conversores Analógico-Digital e Comparadores

Apresentam-se nesta secção realizações comuns quer de conversores A/D quer de comparadores, introduzindo

o funcionamento dos mesmos.

2.3.1 Topologias Comuns de Conversores Analógico-Digital

Conversores de Duplo Declive

Os conversores integradores são bastante utilizados quando se trata de aplicações que requerem elevada

precisão sem preocupações relativas à velocidade.

(a) (b)

Figura 2.5 Funcionamento do conversor de duplo declive: (a) esquema representativo; (b) diagrama temporal.

A realização mais comum deste tipo de conversores é o conversor de duplo declive [5], cuja arquitectura é

ilustrada na Figura 2.5.O circuito funciona de acordo com duas fases. Na primeira fase, que ocorre durante um

intervalo de tempo fixo T1 determinado pela contagem do contador durante 2N ciclos, tal que T1 = 2

N TCLK, o

interruptor S1 está ligado a -Vin, de modo a que Vx sobe proporcionalmente a Vin. Na segunda fase, que decorre

num tempo variável T2., o contador é reiniciado e efectua uma nova contagem. Aí S1 é ligado a Vref, sendo que

Vx diminui com um declive constante. Para obter o valor digital na saída basta obter esta segunda contagem

que termina quando Vx atinge o valor zero.

Conversores de Aproximações Sucessivas

Esta é uma das realizações mais comuns de conversores A/D devido à sua rapidez, apesar da complexidade que

apresenta. Utiliza um algoritmo de procura binária para obter a conversão desejada. A Figura 2.6ilustra o

funcionamento genérico do conversor, que consiste em determinar sucessivamente o valor dos vários bits

começando pelo mais significativo. O sistema começa por colocar unicamente o MSB a 1 no registo e a

convertê-lo para a forma analógica através do conversor D/A, comparando-o com Vin. Este bit será fixado a 1 se

o resultado da comparação determinar que Vin é menor do que a saída do D/A nessas condições. Procedimento

2 Conversores Analógico-Digital para Controlo de Conversores CC-CC

10

semelhante é realizado para os diferentes bits, sendo que a conversão ocupa N ciclos de relógio, sendo N o

número de bits.

Figura 2.6 Esquema representativo do funcionamento do conversor de aproximações sucessivas.

Conversor Algorítmico

Este opera de forma semelhante ao conversor de aproximações sucessivas, sendo que o algoritmo de procura

se processa de acordo com o fluxograma da Figura 2.7 (b) [5], enquanto que a Figura 2.7 (a) [5] ilustra a

arquitectura do conversor.

(a) (b)

Figura 2.7 Funcionamento do conversor algorítmico: (a) arquitectura; (b) fluxograma do algoritmo de procura binária.

Conversor Sigma-Delta

Um conversor sigma-delta corrige a quantificação do sinal de entrada com base na integração do erro.

Geralmente é convertido a um ritmo elevado, mas com um número de bits menor que o necessário, usando um

conversor flash após o integrador. O sinal resultante, que inclui o erro gerado pelos níveis discretos do

conversor flash, é realimentado e subtraído à entrada gerando um sinal de erro que é integrado. Esta

realimentação negativa tem o efeito de modelar o erro devido ao conversor flash para que este não apareça

nas frequências desejadas do sinal. Um filtro digital de decimação segue o flash, reduzindo o ritmo de

amostragem e filtrando o sinal de ruído indesejável, permitindo também um aumento da resolução na saída

[7]. Na Figura 2.8 é ilustrado o seu funcionamento.

Figura 2.8 Representação do conversor sigma-delta.

2 Conversores Analógico-Digital para Controlo de Conversores CC-CC

11

Conversor Flash

Utilizam-se nesta arquitectura 2N comparadores em paralelo, como se mostra na Figura 2.9 [8], sendo que a

entrada negativa de todos eles é ligada a Vin e a entrada positiva a um divisor resistivo que transforma a tensão

de referência em Vr (2n-i). A conversão é concluída num ciclo de relógio. Como se verá mais adiante, apesar de

simples e rápido, este comparador dissipa elevada potência devido ao número de comparadores que utiliza.

Figura 2.9 Esquema que representa a arquitectura do conversor flash.

Conversor de Dois Passos

A Figura 2.10 [8] mostra o diagrama de blocos deste conversor. Consiste em dois sub-A/Ds, um para os bits mais

significativos, outro para os bits menos significativos. Primeiro são convertidos os bits mais significativos e é

armazenado o resultado, sendo que esse mesmo resultado entra num conversor D/A e é subtraído à entrada.

Esta diferença é depois amplificada e aplicada ao sub-conversor dos bits menos significativos. A conversão dos

bits menos significativos só poderá começar uma vez concluída a conversão dos mais significativos, o que é feito

à custa de um circuito de amostragem e retenção. Isto faz com que a conversão ocupe dois ciclos de relógio, no

entanto diminui o número de comparadores para cerca de metade quando comparado com o conversor flash.

Figura 2.10 Representação da arquitectura do conversor de dois passos.

Conversor Folding

Este tipo de arquitectura é semelhante à do conversor de dois passos, no entanto neste caso os LSB são

determinados usando processamento analógico, enquanto os MSB são determinados ao mesmo tempo. Em

primeiro lugar determina-se a quantidade de bits a serem convertidos pelo sub-A/D dos MSB e determina-se

em que nível de tensão estes se encontram. Os LSB são calculados no sub-A/D correspondente e geram um

código termómetro diferente consoante os níveis detectados, como se ilustra na Figura 2.11 [8].

Figura 2.11 Representação do conversor folding.

2 Conversores Analógico-Digital para Controlo de Conversores CC-CC

12

Conversor de Interpolações

Para reduzir o número de comparadores utilizados no conversor flash surge esta topologia que quantifica a

diferença entre a entrada analógica e a tensão de referência na saída de cada pré-amplificador. Assumindo que

cada pré-amplificador não tem tensão de desvio à entrada, verifica-se na Figura 2.12 [9] que se Vin=Vr1 então

Vx1=VY1 e Vx2=VY2 quando Vin=Vr2. Mais importante ainda, quando Vin=(Vr1+Vr2)/2 a diferença entra Vx1 e Vy1 tem

a mesma polaridade que a diferença entre Vin e Vm.

Conversor Pipelined

A topologia mais básica de tipo de conversor, apresentada na Figura 2.13, utiliza um estágio por cada bit, sendo

que no primeiro estágio é convertido o bit mais significativo num conversor de 1 bit. Este valor é armazenado

num registo e também convertido num Conversor D/A, conversor esse cuja saída é a entrada do estágio

seguinte e assim sucessivamente até ao último estágio em que se converte o bit menos significativo [8].

Figura 2.13 Esquema representativo do conversor pipelined.

Conversor Intervalado no Tempo

No caso da Figura 2.14 [8], em que se apresenta um conversor de 4 canais, este opera segundo 4 fases

diferentes, sendo que cada um dos circuitos de amostragem e retenção operam com sinais de relógio

diferentes: Ф0 tem quatro vezes a frequência de Ф1 a Ф4. Estes últimos quatro sinais controlam a operação de

cada um dos conversores A/D. Cada conversor processa individualmente um quarto da gama do sinal.

Figura 2.14 Representação do conversor intervalado no tempo.

Conversor de Acompanhamento com Contador

Apresenta-se agora o conversor de acompanhamento baseado num contador. O seu funcionamento rege-se de

(a) (b)

Figura 2.12 Conversor de interpolações: (a) arquitectura; (b) característica de transferência.

2 Conversores Analógico-Digital para Controlo de Conversores CC-CC

13

acordo com o seguinte: o contador, actuado pelo sinal de relógio, irá ser incrementado ou decrementado,

conforme a saída do comparador tenha o valor lógico “1” ou “0”, respectivamente, sendo a sua saída a saída do

conversor A/D e também a entrada do conversor D/A, como ilustra o diagrama da Figura 2.15 [9]. Este

conversor é, segundo [9], bastante rápido quando se trata de acompanhar pequenas variações do sinal de

entrada. No entanto, se estas variações se tornarem acentuadas entre sucessivas operações de conversão, a

rapidez da sua resposta degrada-se bastante.

Figura 2.15 Representação do conversor de acompanhamento com contador.

Conversor de Acompanhamento com Janela

Este tipo de conversor é baseado geralmente num comparador que estabelece em que janela se encontra a

tensão de entrada em relação à tensão de saída, para que, e sabendo os seus níveis superior e inferior, possa

ajustar a característica do comparador, permitindo que a janela de saída deste acompanhe as variações da

tensão de entrada. Isto é geralmente realizado à custa de uma lógica de controlo assíncrono e de um

quantizador que quantifica a diferença entre a tensão de entrada e o valor de referência, permitindo que,

através do conversor D/A, a característica do comparador seja alterada [10] [11]. A Figura 2.16 ilustra uma

realização comum para este tipo de conversor.

Figura 2.16 Esquema representativo do conversor de acompanhamento com janela.

Análise comparativa

As várias realizações apresentadas diferem entre si de acordo com vários critérios. As topologias do tipo

paralelo, como por exemplo o flash, são bastante rápidas e apresentam uma latência baixa, isto é, não

necessitam de um número elevado de ciclos de relógio para processar cada conversão. No entanto, devido ao

elevado número de elementos de circuito que necessitam, maioritariamente comparadores, o seu consumo é

elevado, o que é deveras desvantajoso para a aplicação ao conversor CC-CC com controlo digital, uma vez que o

consumo dos circuitos de controlo terá que ser baixo para não comprometer o rendimento. Conversores que

utilizam técnicas de conversão sequenciais, como o pipelined e o conversor de aproximações sucessivas,

permitem atingir resoluções médias a elevadas, no entanto a sua latência pode comprometer a utilização neste

tipo de aplicações. O conversor de acompanhamento com janela pode ser uma alternativa válida para a

aplicação em estudo, já que tratando-se de um conversor assíncrono pode atingir um ritmo de conversão

adequado.

2 Conversores Analógico-Digital para Controlo de Conversores CC-CC

14

2.3.2Topologias Comuns de Comparadores

Os comparadores são, depois dos amplificadores, dos circuitos mais utilizados no mundo da electrónica. São

circuitos utilizados para discriminar se uma determinada tensão é maior ou menor que uma outra [5]. Uma das

suas maiores aplicações é em conversores analógico-digital. Segue-se uma abordagem a diversas arquitecturas

de comparadores.

Par diferencial como Comparador

Uma perspectiva bastante simples sobre a forma como se podem realizar comparadores prende-se com o uso

de um par diferencial simples tal como se mostra na Figura 2.17. O comparador pode ser inversor ou não

inversor, conforme a tensão de referência VREF esteja ligada à entrada positiva ou à entrada negativa do

amplificador, respectivamente. Este circuito apesar de bastante simples sofre de dois problemas que podem

comprometer a sua utilização nos conversores A/D de uso comum hoje em dia: sofre de tensão de desvio à

entrada e tem um ganho muito baixo.

No caso de um comparador com par diferencial MOS e carga activa, como o da Figura 2.17, a tensão de desvio à

entrada deve-se a dois tipos de assimetrias: variação das tensões de limiar (Vt) ou da razão W/L (em que W

representa o comprimento de canal e L a largura do canal) dos transístores do par diferencial; variação da razão

W/L nos transístores da carga [9].

Um outro efeito que, dependendo da aplicação, pode ser indesejado não só neste tipo de comparadores,

prende-se com a histerese. No entanto este efeito pode ser propositadamente adicionado para garantir maior

imunidade ao ruído. A existência de histerese faz com que a característica do comparador passe a ser de acordo

com a Figura 2.18, significando isto que a decisão do comparador nem sempre ocorre no mesmo valor da

tensão de entrada e depende do declive da tensão de entrada em relação ao tempo.

Figura 2.17 Par diferencial em malha aberta.

Figura 2.18 Característica em repouso do comparador: (a) sem tensão de desvio; (b) com tensão de desvio à entrada.

Figura 2.19 Característica temporal de um comparador com histerese.

2 Conversores Analógico-Digital para Controlo de Conversores CC-CC

15

Para aumentar o ganho deste tipo de comparadores pode optar-se por uma solução que consiste em ligar a

carga a espelhos de corrente conforme a Figura 2.20, de forma a efectuar a saída do par diferencial em

corrente. O circuito baseia-se num amplificador de transcondutância simétrico [12] em malha aberta. O mesmo

propósito pode justificar o uso de inversores na saída [13].

Figura 2.20 Esquema eléctrico do comparador rápido.

Comparadores com báscula

Este tipo de comparadores surge como resposta à baixa velocidade de decisão dos comparadores ditos

convencionais, analisados na sub-secção anterior. Tipicamente estes comparadores têm três andares: um de

pré-amplificação, um de báscula e finalmente um registo de saída, e a sua operação é comandada por um sinal

de relógio, conforme a Figura 2.21 [9].

Figura 2.21 Esquema representativo do comparador comutado.

O seu funcionamento decorre de acordo com duas fases, tal que numa primeira fase, chamada de fase de

amplificação, pré-carga ou reset, o relógio está a 0 e os nós de saída são ligados a 1 ou 0, conforme a

arquitectura, e a diferença entre Vin e Vref é amplificada e armazenada na entrada da báscula. Na fase posterior,

de decisão ou comparação, quando o relógio vem a 1, a báscula (latch), geralmente constituída por dois

inversores costas-com-costas, tenderá a comutar no sentido que reforça a diferença da pré-carga recebida,

devido à forte realimentação positiva. Este tipo de circuitos requer normalmente o uso de latchs do tipo S-R

para manter o valor comparado na saída durante a fase de pré-carga seguinte.

Relativamente aos comparadores convencionais, os comparadores com báscula são consideravelmente mais

rápidos., No entanto o seu consumo pode ser mais elevado devido ao elevado número de comutações ditadas

pelo relógio do circuito. Um requisito importante nestes comparadores consiste em garantir que não haja

fenómenos de condução simultânea quando se comuta o circuito entre as diferentes fases. No que toca à

tensão de desvio à entrada, os comparadores comutados continuam a sofrer de tal limitação, sendo necessário

na maioria das aplicações efectuar a sua compensação, acontecendo o mesmo com os comparadores

convencionais. Em algumas aplicações a principal desvantagem do comparador comutado face ao convencional

decorre do facto de o primeiro necessitar de um relógio com uma frequência tal que permita efectuar

comparações com o ritmo desejado [14].

2.4 Estado da Arte

Nesta secção discutem-se diversas implementações de conversores A/D e comparadores que constituem o

estado da arte em ambas as matérias. Saliente-se que as topologias apresentadas são realizações das

arquitecturas apresentadas anteriormente.

2 Conversores Analógico-Digital para Controlo de Conversores CC-CC

16

2.4.1 Conversores Analógico-Digital

Diferentes realizações têm vindo a ser exploradas, como é o caso do conversor de aproximações sucessivas com

12 bits, de Fotouhi e Hodges [15]. Este combina um paralelo de K condensadores e outro de M resistências para

atingir uma resolução de M+K bits, sendo cada um destes elementos controlado por um interruptor, tal como é

sugerido na Figura 2.22. Segue-se um interruptor e o circuito digital que controla os interruptores. A tensão de

entrada é primeiro amostrada e retida nos condensadores. Depois é realizada através das resistências a procura

sucessiva, até que a sequência obtida é armazenada nas placas dos condensadores, no final da conversão.

Figura 2.22 Esquema simplificado do conversor A/D de aproximações sucessivas de Fotouhi e Hodges.

Figura 2.23 Esquema conceptual do conversor de 3 bits do conversor de aproximações sucessivas de Hamdé.

Hamadé [16] projecta um conversor de 8 bits utilizando uma série de duzentas e cinquenta e seis resistências

de igual valor seguidas de uma matriz de quinhentos e dez interruptores analógicos e por fim um comparador.

Este circuito pretende implementar um conversor A/D de aproximações sucessivas. A condução dos

interruptores é controlada por 8 sinais de controlo e pelos mesmos sinais negados. A conversão ocorre numa

sequência de 8 operações que permite seleccionar a adequada de entre todas as 512 combinações possíveis

2 Conversores Analógico-Digital para Controlo de Conversores CC-CC

17

das várias resistências. A Figura 2.23 [16] ilustra o funcionamento de um conversor de 3 bits utilizando a mesma

técnica. Comparando ambas as técnicas verifica-se que em [15] consegue-se uma economia ao nível da área

ocupada pelo conversor face a [16], acrescendo o facto de o conversor projectado em [15] dispor de uma

resolução superior.

Com vista a conseguir um aumento de velocidade e tirar partido das vantagens do processamento paralelo, não

abdicando de uma resolução média, é projectado em [17] um conversor de aproximações sucessivas que dispõe

de várias células que implementam cada uma um Conversor A/D de aproximações sucessivas com 10 bits, tal

como se mostra na Figura 2.24. Combinando várias células em paralelo a velocidade do comparador aumentará

proporcionalmente ao número de células colocadas em paralelo. Cada célula é constituída por um circuito de

amostragem e retenção, que evita tensões de desvio nas fontes, um comparador e um registo de

deslocamento. É necessário ainda um conversor D/A de dois passos, um de conversão fina e um outro de

conversão com menor resolução, que consistem num divisor resistivo, servindo para gerar a tensão de

referência. Quando comparada esta solução com as apresentadas em [16] e [15] verifica-se que o aumento da

velocidade de processamento conduz a um aumento do consumo.

Figura 2.24 Ilustração do princípio de funcionamento do conversor de aproximações sucessivas com várias células.

Em [18] concebe-se um Conversor A/D de aproximações sucessivas ilustrado na Figura 2.25(a). Como este

conversor será usado numa aplicação de pó inteligente, a maior preocupação é o consumo de energia que deve

ser bastante reduzido, podendo-se sacrificar a rapidez de conversão em função disso, pelo que o

processamento pode ser sequencial, ao contrário de [17]. O conversor utiliza um único comparador que é

ligado a um microprocessador e uma rede de interruptores que permite através de um circuito digital

implementar o algoritmo de procura binária. O circuito compreende ainda um conjunto de condensadores,

cada um com o peso binário correspondente, que permite converter o valor de cada aproximação numa tensão

que será depois comparada na iteração seguinte com a referência.

(a) (b)

Figura 2.25 (a) Arquitectura do conversor para aplicações de pó inteligente 8 bits; (b) arquitectura do conversor sigma-delta contínuo no tempo.

O conversor sigma-delta contínuo no tempo, com 4 bits, é apresentado em [19]. Este conversor dispõe de um

filtro de terceira ordem que suprime o ruído de quantização na fronteira da banda do sinal, dispondo ainda de

um conversor A/D de acompanhamento com três comparadores, cujo esquema simplificado se apresenta na

Figura 2.25 (b). Este último contém três comparadores, um divisor resistivo, um contador e uma matriz de

interruptores. Para pequenas variações do sinal de entrada apenas o comparador do meio reage e não há

2 Conversores Analógico-Digital para Controlo de Conversores CC-CC

18

qualquer variação no contador nem nas tensões de referência dos restantes comparadores. Para variações

maiores todos os comparadores actuarão, sendo incrementado ou decrementado o contador, fazendo com que

as tensões de referência, controlados por interruptores, sigam a variação do sinal de entrada, permitindo nova

conversão.

Em [11] utiliza-se uma técnica de acompanhamento desta vez baseada num quantizador de diferença, sendo o

conversor A/D assíncrono. O quantizador de diferença que determina a diferença entre a tensão de entrada e a

referência, determinado se o contador incrementa ou decrementa. O resultado de cada contagem determina

em que nível se encontra o sinal de entrada face à referência, sendo este depois convertido num conversor D/A,

para que o resultado de cada conversão possa ser compatível com o quantizador. Face aos conversores

projectados em [18] e [19] este conversor permite uma maior eficiência no que toca ao consumo. A

arquitectura utilizada representa-se na Figura 2.26.

Figura 2.26 Esquema do conversor A/D de acompanhamento de 4 bits implementado por Allier et al.

(a) (b)

Figura 2.27 Conversor flash de elevada velocidade: (a) esquema representativo da arquitectura; (b) comparador.