Decodificador de 7 Segmentos_v7 (Rafael)

-

Upload

rafaelcampello -

Category

Documents

-

view

51 -

download

16

description

Transcript of Decodificador de 7 Segmentos_v7 (Rafael)

UNIVERSIDADE ESTÁCIO DE SÁ

José Ricardo Silva - 201301140856

Reinaldo da Silva Itaborai - 201201582962

Rafael Braga Campello - 201201405131

Thiago Russo Dias - 201201299128

Professor: ODAIR DA SILVA XAVIER

CIRCUITOS COMBINACIONAIS – PRÁTICA 5

DECODIFICADOR NAND PARA DISPLAY DE 7 SEGMENTOS

Rio de Janeiro, 24 de novembro de 2014.

SUMÁRIO

1. INTRODUÇÃO ................................................................................................................. 1

2. OBJETIVO ........................................................................................................................ 1

3. DESENVOLVIMENTO ................................................................................................... 2

3.1. MATERIAL UTILIZADO ................................................................................................ 2

3.2. PROCEDIMENTO EXPERIMENTAL ................................................................................ 2

4. CONCLUSÃO ................................................................................................................. 18

5. REFERÊNCIAS BIBLIOGRÁFICAS .......................................................................... 19

1

1. INTRODUÇÃO

O display de 7 segmentos é utilizado na eletrônica digital para exibir as informações

em linguagem de máquina as convertendo para linguagem humana, em outras palavras, o

display fornece informações binárias de forma decimal, tornando fácil para o ser humano

interpretar determinado comportamento eletrônico. O display de 7 segmentos é composto por

oito diodos LED e podem ser catodo comum ou anodo comum conforme Figura 1 e cada

diodo LED corresponde a um segmento denominados de a, b, c, d, e, f, g e dp (decimal point)

[1].

Figura 1 – Exemplificação interna de um display de 7 segmentos.

Para que o display de 7 segmentos exiba os valores binários do circuito digital de

forma decimal, necessita-se decodificar o código binário BCD8421 para o código decimal.

Existem diversas maneiras simples para decodificar o código BCD8421, como por exemplo,

podem ser utilizados um dos circuitos integrados 74LS47, 74LS48 ou CD4511 [2].

Nesta prática serão utilizados apenas circuitos integrados de operações NAND com

portas de no máximo duas entradas para decodificar o código BCD8421 ao invés de utilizar

um simples circuito integrado decodificador como 74LS47.

2. OBJETIVO

Tem-se como proposta nesta prática verificar o funcionamento de um circuito

decodificador do código BCD8421 projetado utilizando circuitos integrados da família TTL

com portas lógicas de operações NAND utilizando as técnicas de simplificação pelo Mapa de

Karnaugh e De Morgan, além de exercer as práticas de criação e montagem de circuito em

placa de circuito impresso (PCI) com o auxílio de softwares simuladores de circuito e

geradores de layout para PCI.

2

3. DESENVOLVIMENTO

3.1. Material utilizado

O material utilizado na prática está descrito na Tabela 1 abaixo.

Material utilizado

Quantidade Equipamento ou componente

13 CI 74LS00 (NAND)

1 Placa de fenolite 15x10 cm

13 Soquete DIL de 14 terminais

1 Display de 7 segmentos catodo comum

7 Resistores de 220 Ω

1 Percloreto de ferro (400g)

1 Bobina de solda

1 Ferro de soldar

1 Furadeira com broca de 1 mm

1 Chave SPST de 4 contatos

Tabela 1 – Lista de material utilizado para prática com circuito decodificador de sete segmentos.

3.2. Procedimento experimental

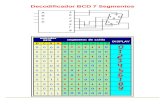

Para obter as expressões lógicas necessárias para converter determinados valores

binários nos valores decimais desejados foi utilizada a Tabela 2 que relaciona o código

binário BCD8421 (porque o display de 7 segmentos é capaz de exibir apenas os valores de 0 a

9) com os valores decimais, como por exemplo, 00002 equivale a 010 e 10012 equivale a 910.

Decimal BCD8421 Display de 7 segmentos

A B C D a b c d e f g

0 0 0 0 0 1 1 1 1 1 1 0

1 0 0 0 1 0 1 1 0 0 0 0

2 0 0 1 0 1 1 0 1 1 0 1

3 0 0 1 1 1 1 1 1 0 0 1

4 0 1 0 0 0 1 1 0 0 1 1

5 0 1 0 1 1 0 1 1 0 1 1

6 0 1 1 0 0 0 1 1 1 1 1

7 0 1 1 1 1 1 1 0 0 0 0

8 1 0 0 0 1 1 1 1 1 1 1

9 1 0 0 1 1 1 1 0 0 1 1

10 1 0 1 0 x x x x x x x

11 1 0 1 1 x x x x x x x

12 1 1 0 0 x x x x x x x

13 1 1 0 1 x x x x x x x

14 1 1 1 0 x x x x x x x

15 1 1 1 1 x x x x x x x

3

Tabela 2 – Tabela de relação entre BCD8421 e a representação decimal do display.

Observando que há na Tabela 2 uma coluna para cada segmento que será utilizado no

display para exibir os valores de 0 a 9 e não é necessário utilizar o segmento Decimal Point,

portanto foram criadas apenas 7 colunas, que representam 7 saídas em nosso circuito. Ao

analisar a Figura 1 novamente, podemos observar qual segmento deve emitir luz para

representar um número desejado, como por exemplo, para representar o número 1, apenas os

segmentos b e c devem emitir luz. As colunas que representam os segmentos do display de 7

segmentos na Tabela 2 foram preenchidas seguindo esta lógica, valor 1 significa que o

segmento deve emitir luz, e valor 0 significa que o segmento deve permanecer apagado, e

valor “x” significa que resultado “não importa” ou “don’t care”.

Em seguida foi utilizado o método do mapa de Karnaugh para obter as expressões

booleanas dos sinais de entrada ABCD para cada saída (a, b, c, d, e, f, g).

4

Figura 3 – Mapas de Karnaugh para cada segmento do display de 7 segmentos e as expressões de boole para

cada saída.

Nota-se que as expressões obtidas pelos Mapas de Karnaugh representados na Figura

3 indicam expressões que utilizam operações lógicas OR, AND e INVERSÃO. Tendo como

objetivo nesta prática utilizar apenas operações lógicas NAND, foi utilizado o Teorema de De

Morgan para obter as expressões descritas nas equações abaixo:

Equação 1 – Saída do segmento a apenas com operações NAND.

Equação 2 – Saída do segmento b apenas com operações NAND.

Equação 3 – Saída do segmento c apenas com operações NAND.

Equação 4 – Saída do segmento d apenas com operações NAND.

Equação 5 – Saída do segmento e apenas com operações NAND.

Equação 6 – Saída do segmento f apenas com operações NAND.

Equação 7 – Saída do segmento g apenas com operações NAND.

Para verificar de modo rápido e eficaz a veracidade dos resultados das expressões

obtidas com os Mapas de Karnaugh e Teorema de De Morgan foi utilizado o simulador

Logisim Win 2.7.1 [3] para criar o circuito da Figura 4. Com o simulador foi possível atribuir

combinações de valores de nível lógico alto ou baixo nas entradas ABCD e verificar que os

resultados em valores decimais foram satisfatórios através do display de 7 segmentos.

5

Figura 4 – Circuito Decodificador de BCD8421 para Display de 7 Segmentos no simulador Logisim Win.

Observe na Figura 4 que determinadas portas lógicas possuem muitas ligações em

seus terminais de saída para até 10 entradas de outras portas lógicas. O circuito funcionou

perfeitamente no simulador, mas gera a dúvida se realmente funciona na prática, pelo motivo

de uma saída estar alimentando tantas entradas. Para eliminar esta dúvida, foram realizados

cálculos de fan-out para saída da porta lógica NAND.

6

Está descrito em algumas literaturas [4] que o fan-out do CI 74LS00 para a saída é 10,

ou seja, pode alimentar até 10 entradas lógicas padrão. O fan-out, também chamado de fator

de carga, é definido como o número máximo de entradas de circuitos lógicos que uma saída

pode alimentar de maneira confiável [5].

Para determinar quantas entradas diferentes a saída de um CI pode alimentar,

precisamos conhecer o IOL (máx) e IOH (máx) de tal CI e as necessidades de corrente de cada

entrada, IIL e IIH para satisfazer a Equação 8 e Equação 9 abaixo:

Equação 8 – Relação entre corrente máxima de saída para nível lógico baixo e corrente máxima de

entrada para nível lógico baixo.

Equação 9 – Relação entre corrente máxima de saída para nível lógico ALTO e corrente máxima de

entrada para nível lógico alto.

As características [6] utilizadas como base de dados para os cálculos de fan-out foram

da FARCHILD SEMICONDUCTORTM conforme Figura 5, obtendo os resultados da

Equação 10 e Equação 11.

Figura 5 – Características Elétricas do CI 74LS00 de acordo com a FARCHILD SEMICONDUCTORTM.

Equação 10 – Resultado do fan-out (baixo).

Equação 11 – Resultado do fan-out (alto)

Com os resultados obtidos, fica confirmado que uma saída do CI 74LS00 pode-se

alimentar no máximo 20 entradas lógicas [7].

7

A informação teórica de que uma saída do CI 74LS00 pode alimentar de maneira

confiável até 20 entradas lógicas de outros CI de mesmo modelo ainda não é suficiente para

garantir que o circuito funcionará normalmente na prática, portanto, um circuito que utiliza a

saída de uma porta lógica para controlar 10 entradas lógicas foi montado na matriz de

contatos conforme a Figura 6 e o seu funcionamento foi verificado provando que uma saída

do CI 74LS00 pode alimentar 10 entradas lógicas, não foi realizado teste com mais entradas,

pois não há aplicação neste projeto.

Figura 6 – Circuito montado na matriz de contatos demonstrando que uma saída pode alimentar 10 entradas.

Para não danificar os segmentos do display deve ser inserido em série com cada

terminal do display um resistor para limitar a corrente. Foi utilizado um resistor de 220 Ω

cada segmento, este valor de resistência é o dobro da resistência necessária e foi escolhido

porque é um valor de resistência ideal para garantir a emissão de luz considerável e também

não se aproximar dos limites do display conforme Equação 12 de acordo com as

características do datasheet [8]. O display de 7 segmentos utilizado é o C-551H do fabricante

ParaLight e possui consumo de corrente de 10 mA e queda de tensão direta Vf de 2.3 V.

Equação 12 – Limitador de corrente para display de 7 segmentos.

Seguindo a norma IPC-2221 [9] para padronização de placas de circuito impresso da

IPC ASSOCIATION CONNECTION ELECTRONICS INDUSTRIES® e com auxílio do

8

software Electrodroid [10] foi determinado a largura da trilha da placa de circuito deve ser de

4,722 µm para uma corrente máxima de 100 mA, temperatura do ambiente até 50°C e

espessura do cobre de 35 µm. A corrente máxima utilizada garante uma margem de segurança

muito alta porque cada CI consome no máximo 4,4 mA de acordo com o datasheet [6]

totalizando 57,2 mA de consumo porque o circuito possui 13 circuitos integrados. Com estas

informações a largura da trilha da placa de circuito impresso deixa de ser uma preocupação,

porque os softwares utilizados para gerar o layout da placa de circuito impresso (PCI)

utilizam no mínimo trilhas de 250 µm.

O projeto definitivo do circuito digital decodificador do código BCD8421 para display

de 7 segmentos foi desenhado no simulador Proteus, propriedade da Labcenter Electronics

[11] seguindo as especificações para layout de PCI fornecidas pela Giga Eletrônica Ltda.

[12]. Como pode ser observado na Figura 7 as especificações determinam: menor tamanho de

ilha de 50 mils, isolação entre trilhas de 10 mils (foi utilizado 40 mils), menor largura de

trilha de 10 mils (foi utilizado 15 mils), isolação entre ilhas de 10 mils, isolação entre trilhas e

ilhas de 10 mils (foi utilizado 40 mils) e distância entre trilhas e a borda da placa de 12 mils.

O mil é a mínima unidade de comprimento no sistema de medidas no padrão dos Estados

Unidos e equivale a 0,0254 milímetros ou 0,001 polegada. Esta unidade foi originada da

unidade milésimo de uma polegada (Thou) do sistema imperial de unidades [13].

Figura 7 – Especificações para layout de PCI fornecidos pela Giga Eletrônica Ltda.

O layout da placa de circuito impresso foi criado utilizando uma placa de fenolite com

face dupla de cobre com 150 mm de largura e 100 mm de altura devido a alta quantidade de

circuitos integrados interligados utilizados no circuito. A confecção de uma placa de circuito

impresso dupla face exige determinadas tecnologias para confecção de PCI difíceis de

reproduzir de forma caseira, portanto os layouts foram enviados para cotação em inúmeras

empresas de confecção de PCI. Os prazos para confecção de PCI com face dupla de cobre são

de aproximadamente 10 dias de acordo com empresas contatadas, este prazo é alto porque a

placa de circuito dupla face exige a utilização da tecnologia de furação metalizada que garante

o contato elétrico entre as ilhas em ambas as faces da placa. Este prazo não atende a data de

entrega do projeto, portanto, foi criado um novo layout de PCI utilizando uma placa de face

simples de 150 mm de largura e 100 mm de altura para confecção caseira, a grande

desvantagem é a grande necessidade da utilização de fios jumper para compensar a

inexistência de outra face no circuito. O software utilizado para gerar o layout da PCI de face

simples foi o PCB Wizard da New Wave Concepts [14] devido à facilidade de adicionar fios

jumper no circuito. Todos os diagramas e layouts podem ser vistos nas próximas páginas

conforme as imagens da Figura 8 até a Figura 14.

9

Figura 8 – Diagrama do circuito digital decodificador do código BCD8421 para um display de 7 segmentos.

10

Figura 9 – Visualização em 3 dimensões gerada pelo Proteus do lado superior e inferior da placa de circuito

impresso dupla face.

11

Figura 10 – Visualização das trilhas do lado superior da placa de circuito impresso dupla face.

Figura 11 – Visualização das trilhas do lado inferior da placa de circuito impresso dupla face.

12

Figura 12 – Visualização de “mundo real” do circuito decodificador em placa de face simples de 150 x 100 mm.

Figura 13 – Layout do circuito decodificador em placa de face simples de 150 x 100 mm.

13

Figura 14 – Visualização das trilhas do circuito decodificador em placa de face simples de 150 x 100 mm.

A alta quantidade de fios jumper para montagem do circuito em placa de face simples

prejudicou severamente a aparência da placa e dificultou demasiadamente o procedimento de

montagem assim como a visualização do circuito para o fim de verificar falhas e corrigi-las.

Foram necessárias dezenas de horas para finalização da montagem da placa de circuito

impresso em placa de face simples e o resultado foi insatisfatório. O display de 7 segmentos

apenas emite luz indicando um caractere indefinido parecido com o número decimal 3 como

pode ser visto na Figura 15.

Figura 15 – Circuito decodificador do código BCD8421 para um display de 7 segmentos montado em placa de

circuito impresso de face simples de 150 x 100 mm.

14

Observe na Figura 16 o aspecto indesejado causado pela altíssima quantidade de fios

jumper na parte inferior da placa de circuito impresso.

Figura 16 – Lado inferior da PCI do circuito decodificador do código BCD8421 para um display de 7 segmentos.

Foram obtidos resultados satisfatórios através da montagem do circuito na matriz de

contatos conforme visto anteriormente na Figura 6 e também através do simulador Proteus

conforme as imagens seguintes da Figura 17 até a Figura 26. Apesar do circuito

decodificador não ter operado como deveria ao ser montado na placa de circuito impresso

Figura 17 – Recorte do simulador Proteus do circuito decodificador utilizando 13 CI com portas NAND de duas

entradas utilizando sinal de entrada para ABCD = 0000.

Figura 18 – Recorte do simulador Proteus do circuito decodificador utilizando 13 CI com portas NAND de duas

entradas utilizando sinal de entrada para ABCD = 0001.

15

Figura 19 – Recorte do simulador Proteus do circuito decodificador utilizando 13 CI com portas NAND de duas

entradas utilizando sinal de entrada para ABCD = 0010.

Figura 20 – Recorte do simulador Proteus do circuito decodificador utilizando 13 CI com portas NAND de duas

entradas utilizando sinal de entrada para ABCD = 0011.

Figura 21 – Recorte do simulador Proteus do circuito decodificador utilizando 13 CI com portas NAND de duas

entradas utilizando sinal de entrada para ABCD = 0100.

16

Figura 22 – Recorte do simulador Proteus do circuito decodificador utilizando 13 CI com portas NAND de duas

entradas utilizando sinal de entrada para ABCD = 0101.

Figura 23 – Recorte do simulador Proteus do circuito decodificador utilizando 13 CI com portas NAND de duas

entradas utilizando sinal de entrada para ABCD = 0110.

Figura 24 – Recorte do simulador Proteus do circuito decodificador utilizando 13 CI com portas NAND de duas

entradas utilizando sinal de entrada para ABCD = 0111.

17

Figura 25 – Recorte do simulador Proteus do circuito decodificador utilizando 13 CI com portas NAND de duas

entradas utilizando sinal de entrada para ABCD = 1000.

Figura 26 – Recorte do simulador Proteus do circuito decodificador utilizando 13 CI com portas NAND de duas

entradas utilizando sinal de entrada para ABCD = 1001.

18

4. CONCLUSÃO

A quantidade de circuitos integrados da família TTL com operação NAND que é

necessária para executar a função de um decodificador do código binário BCD8421 para o

código decimal através de um display de 7 segmentos pode variar porque depende da

simplificação das expressões lógicas obtidas através do Mapa de Karnaugh ou do Teorema de

De Morgan para cada saída podendo definir um circuito com dezesseis circuitos integrados

7400 ou apenas treze circuitos integrados, como foi utilizado nesta prática. Esta quantidade

também pode variar dependendo do CI com operação NAND escolhido, a quantidade de CI

utilizados poderia ter sido reduzida com a utilização de portas lógicas com mais entradas,

como por exemplo, 7410 com três portas NAND de três entradas, 7420 com duas portas

NAND de quatro entradas ou 7430 com uma porta NAND de oito entradas [15].

A montagem de um circuito que utiliza uma alta quantidade de circuitos integrados

com uma grande quantidade de interligações entre si é muito complicada de ser realizada

utilizando uma placa de circuito impresso de face simples e acaba se tornando inviável, a

quantidade mínima de fios jumper necessários para completar as ligações do circuito em uma

placa de face simples foi de 47 fios jumper mesmo utilizando as espessuras mais finas e

espaçamentos mais estreitos permitidos pelas especificações das empresas fabricantes de

placas de circuito impresso.

Os objetivos propostos por esta prática foram todos atingidos uma vez que foi definido

que um decodificador do código BCD8421 pode ser criado de várias maneiras utilizando

portas lógicas ou utilizando apenas portas lógicas de operação NAND demonstrando a origem

dos circuitos integrados como 74LS47, 74LS48 ou CD4511.

19

5. REFERÊNCIAS BIBLIOGRÁFICAS

1. DO BIT AO BYTE. Eletrônica digital - Display 7 segmentos com 74HC595. Disponível

em: <http://www.dobitaobyte.com.br/arduino/eletronica-digital-display-7-segmentos-

com-74hc595>. Acesso em: 22/10/2014.

2. ELECTRONICS LAB. BCD Decoders to seven segments displays (74LS47, 74LS48,

CD4511). Disponível em: <http://electronicslab.eu/en/digital-electronics/379-bcd-

decoders-to-seven-segments-displays-74ls47-74ls48-cd4511.html>. Acesso em:

22/10/2014.

3. CBURCH. Logisim. Disponível em: <http://www.cburch.com/logisim/pt/index.html>.

Acesso em: 22/10/2014.

4. CORRADI. Sistemas Digitais - Módulo 5 - Como calcular o FAN-OUT. Disponível

em: <http://pt.scribd.com/doc/44005511/Como-Calcular-o-FAN-OUT>. Acesso em:

22/10/2014.

5. DE LIMA, José Antônio Gomes. Circuitos Integrados e Famílias Lógicas. Disponível

em: <http://www.di.ufpb.br/jose/familias.pdf>. Acesso em: 22/10/2014.

6. FARCHILD SEMICONDUCTOR. DM74LS00 Datasheet. Disponível em:

<http://pdf.datasheetcatalog.com/datasheets/70/232209_DS.pdf>. Acesso em: 22/10/2014.

7. BEREIT, Mark. 74LS00 Family. Disponível em:

<www.markbereit.com/rsrc/ccdig_74ls.html>. Acesso em: 22/10/2014.

8. PARALIGHT. C551H Datasheet. Disponível em:

<http://doc.chipfind.ru/pdf/para/c551.pdf>. Acesso em: 22/10/2014.

9. IPC ASSOCIATION CONNECTING ELECTRONICS INDUSTRIES. IPC 2221A.

Disponível em:

<http://sisko.colorado.edu/CRIA/FILES/REFS/Electronics/IPC_2221A.pdf>. Acesso em:

22/10/2014.

10. IERO. ElectroDroid. Disponível em: <http://electrodroid.it/>. Acesso em: 22/10/2014.

11. LABCENTER Electronics. Proteus. Disponível em:

<http://www.labcenter.com/index.cfm>. Acesso em: 22/10/2014.

12. GIGA Eletronica. Confecção de placas de circuito impresso. Disponível em:

<http://www.gigaeletronica.com.br/>. Acesso em: 22/10/2014.

13. WIKIPEDIA, The Free Encyclopedia. Thousandth of an inch. Disponível em:

<http://en.wikipedia.org/wiki/Thousandth_of_an_inch>. Acesso em: 22/10/2014.

14. NEW WAVE CONCEPTS. PCB Wizard. Disponível em: <http://www.new-wave-

concepts.com/ed/wizard.html>. Acesso em: 22/10/2014.

15. MONTEBELLER, S. J. Apostila de Eletrônica II. Disponível em:

<http://alfa.facens.br/~sidney>. Acesso em: 26/10/2014.