Eletrônica Digital II - Site do Getúlio Teruo Tateoki´nica Digital II – Flip-Flop´s (a) Se os...

Transcript of Eletrônica Digital II - Site do Getúlio Teruo Tateoki´nica Digital II – Flip-Flop´s (a) Se os...

Prof. Msc. Getúlio Teruo Tateoki 2

Eletrônica Digital II – Flip-Flop´s

Diagrama geral de um sistema digital

Prof. Msc. Getúlio Teruo Tateoki 3

Eletrônica Digital II – Flip-Flop´s

Símbolo geral para um flip-flop e seus dois estados de saída possíveis:

Prof. Msc. Getúlio Teruo Tateoki 4

Eletrônica Digital II – Flip-Flop´s

Um latch(fecho, tranca) com portas NAND tem dois estados

de repousos possíveis: Quando SET=CLEAR(Reset) = 1

Prof. Msc. Getúlio Teruo Tateoki 5

Eletrônica Digital II – Flip-Flop´s

Pulsando a entrada SET para o estado “0” quando:

(a) Q = 0 antes do pulso na entrada SET;

(b) Q = 1 antes do pulso na entrada SET.

Nestes dois casos a saída Q termina com o nível ALTO

Prof. Msc. Getúlio Teruo Tateoki 6

Eletrônica Digital II – Flip-Flop´s

Pulsando a entrada CLEAR para o estado “BAIXO” quando:

(a) Q = 0 antes do pulso na entrada CLEAR;

(b) Q = 1 antes do pulso na entrada CLEAR.

Em cada caso a saída Q termina com o nível BAIXO

Prof. Msc. Getúlio Teruo Tateoki 7

Eletrônica Digital II – Flip-Flop´s

(a) Latch da Porta NAND (b) Tabela Verdade

Prof. Msc. Getúlio Teruo Tateoki 8

Eletrônica Digital II – Flip-Flop´s

(a) Representação equivalente

(b) a um Latch NAND (b) Símbolo simplificado

Prof. Msc. Getúlio Teruo Tateoki 10

Eletrônica Digital II – Flip-Flop´s

(a) A trepidação de um contato mecânico gera múltiplas transições na tensão;

(b) Latch NAND é usado para eliminar as múltiplas transições na tensão.

Prof. Msc. Getúlio Teruo Tateoki 11

Eletrônica Digital II – Flip-Flop´s

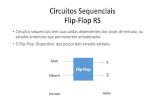

(a) Latch com portas NOR;

(b) Tabela-verdade;

(c) Símbolo simplificado.

Prof. Msc. Getúlio Teruo Tateoki 14

Eletrônica Digital II – Flip-Flop´s

Conceitos: Sinais de “clock”

Prof. Msc. Getúlio Teruo Tateoki 15

Eletrônica Digital II – Flip-Flop´s

Flip-flop com clock tem uma entrada de clock (CLK) que pode ser ativada por

(a) Uma borda de subida ou (b) por uma borda de descida.

As entradas Controle determinam o efeito da transição ativa do clock.

Prof. Msc. Getúlio Teruo Tateoki 16

Eletrônica Digital II – Flip-Flop´s

Entradas de controle tem de ser mantidas estáveis por

(a) Um temp ts antes da transição ativa do clock e

Por (b) um tempo tH após a transição ativa do clock

Prof. Msc. Getúlio Teruo Tateoki 17

Eletrônica Digital II – Flip-Flop´s

Flip-flop S-C com disparo apenas nas transições negativoas do clock

Prof. Msc. Getúlio Teruo Tateoki 18

Eletrônica Digital II – Flip-Flop´s

Versão simplificada do circuito interno de um flip-flop S-C didparado pr borda.

Prof. Msc. Getúlio Teruo Tateoki 19

Eletrônica Digital II – Flip-Flop´s

Implementação de um circuito detector de borda usado em flip-flops

Disparados por bordas: (a) borda positiva. (b) borda negativa.

A duração dos pulsos CLK (clock) é normalmente de 2 a 5 nano segundos.

Prof. Msc. Getúlio Teruo Tateoki 20

Eletrônica Digital II – Flip-Flop´s

(a) Flip-flop J-K com clock que responde apenas as boras positivas do clock.

Prof. Msc. Getúlio Teruo Tateoki 21

Eletrônica Digital II – Flip-Flop´s

(a) Flip-flop tipo D disparados apenas nas transições positivas do clock;

(b) Formas de onda.

Prof. Msc. Getúlio Teruo Tateoki 22

Eletrônica Digital II – Flip-Flop´s

Implementação de um flip-flop D disparado por borda a partir de um flip-flop J-K.

Prof. Msc. Getúlio Teruo Tateoki 23

Eletrônica Digital II – Flip-Flop´s

Transferência de dados em paralelo usando flip-flops D.

Prof. Msc. Getúlio Teruo Tateoki 24

Eletrônica Digital II – Flip-Flop´s

Lach D transparente; (a) estrutura; (b) Tabela-verdade;

(c) Símbolo lógico.

Prof. Msc. Getúlio Teruo Tateoki 25

Eletrônica Digital II – Flip-Flop´s

Formas de onda mostrando os dois modos de operação de um lach D transparente.

Prof. Msc. Getúlio Teruo Tateoki 26

Eletrônica Digital II – Flip-Flop´s

Atrasos de propagação nos FFs.

Prof. Msc. Getúlio Teruo Tateoki 27

Eletrônica Digital II – Flip-Flop´s

Um flip-flop D disparado por bordas é usado para sincronizar a habilitação

da porta AND com a borda de descida do clock.

Prof. Msc. Getúlio Teruo Tateoki 28

Eletrônica Digital II – Flip-Flop´s

Operação de transferência síncrona de dados realizada por diversos

Tipos de FF´s com clock.

Prof. Msc. Getúlio Teruo Tateoki 29

Eletrônica Digital II – Flip-Flop´s

Transferência paralela do conteúdo do registrador X pa ao registrador Y.

Prof. Msc. Getúlio Teruo Tateoki 30

Eletrônica Digital II – Flip-Flop´s

Transferência serial de dados de um registrador X para um registrador Y.

Prof. Msc. Getúlio Teruo Tateoki 32

Eletrônica Digital II – Flip-Flop´s

Flip-flops J-K conectados para um contador binário de três bits.

Prof. Msc. Getúlio Teruo Tateoki 33

Eletrônica Digital II – Flip-Flop´s

Tabela com os estados dos flip-flops mostrando uma seqüência de

contagem binária.

Prof. Msc. Getúlio Teruo Tateoki 34

Eletrônica Digital II – Flip-Flop´s

O diagrama de transição de estados mostra como os estados de um contador

mudam a cada pulso de clock aplicado.

Prof. Msc. Getúlio Teruo Tateoki 35

Eletrônica Digital II – Flip-Flop´s

Exemplo de um microprocessador transferindo dados binários

para um registrador externo.

Prof. Msc. Getúlio Teruo Tateoki 36

Eletrônica Digital II – Flip-Flop´s

(a) Se os tempos de transições das entradas forem muito longos, a saída de um

dispositivo lógico comum pode oscilar ou mudar imprevisivelmente de estado;

(b) Um dispositivo lógico com entrada schimitt-trigger produz uma saída

com transições rápidas.

Prof. Msc. Getúlio Teruo Tateoki 37

Eletrônica Digital II – Flip-Flop´s

http://mesonpi.cat.cbpf.br/e2006/graduacao/pdf_g4/G4-Aula2.pdf

Tocci, Ronald J.; Widmer, Neal S. – Sistemas Digitais, Princípios e Aplicações,

Editora Prendice Hall, 8ª Edição.

Azevedo Jubior, João Batista, TTL/CMOS Teoria e Aplicação em Circuitos Digitais

Volume 1 e 2, Editora Érica - 2ª Edição

Taub, Herbert; Shiling, Donald – Eletrônica Digital, Editora McGraw-Hill

Bibliografia: