Etapas amplificadoras con FET 8...Autopolarización JFET R S R1 RD V DD R2 recta de carga estática...

Transcript of Etapas amplificadoras con FET 8...Autopolarización JFET R S R1 RD V DD R2 recta de carga estática...

-

EtapasEtapasEtapasamplificadorasamplificadorasamplificadoras

con FETcon FETcon FET

FCEIA FCEIA FCEIA --- UNRUNRUNRProf. María Isabel Schiavon

Electrónica I

FET

-

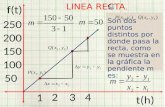

recta de polarización

SDSG Riv −=

recta de carga estática

SD

DSD RR

vVi+−

=

2

1

−=

P

SGSSDD V

vIizona de corriente constanteo de saturación del canal

V

SD RRV+

iD

vDS

Autopolarización JFET

-

RSR1

R D

VDD

R2recta de carga estática

SD

DSDDD RR

vVi+−

=

recta de polarización

SDGGSG RiVv −=

GGV

21

1

RRRVV DDGG +

=2

1

−=

P

SGSSDD V

vIi

iD

vDS

Autopolarización con divisor de tensión JFET

-

Comparación

recta de carga estática

SD

DSDDD RR

vVi+−

=

SDGGSG RiVv −=

GGV

2

1

−=

P

SGSSDD V

vIi

iD

vDS

SDSG Riv −=

DI∆

DI∆

R S R 1

R D

V

R 2

R S R 1

R D

V

R 2

JFET

-

VT

iD

vDS

( ) ( )22 TSDTSGD VvKVvKi −=−≅RD

VDD

RF

MOSFET

-

N-MOS y P-MOS

MOSFET enriquecimiento

VGS>0

NMOS PMOS

VT>0 VT0

ID> 0

VGS< 0

VDS0

VDS>0

ID> 0

VGS< 0 ó VGS> 0

VDS

-

RSR1

R D

VDD

R2

RD

VDD

RF

fuente comúnpuerta comúndrenaje común

FET Polarizado

terminal de excitaciónterminal de salida

Terminal común

Etapas amplificadoras básicas

-

SC-DC-GC

RSR1

RD

VDD

R2

vivo

++

__

fuente

común dre

naje

común

RSR1

VDD

R2

vo+

_

vi+_

RSR1

RD

VDD

R2

vi

vo

+

+_

_

puerta

común

=i

ov v

vA

=i

oi i

iA

=iiiv

iz=

= 0ivo

oo i

vz

+vo--

ii io

+vi--

amplificador

-

SC-DC-GC

=i

ov v

vA =i

oi i

iA

=iiiv

iz == 0ivo

oo i

vz+vo--

ii io

+vi--

amplificador

+vo--

ii io

+vi--

+viAv

R

eszi

zo Rls

si

isi Rz

zev+

=

lo

livo Rz

RvAv+

=

lo

ivo

l

oo

RzvAi

Rvi

+=

−=

-

g d

rdsgmvgs

s

vgs

id

vds

λIVλ1

iv

DQ

DSQ

Vdds

dsQSG

r +==

( )

( )DSS

DPJm

SGPP

SSD

Qgsd

m

I

IVK2g

VVV

I2vig

QQ

QQ

−=

+−−

==

Si VP ≈- 5V IDSS =10mAλ< 0,05/V IDQ==1mA VDSQ=10V

Si VP ≈- 5V IDSS =10mAλ< 0,05/V IDQ==1mA VDSQ=10V

gmQ≈1,26mA/V

rds > 30KΩ

FET: modelo en pequeña señal

-

RSR1

RD

V

R2

vivo

++

__

fuente

común

Fuente común1

QQQ GSV,DSV,DIPunto de Trabajo

Superposición condicionada al punto de trabajo

modelo en señal

G D

rdsg

mvgs

S

vgs

id

RS

RG

+

_

vivo

RD

+

_

gsmds

dsd vg r

vi + = Ddo R = -iv

Sdigs Rivv −=

( )igsods vvvv −−=

-

G D

rdsg

mvgs

S

vgs

id

RS

RG

+

_

vivo

RD

+

_

RSR1

RD

V

R2

vivo+

+__

fuente

común

SmDm

io

v Rg1Rg

vvA

+−

≈=

Amplificador

Fuente común2

C S

≈− DRmg

RS=0

( )[ ]sdsD0eo

oo RrRi

vzs

+=≡=

//

GiFETi Rz//Rz ≈= G

D0eo

oo Ri

vzs

≈≡=

-

Drenaj

e

común

RSR1

VDD

R2

vo+

_

vi+_

1Rg1

RgvvA

SmSm

io

v

-

RSR1

RD

VDD

R2

vi

vo

+

+_

_

Dmio

v RgvvA ≈=

1mS

1mi gR//gz

−− ≈=

Do

oo Ri

vz0se

≈≡=

g

d

rdsgm vgs

svgs

id

RS

+

_vi

voRD

+

_

_

+RG

fuente de corriente o

carga activa

RG=R1//R2

RSR1

VDDR2

Io

( )Sm Rg1oroz +≈

puerta común

-

1<+

≈Sm

Smv Rg1

RgA

1mo gz−≈21Gi RRRz //==

dc

SmDm

io

v Rg1Rg

vvA

+−

≈=

D0eo

oo Ri

vzi

≈≡=

GiFETGi RzRz ≈= //

sc

fuente de corriente o

carga activa

RSR1

VDDR2

Io

( )Sm Rg1oroz +≈

adaptador de impedancia amplifica corriente

amplificador de tensión y

corriente

gc

resumen