Projeto de um decodificador 4X16 bits utilizando...

Transcript of Projeto de um decodificador 4X16 bits utilizando...

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

140

Projeto de um decodificador 4X16 bits utilizando tecnologia Complementary Metal-Oxide Semiconductor de 0,25 µm e metodologia Standard Cell

Carlos Alexandre Silva dos Santos1; Alian Moreira Engroff2

1Docente na Universidade Regional Integrada do Alto Uruguai e das Missões – URI Santiago, Mestrando no PPG Engenharia Elétrica, UNIPAMPA, [email protected]

2Mestrando PPG Engenharia Elétrica, UNIPAMPA, [email protected]

Resumo

Este artigo apresenta um projeto completo de um circuito integrado digital de um

decodificador 4X16 bits, cujo objetivo é propor este CI com tecnologia de 0,25 µm

CMOS e com o menor número possível de transistores. O trabalho visa também

descrever os principais passos para a elaboração de um circuito eletrônico

integrado, descrevendo as vantagens da tecnologia CMOS que é amplamente

utilizada em dispositivos eletrônicos, servindo de embasamento para

desenvolvimento de novos CIs com essa tecnologia. Nesse contexto, é utilizada a

metodologia standard cell na qual são apresentadas todas as fases de projeto,

passando pelos níveis conceitual, lógico, de transistores e de layout. Em cada fase

são apresentadas as simulações elétricas com o intuito de validar o circuito

integrado proposto. Como resultado foi apresentado um projeto completo de

decodificador 4X16 totalmente funcional e com apenas 104 transistores.

Palavras chave: Circuito Eletrônico Integrado. Decodificador 4X16. Complementary Metal-Oxide Semiconductor.

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

141

Project of decoder 4X16 bit using Complementary Metal-Oxide Semiconductor technology of 0.25 µm and Standard Cell methodology

Abstract

This paper presents a complete design of a digital integrated circuit of a 4X16 -bit

decoder, which aims to propose this IC with 0.25 0,25 µm CMOS technology and

with the lowest possible number of transistors. The work also aims to describe the

key steps in the development of an integrated electronic circuit, describing the

advantages of CMOS technology that is widely used in electronic devices, serving

as a basis for developing new ICs with this technology. In this context, the paper

presents use the standard cell methodology in which contains all Project through

the conceptual, logic, transistors and layout levels. In each phase was made

electrical simulations in order to validate the proposed integrated circuit. As a result

was presented a 4X16 decoder complete project fully functional with only 104

transistors.

Keywords: Integrated Circuit Electronic . Decoder 4X16 . Complementary Metal -

Oxide Semiconductor

1. Introdução

Um CI (Circuito Integrado) pode ser definido como sendo um conjunto de

componentes de elementos de circuito, como resistores, diodos, capacitores e

transistores, formados e interligados de forma simultânea dentro de um mesmo

corpo, normalmente uma pastilha de silício, constituindo um dispositivo único que

realiza a função do circuito (MELO 1976).

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

142

Os circuitos integrados são indicados principalmente em aplicações que

têm funções repetitivas e possuem espaços limitados, apresentando inúmeras

vantagens tais como: tamanho e peso reduzidos, baixo consumo de potência, alta

velocidade, confiabilidade, baixo custo e facilidade de manutenção (é mais fácil

realizar a manutenção em circuitos integrados complexos, que utilizam circuitos

integrados, do que se estes fossem constituídos apenas de componentes

individuais).

Circuitos integrados construídos com Transistores de Efeito Campo (Field-

Effect Transistors - FET) do tipo Metal-Óxido Semicondutor Complementares

(Complementary Metal-Oxide Semiconductor - CMOS) são o apogeu de uma

história de desenvolvimento tecnológico que teve início em 1925. Atualmente,

cerca de 75% dos circuitos semicondutores são implementados com essa

tecnologia. As principais vantagens apresentadas pela tecnologia CMOS são o

baixo consumo de potência, alta imunidade a ruído, alto nível de integração,

simplicidade de projeto e operação confiável em ampla faixa de valores de tensão.

O "complementary" em seu nome vem do fato dessa tecnologia utilizar os dois

tipos de transistores MOSFET, o MOSFET canal N e o MOSFET canal P, de tal

modo que um deles "complementa" o outro na necessidade de se produzir

funções lógicas.

Decodificador é um circuito digital que faz a conversão de um código binário

para outro código ou um número qualquer. Geralmente recebe um código binário

na entrada e ativa apenas uma saída, correspondente ao número decodificado. Os

decodificadores são ferramentas importantes nos projetos digitais, pois são

amplamente utilizados para selecionar memórias e realizar conversões de códigos

(por exemplo, binário para decimal) e roteamento de dados.

Este trabalho tem como objetivo apresentar um projeto completo de um

decodificador de linha 4X16 otimizado, de forma que apresente o menor número

possível de transistores. Além disso, pretende se desenvolver o projeto utilizando

tecnologia CMOS de tamanho 0,25 µm através da utilização da metodologia

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

143

standard cell e passando pelos níveis de projeto: funcional; lógico; de transistores;

e de layout.

2. Materiais e Métodos

2.1 Materiais

A confecção do projeto elétrico, as simulações e validações foram

realizadas através do software Hspice, da empresa Synopsys. Para a elaboração

do layout equivalente do circuito foi utilizado o programa Magic VLSI Layout Tool.

2.2 Métodos

s considerações que afetam o projeto de decodificador são várias, tais

como a velocidade e a área de layout disponível. Assim, minimizar a área do

layout pode ser importante. Além disso, considerações sobre o layout são

importantes quando se quer que o decodificador se encaixe no mesmo “pitch” de

layout de algum projeto o qual este deverá endereçar como, por exemplo, células

de memória ou matrizes de células de MOSFETs. Geralmente, o tamanho do

decodificador e o consumo de energia são importantes (SUTHERLAND et al.

1999); um projeto que minimiza esforço lógico (“logicaleffort”) pode exigir

demasiado consumo de energia ou muitos transistores na prática.

Dessa forma, foram analisados alguns tipos de decodificadores,

considerando-se os números de transistores. Os que utilizam o número menor de

transistores consumirão menor área, o que leva a escolha do tipo de decodificador

por este critério de maneira a se atingir a menor área requerida. Entretanto,

existem outros critérios para escolha, já que também deve-se considerar qual dos

tipos de decodificadores terão o projeto de layout mais conveniente (alguns tipos

de decodificadores podem ter uma área de layout irregular ou um roteamento mais

complexo, o que pode inviabilizar sua implementação, mesmo que tenha o menor

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

144

número de transistores). Sabe-se que cada tipo de decodificador possui topologia

particular de layout e isto pode levar a um complexo roteamento de trilhas e/ou

difícil posicionamento das células, assim como pode levar a uma área de layout

muito maior, mesmo considerando o transistor de tamanho mínimo da tecnologia

alvo.

Para isto, utilizar-se-á do conceito de implementação do circuito final com

blocos lógicos menores, utilizando decodificadores com número menor de

entradas ou de diferentes tamanhos, seguidos por portas lógicas menores ou com

número menor de entradas. Ou seja, inicia-se com dois decodificadores simples

ou de um estágio (sendo esse primeiro estágio), como o da Figura III, e as saídas

destes recombinadas em um segundo estágio com portas lógicas menores ou com

pequeno número de entradas. Essa implementação alternativa, segue a idéia do

tipo de decodificador de dois estágios, conforme descrito em (GOEL & AGARWAL

2004). Em (GOEL e AGARWAL), são usadas dois decodificadores 2X4 com portas

NAND (pré-decodificador), como a o da Figura V, seguido por 16 portas lógicas

NAND de duas entradas, resultando em um decodificador 4X16.

Para o desenvolvimento do layout foi adotada a metodologia do tipo

biblioteca de células-padrão (standard-cell), pois, dessa forma, o layout será mais

facilmente modularizado, e possivelmente mais compacto. Os passos necessários

para desenvolvimento do projeto utilizando a metodologia standard cell seguiram

os níveis de projeto: funcional; lógico; de transistores; e de layout. Tais níveis

serão abordados a seguir.

3. Resultados e Discussão

3.1 Nível funcional

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

145

Nesse nível houve uma divisão do circuito a ser projetado em “caixas

pretas”, cada um com uma função específica. Exemplo: decodificador 2X4 e

decodificador 4X16.

3.1.1 Decodificador 4X16 completo

A figura I apresenta o Decodificador 4X16, composto por quatro Inversores

e dezesseis portas AND de quatro entradas, totalizando 136 transistores,

entretanto a figura V apresenta um modelo otimizado, utilizando dois pré-

decodificadores de 2X4, com menor número de portas lógicas possíveis e sem

comprometer o projeto devido à complexidade de roteamento quando da conexão

entre os diversos módulos que farão parte do circuito completo do decodificador.

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

146

Figura I. Decodificador 4X16 - 136 transistores.

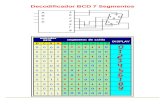

TABELA I – Tabela Verdade para o Decodificador completo 4X16

Entradas Saídas

A B C D S

0 0 0 0 S0

0 0 0 1 S1

0 0 1 0 S2

0 0 1 1 S3

0 1 0 0 S4

0 1 0 1 S5

0 1 1 0 S6

0 1 1 1 S7

1 0 0 0 S8

1 0 0 1 S9

1 0 1 0 S10

1 0 1 1 S11

1 1 0 0 S12

1 1 0 1 S13

1 1 1 0 S14

1 1 1 1 S15

Fonte: autoria própria

Equações de saída:

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

147

3.1.2 Decodificador 4X2

O diagrama de blocos de um codificador de duas entradas e quatro saídas

é apresentado a seguir.

Figura II. Diagrama de blocos de um decodificador 2X4

O circuito esquemático de um codificador de duas entradas usando portas

lógicas NAND de duas entradas (NAND2) e quatro saídas é apresentado a seguira

través de portas lógicas. A construção e simulação do circuito foram realizadas no

software livre Logisim versão 2.7.1, com a finalidade de ilustrar o layout e verificar

seu funcionamento.

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

148

A figura III apresenta o Decodificador 2X4 que será utilizado como pré-

codificador (“predecoder”), uma vez que conforme ilustrado na Figura I, várias

portas AND compartilham exatamente as mesmas entradas e são por isso,

redundantes. Esta técnica leva a possibilidade de melhorar a área, extraindo

essas portas AND em comum por fatoração lógica, melhorando bastante o

consumo de área.

Figura III. Decodificador 2X4 (pré-decodificador).

TABELA II – Tabela Verdade para o Decodificador completo 2X4

Entradas Saídas

A B S

0 0 S0

0 1 S1

1 0 S2

1 1 S3

Fonte: autoria própria

Equações de saída:

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

149

𝑆0 = 𝐴.̅ �̅�

𝑆1 = 𝐴.̅ 𝐵

𝑆2 = 𝐴. �̅�

𝑆3 = 𝐴. 𝐵

3.1.3 Decodificador 4X16 proposto

O circuito que representa o Decodificador 4X16 apresentado no presente

trabalho está ilustrado na Figura IV. Utilizou-se desse circuito, pois há a utilização

de dois Pré-decodificadores 2X4 que farão que haja uma redução de portas

lógicas e, por conseguinte, uma redução do número de transistores. Esse circuito,

por sua vez, é constituído de quatro Inversores, oito portas NAND2 e dezesseis

portas NOR2, totalizando 104 transistores.

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

150

Figura IV. Decodificador 4X16 proposto - 104 transistores

3.2 Nível lógico

Nesta seção haverá o detalhamento de cada uma das “caixas pretas” em

blocos lógicos (portas lógicas), utilizadas para a construção do Decodificador

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

151

4X16. As tabelas verdade para cada porta lógica utilizada estão detalhadas a

seguir.

Porta Inversora:

Figura V. Porta Inversora

TABELA III–Tabela Verdade Porta Inversora

Entrada Saída

A S

0 1

1 0

Fonte: autoria própria

Equação de saída:

𝑆 = �̅�

3.2.2 Porta lógica NAND:

Figura VI. Porta Lógica NAND de 2 entradas

TABELA IV–Tabela Verdade Porta lógica NAND

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

152

Entradas Saída

A B S

0 0 1

1 0 1

0 1 1

1 1 0

Fonte: autoria própria

Equação de saída:

𝑆 = 𝐴. 𝐵̅̅ ̅̅ ̅

3.2.3 Porta lógica NOR:

Figura VII. Porta Lógica NOR de 2 entradas

TABELA V - Tabela Verdade Porta lógica NOR

Entradas Saída

A B S

0 0 1

1 0 0

0 1 0

1 1 0

Fonte: autoria própria

Equação de saída:

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

153

𝑆 = 𝐴 + 𝐵̅̅ ̅̅ ̅̅ ̅̅

3.3 Nível de transistores

Nesse nível foi realizado o dimensionamento dos transistores para

implementação das portas lógicas, bem como a definição das dimensões

geométricas destes transistores.

As portas lógicas usadas no decodificador 4X16 foram dimensionadas com

transistores e a tecnologia utilizada foi CMOS estática. Para cada transistor é

definida uma largura W e um comprimento L. Quanto maior a largura W menor a

resistência e menor o atraso, mas em contrapartida maior a capacitância, ou seja,

maior a potência consumida.

No presente trabalho empregou-se a tecnologia CMOS 0.25 µm e Vdd =

2,5V, logo LMIN = LN = LP = 0.25 µm. Para dimensionar a largura W dos

transistores utilizou-se o gráfico da relação Wp/Wn versus VM (Rabaey2003) e

efetuou-se a simulação do inversor a fim de obter-se uma tensão VM = Vdd/2, para

comparar os valores da teoria com a prática. Os resultados das simulações são

mostrados a seguir.

De acordo com o gráfico da Figura XIII a relação 𝑊𝑝 𝑊𝑛⁄ deve ser

aproximadamente igual a 3,33. A partir desta relação foram definidos os valores

de largura para o NMOS e PMOS do inversor de 𝑊𝑛 = 0,375 µ𝑚 e𝑊𝑝 = 1,25 µ𝑚.

Prosseguiu-se com a simulação e verificou-se que com estes valores VM = Vdd/2 =

1,25V, como observado na Figura IX que apresenta a curva VTC do inversor.

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

154

Figura XIII. Gráfico da relação VM x Wp/Wn da tecnologia CMOS 0,25 µm, 2,5V

Fonte: Adaptado de Rabaey 2002

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

155

Figura IX. Curva VTC do Inversor - análise DC

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

156

Figura X. Análise Transiente do Inversor.

As figuras a seguir detalham as portas lógicas com o dimensionamento dos

transistores.

Figura XI. Circuito Elétrico dos Inversores

O dimensionamento dos transistores das portas lógicas baseiam-se no

inversor. Os detalhes são apresentados a seguir.

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

157

3.4 Caracterização elétrica por simulação

A fim de verificar os tempos de atraso nas portas lógicas que do

Decodificador 4X16 foram realizadas simulações no software Hspice.

O dimensionamento dos transistores das portas lógicas é detalhado a

seguir. A Figura XII ilustra a porta lógica NAND de duas entradas e a Figura XIII

apresenta a simulação, com valores de 𝑊𝑛 = 0,375 µ𝑚 e𝑊𝑝 = 0,375 µ𝑚.

Porta Lógica NAND

Figura XII. Circuito Elétrico da Porta Lógica NAND de duas entradas

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

158

Figura XIII. Tabela-verdade da Porta Lógica NAND de duas entradas

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

159

Figura XIV. Simulação Transiente da porta lógica NAND2

Tempos de atraso da porta NAND2 –1ª Simulação realizada através do

programa Hspice:

Tempo de Descida: 45,403n

Tempo de Subida: 73,315n

Frequência de operação: 1

73,315= 13,64 𝑀𝐻𝑧

Tempos de atraso da porta NAND2 – 2ª Simulação realizada através do

programa Hspice com a utilização do código spice (Simulation Program with

Integrated Circuit Emphasis) gerado da extração do layout desenvolvido no

programa Magic VLSI:

Tempo de Descida: 46,678n

Tempo de Subida: 73,93n

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

160

Frequência de operação: 1

73.93= 13,53 𝑀𝐻𝑧

A Figura XV ilustra a porta lógica NOR de duas entradas e a figura XVI

apresenta a simulação, com valores de 𝑊𝑛 = 0,375 µ𝑚 e𝑊𝑝 = 1,8 µ𝑚.

Porta Lógica NOR

Figura XV. Circuito Elétrico da Porta Lógica NOR de duas entradas

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

161

Figura XVI. Tabela-verdade da Porta Lógica NOR de duas entradas

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

162

Figura XVII. Simulação transiente da porta lógica NOR2

Tempos de atraso da porta NOR2 – 1ª Simulação realizada através do

programa Hspice:

Tempo de Descida: 14,952n

Tempo de Subida: 32,009n

Frequência de operação: 1

32,009= 31,24 𝑀𝐻𝑧

Tempos de atraso da porta NAND2 – 2ª Simulação realizada através do

programa Hspice com a utilização do código spice gerado da extração do layout

desenvolvido no programa Magic VLSI:

Tempo de Descida: 14,95n

Tempo de Subida: 31,167n

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

163

Frequência de operação: 1

31,167= 32,08 𝑀𝐻𝑧

Nas simulações os transistores já se encontravam dimensionados,

obedecendo as seguintes relações:

4. Nível de Layout

Nessa fase foi realizado o layout final do circuito de acordo com as regras

de projeto fornecidas e com as dimensões preestabelecidas pelo nível de

transistores.

A partir de cada porta lógica ilustrada através da tecnologia CMOS e uso de

transistores obtém-se os desenhos dos layouts. Primeiramente ilustrados através

de diagramas de palito ou diagramas Stick e, a seguir na forma de “mask layout”

ou simplesmente layout.

4.1 Diagramas Stick

A seguir são apresentados os diagramas Stick das portas lógicas inversora,

NAND e NOR.

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

164

Figura XVIII. Diagrama Stick da Porta Lógica Inversora

4.2 Layout

A seguir são apresentados os layouts para cada porta lógica. Os Layouts

foram desenvolvidos no programa Magic VLSI.

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

165

Porta lógica Inversora

FiguraXXI Layout do Inversor

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

166

A Figura XXIV apresenta o layout para o decodificador 2X4 elaborado a

partir das portas lógicas construídas e simuladas neste trabalho e com transistores

de acordo com a tecnologia CMOS.

Figura XXIV. Layout do Decodificador 2X4.

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

167

Após validar todas as portas lógicas que compõem o Decodificador 2X4 em

si, pode-se utilizar dois desses como “pré-decodificadores”, com o intuito de se

construir o layout do circuito do Decodificador 4X16. A Figura XXV ilustra o

Decodificador 4X16 completo, proposto nesse trabalho. A Figura XXVI apresenta a

tabela-verdade para demonstrar o correto funcionamento do decodificador e a

Figura XXVII a análise transiente que tem por objetivo analisar os tempos de

atraso do circuito.

Figura XXV. Layout do Decodificador 4X16 proposto.

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

168

Figura XXVI. Simulação do Decodificador 4X16 proposto. Tabela-verdade.

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

169

Figura XXVII. Simulação do Decodificador 4X16 proposto. Análise transiente.

Foram realizadas simulações utilizando o programa Hspice antes da

extração do código spice gerado pelo programa Magic VLSI (1ª simulação), e

outra após, já utilizando os parâmetros fornecidos pelo Magic (2º simulação).

As informações relacionadas à área total das portas lógicas e dos

decodificadores, assim como os tempos de atraso obtidos nas simulações são

apresentados na Tabela VI.

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

170

TABELA VI – Área dos circuitos e tempos de atraso.

PORTA LÓGICA ÁREA

TEMPOS DE ATRASO

TEMPOS DE ATRASO

1ª simulação 2ª simulação

(antes da extração do Magic)

(após extração do Magic)

DESCIDA SUBIDA DESCIDA SUBIDA

Inversor 1.600² 29,186n 23,072n 29,78n 23,247n

Nand2 1.900² 45,403n 73,315n 46,678n 73,93n

Nor2 1.900² 14,952n 32,009n 14,95n 31,167n

Decodificador 2X4 11.385² 44,689n 36,573n 45,354n 36,449n

Decodificador 4X16 68.016² 14,928n 32,104n 15,199n 30,949n

Fonte: autoria própria

Através da observação da Tabela VI é possível verificar a área final

utilizada pelo Decodificador 4X16 proposto, bem como seus tempos de atraso.

É importante destacar a importância de um circuito integrado otimizado, que

utilize o menor número possível de transistores, de forma que diminua o custo

na fabricação, o consumo de energia e a dissipação de calor, além de possuir

tempos de atraso baixo e bom desempenho, características fundamentais para

um bom projeto de circuito eletrônico integrado.

5. Conclusão

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

171

O presente trabalho apresentou as diversas fases (níveis) de projeto para

construção de um circuito integrado digital através do desenvolvimento de um

decodificador 4X16 bits otimizado com 104 transistores, com a utilização de

metodologia standard cell e tecnologia CMOS que é amplamente utilizada na

fabricação de chips e presentes na maioria dos dispositivos eletrônicos utilizados

atualmente.

Além disso, com a apresentação do projeto e suas simulações elétricas

foi possível realizar um estudo comparativo dos resultados obtidos, levando em

conta a área e tempo de atraso (considerando o maior tempo de atraso do

circuito), de forma que o projeto final do decodificador 4X16 bits fosse

devidamente testado e validado.

6. Agradecimentos

Agradecemos à URI Campus de Santiago e à UNIPAMPA Campus de Alegrete

pelo apoio e incentivo à pesquisa.

Referências bibliográficas

CAMARATTA, Giovano da Rosa. 2009. Estruturas de Teste para Avaliação de

Variabilidade Estatística em MOSFETs Sub-100nm. Porto Alegre: UFRGS.

GOEL, Ashish Kumar; AGARWAL, Manish.2004. Decoder Scheme for Making

Large Size Decoder. ST Microeletronics Pvt. Ltd., Uttar Pradesh, India, Sep.

2004. US Patent 6794906. Disponível

em:<http://www.google.com.br/patents?id=0uwRAAAAEBAJ>

Multiciência Online @2016 Universidade Regional Integrada do Alto Uruguai e das Missões – Campus Santiago

ISSN 2448-4148

172

SYNOPSYS – SILICON TO SOFTWARE.2016.Hspice Synopsys. Disponível

em: <http://www.synopsys.com>

KANG, Sung-Mo; LEBLEBICI, Yusuf.2002. CMOS Digital Integrated Circuits

Analysis and Design. 3nd ed. New York: McGraw-Hill Education.

MAGIC VLSI.2016. Magic VLSI Layout Tool. Disponível

em:<http://opencircuitdesign.com/magic/index.html >.

MELO, Hilton Andrade de.1976. Circuitos Integrados. São Paulo: Câmara

Brasileira do Livro.

RABAEY, J. M. et al. 2003. Digital Integrated Circuits: A Design Perspective.

2nd ed. Upper Saddle River: Prentice Hall.

SUTHERLAND, I.E.; SPROULL, R. F.; HARRIS, D. F. 1999.Logical Effort:

Designing Fast CMOS Circuits. San Francisco: USA: Morgan Kaufmann. pág.

239.