PROJETO DE UMA ARQUITETURA BASEADA NUM …‡… · Figura 4 - Classificação dos processadores....

Transcript of PROJETO DE UMA ARQUITETURA BASEADA NUM …‡… · Figura 4 - Classificação dos processadores....

Pós-Graduação em Ciência da Computação

CECIL ACCETTI RESENDE DE ATAÍDE MELO

PROJETO DE UMA ARQUITETURA BASEADA

NUM PROCESSADOR RISC-V PARA

DESENVOLVIMENTO DE APLICAÇÕES EM

SOFTWARE-DEFINED RADIO

Universidade Federal de Pernambuco

[email protected] www.cin.ufpe.br/~posgraduacao

RECIFE

2016

Cecil Accetti Resende de Ataíde Melo

Projeto de uma Arquitetura Baseada num Processador RISC-V para Desenvolvimento

de Aplicações em Software-Defined Radio

ORIENTADORA: Profª. Edna Natividade da Silva Barros

RECIFE

2016

Este trabalho foi apresentado à Pós-Graduação em

Ciência da Computação do Centro de Informática da

Universidade Federal de Pernambuco como requisito

parcial para obtenção do grau de Mestre em Ciência da

Computação.

Catalogação na fonte

Bibliotecária Monick Raquel Silvestre da S. Portes, CRB4-1217

M528p Melo, Cecil Accetti Resende de Ataíde

Projeto de uma arquitetura baseada num processador RISC-V para desenvolvimento de aplicações em software-defined radio / Cecil Accetti Resende de Ataíde Melo. – 2016.

111 f.:il., fig., tab. Orientadora: Edna Natividade da Silva Barros. Dissertação (Mestrado) – Universidade Federal de Pernambuco. CIn,

Ciência da Computação, Recife, 2016. Inclui referências e anexo.

1. Engenharia da computação. 2. Arquitetura de computador. 3. FPGA. I. Barros, Edna Natividade da Silva (orientadora). II. Título. 621.39 CDD (23. ed.) UFPE- MEI 2017-178

Cecil Accetti Resende de Ataide Melo

Projeto de uma Arquitetura Baseada num Processador RISC-V para Desenvolvimento de Aplicações em Software-defined Radio

Dissertação de Mestrado apresentada ao

Programa de Pós-Graduação em Ciência da

Computação da Universidade Federal de

Pernambuco, como requisito parcial para a

obtenção do título de Mestre em Ciência da

Computação

Aprovado em: 26/08/2016.

BANCA EXAMINADORA

__________________________________________

Prof. Dr. Abel Guilhermino da Silva Filho

Centro de Informática / UFPE

__________________________________________

Prof. Dr. Elmar Uwe Kurt Melcher

Departamento de Sistemas e Computação / UFCG

__________________________________________

Profa. Dra. Edna Natividade da Silva Barros

Centro de Informática / UFPE (Orientadora)

Agradecimentos

Agradeço ao CNPq (na gestão do periódo democrático, anterior aos eventos de 2016)

pelo suporte financeiro.

Agradeço à Profª Edna Barros, pela confiança e apoio durante o período que se encerra

com a conclusão desta dissertação, por seu exemplo de dedicação ao trabalho e aos seus

alunos, como provocadora, incentivadora e crítica.

Aos colegas e amigos do grupo de sistemas embarcados: Rafael Macieira, Erika

Spencer, Lucas Cambuim, Dario Soares, Marcus Duarte e Camila Nunes pelas conversas,

discussões e por tornar o ambiente do antigo laboratório C-23 o melhor possível.

À equipe do LINCS-CETENE: Pyetro Ferreira, João Paulo Barbosa, Henrique

Figueirôa, Maria Silveira, Vanessa Ogg, Bruno Neves, Hugo Albuquerque, Josivan Reis e

Severino Barros, pelas contribuições dadas ao trabalho de maneira direta ou indireta e pela

convivência durante últimos dois anos.

Ao Prof. Ricardo Emmanuel de Souza, pelas oportunidades que me proporcionou,

incentivo e pela amizade. Aos professores que contribuíram com a minha formação

acadêmica, em especial aos Prof. Marcio Cornélio, Prof. Odilon Maroja e Prof. Rafael Dueire,

pelo exemplo profissional e de conduta dentro e fora da sala de aula.

Por fim, agradeço à minha família, minha mãe Rossana, meu pai Antônio Emídio e

meu irmão Angelo pela paciência.

Aos meus amigos, desculpem o transtorno.

Shanghai, Setembro de 2016

Resumo

Os sistemas de software-defined radio práticos normalmente se dividem em duas

classes: arquiteturas reconfiguráveis em FPGA que implementam os algoritmos de

processamento de digital de sinais, com granularidade alta e, as arquiteturas baseadas em

processador. Um dos problemas no projeto de arquiteturas de processamento digital de sinais

baseadas em processador é o do suporte a compiladores e linguagens de alto nível.

Arquiteturas muito especializadas, com conjuntos de instruções extensos e muitos modos de

endereçamento, dificultam a implementação de compiladores para linguagens de alto nível.

Neste trabalho buscou-se explorar a viabilidade de um conjunto de instruções emergente,

RISC-V, e uma extensão do seu conjunto de instruções para a aplicação em processamento

digital de sinais de banda base, sobretudo nas funcionalidades de modem, em aplicações de

software-defined radio. A análise das operações de um modem, para as modulações digitais

mais utilizadas, revela que as operações feitas para modulação/ demodulação envolvem

números complexos. No entanto, aritmética de complexos não é normalmente suportada pelo

hardware em arquiteturas tradicionais. Além da arquitetura proposta para o processador, com

suporte a novas instruções especializadas, os periféricos necessários para o front-end de rádio

frequência e o software de suporte foram implementados, resultando num SoC para software-

defined radio.

Palavras-chave: Software-defined radio. DSP. FPGA

Abstract

Practical software-defined radio systems are usually classified in two main

architecture classes: Reconfigurable architectures on FPGAs, that implement coarse grained

digital signal processing algorithms, or processor-based architectures. One of the issues in the

design of processor-based digital signal processing architectures is compiler and high-level

languages support. Highly specialized architectures, with extensive instruction sets (ISA) and

addressing modes turn high-level languages compiler design a complex task. In this work we

explore the viability to extend the emerging RISC-V instruction set for baseband processing

applications for software-defined radio, especially for modem applications. The analysis of

modem functions, for the most used digital modulation schemes, reveals that the

modulation/demodulation tasks involve complex number operations. Complex number

arithmetic, however, is not supported on traditional architectures. The proposed platform

includes a 3-stage pipelined processor with new specialized instructions, as well as the

peripherals needed to the radio-frequency front-end and supporting software, resulting on a

system-on-a-chip for software-defined radio applications. software-defined radio.

Keywords: Software-defined radio. DSP. FPGA

Lista de Figuras

Figura 1 - Espectro eletromagnético, nas frequências de RF ................................................... 21

Figura 2- Diagrama de um rádio digital ................................................................................... 23

Figura 3 - Exemplos de diagramas de constelação. a) Modulação BPSK. b) Modulação QPSK

ou 4-QAM. c) Modulação 16-QAM ......................................................................................... 25

Figura 4 - Classificação dos processadores. ............................................................................. 26

Figura 5 - Arquitetura de um FPGA. Extraído de (Tocci, Widmer e Moss, 2007) .................. 28

Figura 6 - Arquitetura SIMT (Tell, Nilsson e Liu, 2005b) ....................................................... 31

Figura 7 - Arquitetura SODA(Lee, Chakrabarti e Mudge, 2010) ............................................ 32

Figura 8 - Arquitetura GOLD-X(Ramacher et al., 2011) ......................................................... 33

Figura 9 - Arquitetura do sistema proposto por (Chen et al., 2016)......................................... 34

Figura 10 - Fluxograma da metodologia de projeto utilizada .................................................. 36

Figura 11- Diagrama de blocos da arquitetura do sistema proposta......................................... 39

Figura 12 - Registradores de propósito geral e rótulos utilizados pelo compilador ................. 44

Figura 13 - Formatos das Instruções RISC-V (Waterman et al., 2014) ................................... 44

Figura 14 - Listagem das Instruções RV32IM implementadas. ............................................... 46

Figura 15 - Divisão de tarefas entre processador de banda base e processador de aplicação .. 47

Figura 16 - Representação de um número complexo da forma A = a +jb em uma palavra de 32

bits ............................................................................................................................................ 49

Figura 17 - a)Trecho de código C para multiplicação de números complexos, b) Código

assembler da multiplicação, c) Instrução equivalente, cmul ................................................... 49

Figura 18 - a)Trecho de código C para MAC de números complexos, b) Código assembler, c)

Instrução equivalente, cmac ..................................................................................................... 50

Figura 19 -Fluxograma do algoritmo Rijndael, ou AES (Ul Haq et al., 2011). Fluxograma

para encriptação à esquerda, e para decriptação, à direita. ....................................................... 51

Figura 20 - Procedimento xtime() e multiplicação em GF(28) (Daemen e Rijmen, 2002) ...... 51

Figura 21 - Procedimento Multiply() ....................................................................................... 52

Figura 22 - Diagrama da microarquitetura do processador ...................................................... 54

Figura 23 - Estrutura do Banco de Registradores ..................................................................... 56

Figura 24 - Diagrama esquemático da ALU ............................................................................. 58

Figura 25 Diagrama de blocos da CALU ................................................................................. 59

Figura 26 - Diagrama esquemático da unidade CMAC ........................................................... 60

Figura 27 - Caminho de controle do processador ..................................................................... 61

Figura 28 - Estágios do pipeline ............................................................................................... 64

Figura 29 - Espaço de endereçamento de memória .................................................................. 65

Figura 30 - Diagrama de Blocos da plataforma proposta ......................................................... 66

Figura 31 - Diagrama do barramento WISHBONE genérico, listando os sinais de controle, as

linhas de dados e de endereço (OpenCores, 2010) ................................................................... 68

Figura 32 - Diagrama dos sinais WISHBONE durante leitura (OpenCores, 2010) ................. 69

Figura 33 - Diagrama dos sinais WISHBONE durante escrita (OpenCores, 2010) ................. 69

Figura 34 - Diagrama de blocos do Controlador WISHBONE Master .................................... 70

Figura 35 - Diagrama Esquemático do módulo GPIO ............................................................. 72

Figura 36 - Diagrama esquemático do módulo wshbn_timer................................................... 73

Figura 37 - Módulo wshbn_uart ............................................................................................... 74

Figura 38 - Diagrama esquemático do módulo wshbn_ssp ...................................................... 76

Figura 39 - Diagrama Esquemático do módulo wshbn_lo ....................................................... 77

Figura 40 - Diagrama RTL do LSFR........................................................................................ 78

Figura 41 - Diagrama do modulo wshbn_duc .......................................................................... 79

Figura 42 - Resposta em frequência de um filtro CIC (Altera, 2007) ...................................... 79

Figura 43 - Diagrama esquemático do filtro CIC. a)Interpolador e b) Decimador .................. 80

Figura 44 - Diagrama do modulo wshbn_duc .......................................................................... 81

Figura 45 - Placa do front-end sobre o kit DE-0 ...................................................................... 85

Figura 46 - Amostragem dos símbolos ..................................................................................... 86

Figura 47 - Estrutura das tarefas no RIOS-modificado ............................................................ 87

Figura 48 - Tarefas no escalonador, para o caminho de transmissão de um modem ............... 87

Figura 49 - Escalonamento das três tarefas para transmissão num modem simples ................ 88

Figura 50- Trecho de código assembler da rotina de testes para a instrução add ..................... 90

Figura 51 - Captura de tela do osciloscópio durante execução do Dhrystone .......................... 92

Figura 52 - Espectro do sinal modulado em BPSK .................................................................. 95

Lista de Tabelas

Tabela 1- O Modelo OSI .......................................................................................................... 20

Tabela 2- Comparativo entre os Trabalhos Relacionados ........................................................ 35

Tabela 3 - Instruções RV32XOolong ....................................................................................... 48

Tabela 4 - Mapa de Registradores do módulo GPIO................................................................ 71

Tabela 5 - Mapa de Registradores do módulo wshbn_timer .................................................... 73

Tabela 6 - Registradores do modulo UART ............................................................................. 75

Tabela 7 - Registradores do Módulo wshbn_ssp ...................................................................... 76

Tabela 8 - Registradores do módulo wshbn_lo ........................................................................ 81

Tabela 9 - Registradores dos módulos wshbn_duc e wshbn_ddc ............................................ 81

Tabela 10 - Resultados de Síntese EP2C5T144C8 ................................................................... 83

Tabela 11 - Resultados de Síntese EP3C25Q240C8 ................................................................ 84

Tabela 12 - Resultados da Implementação do RIOS- modificado ........................................... 88

Tabela 13 - Resultados da execução das aplicações do TI embedded benchmark suite .......... 91

Tabela 14 - Comparativo da execução do Dhrystone ............................................................... 92

Tabela 15 - Resultados da execução de aplicações do MiBench ............................................. 93

Tabela 16 - Resultados da execução do filtro FIR de (Goh, 2006) .......................................... 94

Tabela 17 - Execução do modulador complexo (BPSK, 4QAM, 16QAM) ............................. 94

Tabela 18 - Execução do AES-128, em ciclos de clock, para uma entrada de 64 bytes .......... 95

Lista de Acrônimos

AM Amplitude Modulation

ASIC Application Specifc Integrated Circuit

ASIP Application Specifc Instruction Set Processor

BPSK Binary Phase-Shift Keying

CI Circuito Integrado

CPU Central Processor Unit

DSP Digital Signal Processor

FIFO First in, First Out

FM Frequency Modulation

FPGA Field Gate Programmable Array

GCC GNU C Compiler

GNU GNU‟s Not Unix

GPP General Purpose Processor

GPS Global Positioning System

GSM Global System for Mobile Communications

ISA Instruction Set Architecture

LUT Look-up table

MAC Multiply-accumulate

MSPS Million (Mega) samples per second

PSK Phase-Shift Keying

QAM Quadrature Modulation

RAM Random-Access Memory

RF Radio Frequência

RISC Reduced Instruction Set Computer

RTOS Real Time Operating System

SDR Software-defined Radio

SFDR Spurious-Free Dynamic Range

SoC System on a Chip

SRAM Static Random-Access Memory

„

Sumário

1. Introdução ........................................................................................................... 14

1.1. Escopo do trabalho ................................................................................................. 17

1.2. Organização da Dissertação ................................................................................... 18

2. Conceitos Básicos ............................................................................................. 19

2.1. Introdução............................................................................................................... 19

2.2. Software-defined radio ........................................................................................... 19

2.3. Processamento de banda base ................................................................................ 22

2.4. Processadores e Sistemas ....................................................................................... 25

2.5. FPGAs .................................................................................................................... 27

3. Trabalhos Relacionados .................................................................................. 30

3.1. Introdução............................................................................................................... 30

3.2. Arquiteturas baseadas em processador ................................................................... 30

3.3. Discussão ................................................................................................................ 34

4. Visão Geral do Projeto ..................................................................................... 36

4.1. Introdução............................................................................................................... 36

4.2. Análise dos requisitos............................................................................................. 37

4.3. Planejamento da arquitetura do processador .......................................................... 37

4.4. Projeto RTL ............................................................................................................ 37

4.5. Benchmarking ........................................................................................................ 38

4.6. Profiling das Aplicações......................................................................................... 38

4.7. Integração do processador e projeto da plataforma ................................................ 39

5. Projeto do Conjunto de Instruções ............................................................... 41

5.1. Introdução............................................................................................................... 41

5.2. O conjunto de instruções RISC-V .......................................................................... 42

5.2.1. Modelo de programação........................................................................................ 43

5.2.2. Formatos de Instrução ........................................................................................... 44

5.2.3. Instruções RV32IM ................................................................................................ 45

5.3. Profiling das aplicações alvo .................................................................................. 45

5.3.1. Processamento de banda base ............................................................................... 47

5.4. Instruções de aplicação específica – Extensão Oolong .......................................... 47

5.4.1. Instruções de aritmética complexa ........................................................................ 48

5.4.2. AES ........................................................................................................................ 50

5.5. Conclusão ............................................................................................................... 52

6. Microarquitetura ................................................................................................ 53

6.1. Introdução............................................................................................................... 53

6.2. O caminho de dados ............................................................................................... 55

6.2.1. Banco de Registradores ......................................................................................... 55

6.2.2. Unidade Lógica e Aritmética ................................................................................. 56

6.2.3. Unidade de execução Oolong ................................................................................ 58

6.3. Caminho de Controle ............................................................................................. 60

6.3.1. Unidade de Busca e Previsão de Desvios .............................................................. 61

6.3.2. Decodificador de Instruções .................................................................................. 62

6.3.4. Registradores especiais e de controle .................................................................... 62

6.4. Pipeline ................................................................................................................... 63

7. Memória e Periféricos ...................................................................................... 65

7.1. Introdução............................................................................................................... 65

7.2. Memória de Inicialização ....................................................................................... 66

7.3. Memória de Programa ............................................................................................ 66

7.4. Memória de Dados ................................................................................................. 67

7.5. Controlador de Memória ........................................................................................ 67

7.6. Barramento WISHBONE ....................................................................................... 67

7.7. Periféricos............................................................................................................... 70

7.7.1. GPIO ...................................................................................................................... 71

7.7.2. TIMER.................................................................................................................... 72

7.7.3. UART ..................................................................................................................... 73

7.7.4. SSP ......................................................................................................................... 75

7.7.5. Oscilador local ...................................................................................................... 77

7.7.6. Interface de RF ...................................................................................................... 78

8. Implementação em FPGA ............................................................................... 82

8.1. Introdução............................................................................................................... 82

8.2. Implementação RTL ............................................................................................... 82

8.2.1. Cyclone II............................................................................................................... 82

8.2.2. Cyclone III ............................................................................................................. 83

8.3. Ambiente de simulação e validação ....................................................................... 84

8.4. Escalonador de tarefas ............................................................................................ 85

8.5. Sistema de Arquivos e Drivers de Periféricos ........................................................ 88

8.6. Benchmarking e Aplicações ................................................................................... 89

8.6.1. Testes de instrução ................................................................................................ 89

8.6.2. TI Embedded Benchmark Suite .............................................................................. 90

8.6.3. Dhrystone ............................................................................................................... 91

8.6.4. MiBench ................................................................................................................. 92

8.6.5. Avaliação das Instruções da Extensão Oolong ..................................................... 93

8.7. Conclusões ............................................................................................................. 95

9. Conclusões e Trabalhos Futuros ................................................................. 97

9.1. Conclusões ............................................................................................................. 97

9.2. Trabalhos Futuros ................................................................................................... 98

Referências ....................................................................................................... 100

Anexo A - listagem das instruções propostas ....................................... 105

14

1

Introdução

Com o aumento do número de protocolos e bandas de operação dos sistemas de

comunicação sem fio, software-defined radio (SDR) tem aos poucos saído da condição de

tecnologia promissora e assumido papel central no desenvolvimento dos novos padrões em

telecomunicações civis e militares e no aprimoramento dos sistemas já existentes, que não

podem ser abandonados (FORUM, 2014)

A programabilidade é o fator chave para a implementação de sistemas de rádio-

comunicação multibanda e multiprotocolo flexíveis, como definem as técnicas de SDR. Os

circuitos integrados (CI) dedicados ou ASIC (Application-specific Integrated Circuit), que

implementam processadores de aplicação única, normalmente utilizados nos sistemas de

comunicação tradicionais necessitam de circuitos específicos para cada modo de operação,

havendo pouco compartilhamento de recursos, aumentando assim a área destes CIs, o

consumo de energia e o custo de produção destes dispositivos (LIU, 2008).

A tecnologia de projeto a ser utilizada para uma determinada aplicação (se ASICs,

circuitos com componentes discretos, ou processadores programáveis) é, além de decisão do

projetista, baseando-se na sua experiência ou de sua equipe, regida também por fatores como

custo de desenvolvimento, tempo de projeto e ainda da janela de mercado do produto, que

afeta o seu preço final ao consumidor. No contexto da evolução constante dos sistemas de

comunicação atuais, em que novos padrões mais eficientes ou adequados a determinados

cenários de utilização surgem a cada ano, sobretudo ao se considerar a recente tendência da

chamada Internet-das-Coisas (IoT, Internet-of-Things), os ASICs, mesmo possuindo o menor

custo unitário em grandes volumes necessitam de grande esforço de projeto e por sua

15

característica básica de ter um algoritmo de processamento de sinal único mapeado num

circuito, dificultam ou até tornam impraticáveis a operação multibanda e multiprotocolo.

Para implementação de um sistema de comunicação multibanda e multiprotocolo

baseado em técnicas de software-defined radio, é fundamental a utilização de técnicas de

processamento digital de sinais. Historicamente, o processamento de sinais de rádio foi feito a

partir de sistemas com circuitos analógicos, como filtros, moduladores, amplificadores. Com

a introdução dos sistemas de comunicação digital, passou-se a implementar circuitos

equivalentes aos circuitos analógicos usuais, com componentes digitais, porém com mesma

estrutura, algoritmos e topologias. Mesmo baseados em componentes digitais, estes são

circuitos de aplicação única. Os processadores digitais de sinal (DSP) surgiram

comercialmente nos anos 1980, voltados à aplicações de processamento de voz e áudio. À

medida que o aumento da capacidade de integração dos dispositivos semicondutores vem

duplicando a cada dezoito meses, a chamada Lei de Moore (embora haja sinais recentes de

que este comportamento esteja se esgotando (WALDROP, 2016) ) os DSPs tiveram sua

capacidade de processamento aprimorada, estando hoje presentes na maioria dos sistemas de

comunicação, seja na transmissão de voz, como na telefonia celular, como nos links de dados

da internet, nos modems ADSL e nos pontos de acesso de redes WiFi.

Duas categorias de circuitos de processamento digital de sinais prevalecem atualmente:

os processadoresDSP de propósito geral, e os processadores com conjunto de instruções de

aplicação específica (ASIP). DSPs de propósito geral, como os TMS320C5x da Texas

Instruments e SHARC da Analog Devices, possuem instruções alto desempenho na

implementação da maioria dos algoritmos de processamento digital de sinais tradicionais,

possuem ferramentas de suporte e desenvolvimento de software além de aplicações de

referência e casos de uso. Porém, ferramentas de código aberto para programação de

processadores DSP são escassas, salvo as produzidas pela própria empresa proprietária da

arquitetura do processador. Como são processadores de propósito geral, a depender do

software que esteja sendo executado pode haver hardware ocioso, que contribui para o

consumo de energia e desperdício de área de silício, ou mesmo limitações de desempenho em

algumas aplicações, como sistemas operacionais, por exemplo. Os processadores de aplicação

específica surgem como alternativas aos processadores DSP de propósito geral, como uma

classe de processadores com conjunto de instruções (ISA) adaptado à aplicação-alvo ou à uma

classe de aplicações (LIU, 2008).

Nas aplicações de comunicação digital, as tarefas de processamento da informação

recebida ou a ser transmitida são chamadas de processamento de banda base. Um processador

16

de banda base programável é então um ASIP especializado no processamento das cadeias de

transmissão e recepção de sinais em sistemas de comunicação sem-fio (rádio), por cabos

elétricos ou de fibra óptica (modems). É este dispositivo que permite a implementação

eficiente de sistemas de software-defined radio, sobretudo no âmbito dos sistemas

embarcados. A programabilidade deste ASIP permite o reuso de suas estruturas de hardware

entre vários padrões de comunicação ou mesmo a interoperabilidade entre padrões, a critério

do projetista e da necessidade das aplicações. Entre as classes de algoritmos que podem ser

implementados por processadores de banda base estão:

Codificação/ Decodificação de áudio/voz;

Codificação de canal;

Modulação/demodulação;

Filtragem;

Sincronização de pacotes;

Estimação de canal e equalização;

Correção de erros.

Os processadores de banda base programáveis também permitem que uma mesma

plataforma de hardware seja utilizada mesmo havendo mudanças nos protocolos e padrões

utilizados, sendo este problema resolvido por meio de updates de software, sem a necessidade

de mudanças no hardware, o que contribui para a redução da obsolescência dos dispositivos e

equipamentos de comunicação. Para permitir esta evolução constante do software e dos

padrões de comunicação, é necessário que a arquitetura do processador também possa ser

melhorada, otimizada para as aplicações já existentes, mas sem perder sua a flexibilidade para

execução de novas tarefas a serem criadas e definidas.

No desenvolvimento de um ASIP duas abordagens são as mais utilizadas: desenvolver

o conjunto completo de instruções, apenas com as instruções necessárias para a classe de

aplicações desejada ou seja, através da customização completa; ou, partir de um conjunto de

instruções básico e extendê-lo com novas instruções dedicadas à esta classe de aplicações,

através de uma customização parcial(KONG et al., 2010). Em comparação com a

customização completa, a customização parcial tem vantagens claras. A utilização de uma

arquitetura base reduz o esforço de implementação das ferramentas de desenvolvimento de

software (compilador, depurador, simulador, etc.) facilitando o uso de linguagens de

programação de alto-nível, além de permitir uma possível herança de bibliotecas de software

já existentes.

17

Algumas arquiteturas de processadores de banda base programáveis tem sido

propostas, utilizando ambas as abordagens (TELL; NILSSON; LIU, 2005a)(NILSSON,

2007)(LEE; CHAKRABARTI; MUDGE, 2010)(FUJISAWA et al., 2003). Devido à sua

simplicidade, arquiteturas com conjuntos de instrução reduzidos (RISC) são as melhores

candidatas para extensão e customização. O trabalho desenvolvido por Fujisawa propõe um

processador de banda base baseado numa arquitetura RISC de projeto próprio. Essa

abordagem como todas que utilizam arquiteturas não padronizadas, entretanto, tem o

desenvolvimento de software prejudicado.

Como uma nova especificação aberta para um conjunto de instruções de propósito

geral, a arquitetura de processador RISC-V foi desenvolvida na Universidade da Califórnia

(WATERMAN et al., 2014). Em 2015 a governança da especificação foi entregue à RISC-V

Foundation, sendo a arquitetura explorada em projetos tanto na indústria como na academia,

como uma alternativa aos conjuntos de instruções proprietários. Um conjunto de instruções

aberto e padronizado facilita o desenvolvimento de novas técnicas de projeto de hardware e

software, e tem criado uma comunidade de usuários rapidamente, o que aumenta a

disponibilidade de uma base de código estável, de forma similar ao processo ocorrido com o

lançamento do kernel Linux.

Este trabalho propõe uma extensão ao conjunto de instruções RISC-V, especializado

para o processamento de banda base e aplicações de software-defined radio. O processador

ASIP baseado no processador RISC-V foi prototipado em uma plataforma voltada à

aplicações de transmissão e recepção de dados e voz nas faixas de frequências entre 100 KHz

e 45 MHz, onde se encontram a maior parte das bandas alocadas para comunicações de de

serviços públicos e de emergência, de rádio amador, da faixa do cidadão e dedicadas a

instrumentos médicos e científicos (AGÊNCIA NACIONAL DE TELECOMUNICAÇÕES,

2014). A plataforma utilizada para prototipação utiliza um FPGA da família Cyclone III da

Altera (ALTERA, 2012).

Escopo do trabalho 1.1.

O escopo desta dissertação é o projeto de um processador de aplicação especifíca, voltado

a aplicações de processamento de banda base, tendo como foco aplicações de banda estreita,

que possibilite a programação de protocolos de transmissão de voz e dados, extendendo o

conjunto de instruções (ISA) de uma arquitetura padronizada.

18

Entre os objetivos e contribuições deste trabalho, incluem-se:

Projeto e implementação de um processador baseado no conjunto de instruções

da arquitetura RISC-V, compatível com as ferramentas de software de código

aberto GNU-GCC para esta arquitetura.

Projeto de uma extensão do ISA escolhido, considerando a padronização dos

formatos de instrução da arquitetura, para otimização de aplicações de software-

defined radio.

Projeto e implementação de unidades funcionais do processador que viabilizem

as instruções propostas.

Desenvolvimento de uma plataforma de hardware e software para execução dos

testes e dos casos de uso, incluindo periféricos do processador e front-end

digital e analógico.

Somado a estes objetivos, buscou-se realizar a plataforma de demonstração mantendo-se um

custo de implementação baixo, influenciando na escolha dos componentes (FPGA, ADC,

DAC, etc.) e comparar o processador desenvolvido com outros processadores utilizados em

sistemas embarcados.

Organização da Dissertação 1.2.

Esta dissertação é dividida em 9 capítulos, incluindo os capítulos de introdução e

conclusão. No capítulo 2, são apresentados os conceitos básicos que fundamentam o projeto

de pesquisa, assim como a motivação deste trabalho.

No capítulo 3, são discutidos os trabalhos relacionados e suas contribuições para este

trabalho, e é apresentada uma análise comparativa entre as abordagens existentes.

Os capítulos 4 a 7 descrevem, respectivamente, a arquitetura proposta para uma

plataforma de hardware e software, incluindo o processador de aplicação específica proposto

e seus periféricos, voltada ao processamento de sinais em banda base para aplicações de

software-defined radio.

O software de suporte às aplicações e os resultados experimentais são discutidos no

capítulo 8. O capítulo 9 apresenta as conclusões deste trabalho, e enumera possíveis trabalhos

futuros que podem ser derivados do trabalho desta dissertação.

19

2

Conceitos Básicos

Introdução 2.1.

Tradicionalmente, os rádios tem sido projetados para o processamento de um apenas

um formato de onda específico (GRAYVER, 2010). Esta especialização permite que o

circuito do transmissor ou do receptor seja otimizado para a aplicação desejada, em custo,

tamanho e potência. Dispositivos capazes de operar em diferentes padrões e frequências

existem desde os primeiros dias das comunicações sem fio, embora isto não os torne rádios

multipadrão. Desde os rádios AM/FM mais simples, até os aparelhos de telefonia celular mais

recentes (com suporte a padrões como WiFi, Bluetooth, NFC, GPS e também telefonia

WCDMA, GSM, etc), na maioria dos casos são compostos por módulos (hardware)

separados, dedicados a cada formato de onda, ou protocolo de comunicação. A idéia de se

unificar o hardware de um dispositivo para os vários padrões que ele suporte, ou venha a

suportar, sendo o processamento de cada formato de onda feito via software é a base do que

veio a ser definido como software-defined radio. Neste capítulo tratamos da fundamentação

dos conceitos que evolvem o projeto de um sistema de software-defined radio, dos algoritmos

e do hardware necessário para sua implementação.

Software-defined radio 2.2.

A definição do Wireless Innovation Forum (FORUM, 2014) para software-defined radio

diz:

Um software-defined radio é um rádio em que algumas ou todas as funcionalidades da

camada física são definidas via software.

20

Esta definição inclui o conceito de camadas de abstração de um sistema de comunicação.

O modelo OSI (Open Systems Interconnect) para as camadas de abstração define sete

camadas (KUROSE; ROSS, 2010) listadas na Tabela 2.1.

Tabela 1- O Modelo OSI

Número Nome Função

7 Aplicação Permite acesso aos serviços da rede para os processos e usuários

6 Apresentação Converte os dados entre o formatos da aplicação e os da rede

5 Sessão Estabelece a sessão entre os processos que se comunicam na rede

4 Transporte Controla a transferência dos dados da aplicação, corrigindo erros e perdas

3 Rede Realiza o controle dos caminhos (roteamento) dos dados até o destino

2 Enlace Transfere os quadros de dados entre os nós da rede, através da camada fisica

1 Física Realiza a transmissão/recepção propriamente dita, através de um meio físico.

O modelo de camadas permite que os sistemas de comunicação sejam divididos em partes

de função semelhante, em que cada camada realiza serviços para a camada superior, através

de interfaces padronizadas. Desta forma, aplicações diferentes (Voz e SMS, por exemplo)

podem ser executadas num mesmo sistema, ou ainda, uma mesma aplicação pode suportar a

execução através de diferentes camadas de enlace ou física. Por exemplo na troca do acesso à

internet via cabo para uma conexão sem fio, as mesmas aplicações (e-mail, streaming) podem

ser executadas.

A camada física é a responsável pelo transporte de cada bit dos dados através de um meio

físico (cabo de cobre, ar, vácuo, ou cabo de fibra óptica), descrevendo as interfaces elétricas e

mecânicas do sistema com o meio. Entre as funcionalidades da camada física estão:

Codificação dos dados

Modo de transmissão (recepção)

Acesso ao meio físico

com exceção das etapas que são dependentes do meio utilizado para comunicação, a maior

parte das funcionalidades da camada física são equivalentes, independentes do meio, seja ele

um meio comportado como cabos de fibra optica ou elétricos, ou meios mais sujeitos a

interferência, como o ar ou o vácuo. Por rádio, se entende qualquer dispositivo que transmita

ou receba informação através de sinais eletromagneticos em frequências tipicamente entre 3

kHz a 300 GHz, como exemplificado na Figura 1.

21

Figura 1 - Espectro eletromagnético até 300 GHz

Software-defined radio, em outras palavras, é um transceptor de rádio em que o

comportamento pode ser alterado mudando o programa a ser executado. Entre os parâmetros

que podem ser alterados estão: frequência ou faixa de frequências de operação, modulação e

codificação dos dados (TELL, 2005). A possibilidade de mudança do formato de onda

utilizado contrasta com as características dos rádios tradicionais, implementados

completamente em hardware, e que não suportam modificação a não ser sob intervenção em

seu circuito (NILSSON, 2007).

A necessidade por rádios flexíveis, que suportem o chaveamento entre diferentes

protocolos, frequências e modos de operação surge da demanda por interoperabilidade entre

os inúmeros sistemas de comunicação atuais. Estes dispositivos também ajudam a reduzir os

custos de fabricação e projeto dos sistemas, dando ao projetista a possibilidade de desenvolver

uma plataforma de hardware única, que tem sua funcionalidade ampliada através de

modificações no software, aumentando assim a vida útil dos produtos. Para comunicações

táticas, ou militares, software-defined radio permite que diferentes órgãos e agências, que

utilizam faixas de frequências e modos de operação distintos possam, quando necessário,

realizar comunicação conjunta, por exemplo entre os diferentes níveis de polícia (militar, civil

e federal), órgãos de defesa civil (Corpo de Bombeiros, serviços de emergência municipais ou

estaduais) e entre as forças armadas (Aeronáutica, Marinha e Exército). A implementação da

camada física em software ainda, diminui a área de placa de circuito impresso dos sistemas,

ao implementar tarefas antes executadas atraves de (multiplos) circuitos integrados em tarefas

de software em um unico processador, reduzindo o custo de fabricação, tamanho e peso, que

podem ser críticos dependendo da aplicação, em especial nos sistemas embarcados.

O hardware de rádios tradicionais é limitado pelas características dos componentes utilizados,

notadamente componentes analógicos discretos ( resistores, capacitores, indutores, etc.), não

aceitando modificações de suas funcionalidades sem a modificação física de seu circuito. Isto

resulta num maior custo de projeto e produção destes dispositivos, e na necessidade de

22

módulos TX e RX específicos para a faixa de frequência de operação desejada. Com o

crescimento da demanda dos sistemas de telecomunicações, a popularização dos serviços de

telefonia e internet, e com o aumento do número de formas de onda utilizadas em um único

aparelho – GSM, 3G, GPS, 802.11, Bluetooth, etc.– o conceito de SDR surgiu como uma

forma de simplificar e reduzir os custos do hardware, deixando os detalhes da implementação

da camada física de cada protocolo a cargo do processador de propósito geral, e não de um

hardware específico.

O Wireless Inovation Forum descreve um sistema de SDR prático como (FORUM, 2014):

SDR é uma coleção de tecnologias de hardware e software onde algumas ou

todas as funções são implementadas através de software modificável

operando em tecnologias de processamento programáveis. Estes dispositivos

incluem field-programmable gate-array (FPGA), processadores digitais de

sinais, processadores de propósito geral ou processadores de aplicação

específica.

Para realização das técnicas de SDR, conversores de dados isto é, conversores analógico-

digital, e digital-analógico, com altas taxas de amostragem (> 10 MSPS) são necessários. A

escolha destes componentes é determinada por um compromisso entre consumo de potência,

largura de banda, relação sinal-ruído (SNR), spurious-free dynamic range (SFDR), e custo

destes dispositivos.

Processamento de banda base 2.3.

Um rádio digital típico é constituído por cinco módulos básicos, como mostrado na Figura

2. O processador de aplicação é normalmente um microcontrolador ou processador de

propósito geral, o qual executa os processos que geram ou consomem os dados transmitidos

ou recebidos. Essas aplicações podem variar desde as mais simples, como um terminal de voz

ou texto, até as mais sofisticadas como decodificação de video ou mesmo um sistema

operacional completo, para acesso à internet.

23

Figura 2- Diagrama de um rádio digital

O processador de banda base é o módulo responsável pelo processamento da informação,

no nível da camada física. Este módulo é comumente chamado de modem devido à sua

principal atribuição: a modulação e demodulação dos dados transmitidos e recebidos,

respectivamente.

Da Figura 2 nota-se a existência de dois caminhos básicos, as cadeias de transmissão e de

recepção. Na cadeia de transmissão, o processador de banda base codifica e modula os dados

digitais recebidos do processador de aplicação e entrega ao conversor analógico-digital

(DAC). O sinal analógico convertido, então, é modulado na frequência da onda portadora ( a

frequência em que é transmitido pelo meio físico) e amplificado, no front-end de radio-

frequência (RF). Na cadeia de recepção, o inverso ocorre. O sinal captado pela antena é

amplificado e extraído da onda portadora, passando a ser um sinal em banda base. A

digitalização do sinal é feita através do conversor analógico-digital, que a partir daí é

equalizado, sincronizado e demodulado pelo processador de banda base, que entrega os dados

recuperados pela recepção ao processador de aplicação.

2.3.1. Modulação

Sinais digitais são usualmente representados como uma cadeia de dados binários (bits),

sequências de 0 e 1. Cabe ao processador de banda base transformar a sequência de dados

original, em uma outra, mais adequada à transmissão através de um meio físico. Este meio, o

canal de comunicação, a depender de suas características, pode acrescentar ruído e distorções

que podem corromper a informação nele transmitida. Para transmitir corretamente a sequência

binária no canal, é preciso gerar uma representação desta sequência binária de maneira

adequada ao canal. Esta representação deve permitir a recuperação da sequencia original a

partir do sinal detectado pelo receptor. O processo de mapeamento de uma sequência digital

em sinais para transmissão em um canal de comunicação é chamado de modulação digital

(PROAKIS, 2001).

24

Nos processos de modulação digital, a sequência de bits é convertida numa sequência de

símbolos, com o número de bits por símbolo determinando a taxa de transmissão da

modulação. Pela natureza dos canais típicos, os sinais transmitidos são periódicos no formato

da equação 2.1, onde x(t) é um sinal variante no tempo, fc é a frequência da portadora e ( ) é

a sua fase.

( ) ( ) ( ( )) (2.1)

Os símbolos correspondem, dentro de cada tipo de modulação, a variações da amplitude x(t)

do sinal, da frequência fc e da fase ( ). O formato de modulação digital mais simples,

chamado de Amplitude Shift Keying, ou ASK, atribui valores específicos para a amplitude do

sinal, para representação de 0 e 1. Em seu caso mais básico, com x(t) = 1 para representação

do bit 1 e x(t) = 0 para representação do bit 0, esta modulação é chamada de OOK (on-off

keying). Quando os símbolos utilizados se refletem na variação da frequência fc, tem-se a

modulação FSK (Frequency shift keying). Quando a variação é dada sobre a fase ( ) ,

obtém-se a modulação PSK, ou phase shift keying.

Os esquemas de modulação analógica, AM e FM também podem ser descritos pela

equação 2.1, assim como o caso em que tanto a amplitude quanto a fase são utilizados para

representação do sinal digital, a modulação QAM (Quadrature-amplitude modulation).

O sinal S(t) da equação 2.1 é um sinal complexo, com componentes real e imaginária.

Mapeando-se os símbolos de cada modulação no plano complexo, obtém-se o diagrama de

constelação da modulação. Neste diagrama, cada símbolo é representado por um ponto no

plano complexo.

Na Figura 3 são mostrados os diagramas de constelação de três tipos de modulação: BPSK,

QPSK e 16-QAM. A modulação BPSK (binary phase shift keying) utiliza um mapeamento de

25

Figura 3 - Exemplos de diagramas de constelação. a) Modulação BPSK. b) Modulação QPSK ou

4-QAM. c) Modulação 16-QAM

um bit por símbolo. Neste esquema, os dois valores possiveis pra cada bit, 0 ou 1, são

mapeados como símbolos correspondentes aos números 1 + 0j e -1 + 0j, respectivamente.

Na modulação QPSK, Figura 3b, é utilizado um mapeamento de 2 bits / símbolo, o que

torna possível a ocorrência de quatro símbolos 00 , 01, 10 e 11, representados no plano

complexo por -1 –j, -1+j, 1 –j e 1+j, respectivamente. Na modulação 16-QAM, o mapeamento

é feito em 4 bits / por símbolo, com a ocorrência de 16 símbolos distintos. Neste formato, a

sequência 1011, por exemplo, é mapeada no símbolo complexo 1+ 3j.

Após o mapeamento das sequências de bits nos respectivos símbolos, a modulação é

completada através da multiplicação do símbolo (um número complexo) por uma onda

portadora, que também pode ser representada através de um número complexo da forma:

( ) ( ) (2.2)

.

Processadores e Sistemas 2.4.

O principal componente de qualquer sistema computacional é a unidade central de

processamento (CPU) , também chamada de processador. Desde as CPUs descartáveis,

presentes em etiquetas de RFID e que substituem os códigos de barra, até os

26

supercomputadores utilizados para pesquisa científica, o projeto de CPUs a grosso modo

segue os mesmos princípios básicos.

As CPUs em geral possuem memória para armazenamento de programas e dados, um

caminho de dados para processamento e algum dispositivo para entrada e saída de dados ou

informação, como uma tela, botões, teclado, porta de comunicação. A maneira como estas

partes se organizam, no entanto, dependem da aplicação do sistema, que implicam em

limitações de preço, custo, tamanho, e consumo de energia.

De maneira geral, os processadores se dividem em processadores de propósito geral (GPP),

como o Intel Pentium, e os processadores de aplicação específica onde se incluem os

microcontroladores e os processadores digitais de sinais (DSP).

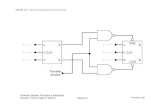

Figura 4- . Classificação dos processadores. (uC : microcontroladores, uP: microprocessadores, ASIP:

processadores de conjunto de instrução de aplicação específica, ASIC: circuitos ntegrados de aplicação

específica)

A divisão entre cada classe de processadores, porém, é difusa. Os processadores de

propósito geral mais recentes possuem instruções de aplicação específica, assim como os

microcontroladores e DSPs passam a suportar a execução de tarefas mais genéricas, inclusive

de sistemas operacionais. A Figura 4 ilustra este continuum das classes de processadores, com

exemplos de famílias de processadores que se enquadram nestas classes.

2.4.1. Application-specific Instruction Set Processors (ASIP)

ASIPs, ou processadores de conjunto de instruções de aplicação específica, são

processadores com instruções dedicadas a uma ou a um conjunto de aplicações. Estas

instruções são projetadas normalmente para otimizar a execução de determinados algoritmos,

reduzindo os seus gargalos de desempenho, em geral dados por operações que possuem maior

custo computacional e que são críticas ao desempenho do algoritmo.

27

O projeto de um ASIP consiste em se avaliar os trade-offs entre a flexibilidade de um

processador de propósito geral, com o desempenho para a aplicação de interesse, de um

processador de aplicação específica. Como ilustrado na Figura 4, o grau de especialização do

conjunto de instruções do ASIP pode variar bastante.

De maneira geral, para se aumentar o grau de especialização de um processador três

técnicas são normalmente utilizadas (LIU, 2008): Aceleração em nível de instrução,

aceleração em nível de função e otimização da microarquitetura.

Das três técnicas, a otimização da arquitetura foi bastante utilizada nos processadores x86,

com a adição de unidades funcionais, despacho de multiplas instruções e técnicas de

exploração do paralelismo de instrução (HENNESSY; PATTERSON, 2012). Esta abordagem,

porém, é a mais custosa em termos de área de circuito integrado e consumo de energia.

A aceleração em nível de função, adiciona ao sistema coprocessadores especializados que

em conjunto com o processador executam os algoritmos da aplicação desejada. Por exemplo

um coprocessador para compressão de imagens em câmeras fotográficas, que divide com o

processador principal, processador de aplicação, partes de algoritmos de processamento

digital de sinais, ou executam os algoritmos completos. Embora essa técnica possibilite

desempenho elevado nas aplicações desejadas, ela reduz a possibilidade de reuso deste

coprocessador em outras aplicações, ainda que semelhantes.

A aceleração em nível de instrução é a que possibilita o desenvolvimento de ASIPs. Nesta

técnica, operações ou sequências de operações comuns às aplicações de interesse são

substituídas por instruções únicas. A inclusão de novas instruções especializadas pode ser

feita através de novas estruturas de computação (caminho de dados), ou com utilização das

estruturas já existentes no processador, apenas necessitando a mudança e inclusão das novas

instruções no decodificador de instruções do processador.

A tecnologia de projeto de um ASIP também é dependente de sua aplicação.

Tradicionalmente, circuitos integrados dedicados são os mais utilizados para implementação

dos ASIPs. No entanto, com a redução do custo dos FPGAs, proporcionado em parte pelos

efeitos da lei de Moore (MOORE, 1998), estes tem ganhado espaço na implementação de

ASIPs (LIU, 2015)(MORAWIEC; HINDERSCHEIT, 2012)(PODIVINSKY et al., 2015).

FPGAs 2.5.

Field-programmable gate-arrays, FPGAs, são dispositivos semicondutores de lógica

reconfigurável, projetados para serem configurados após sua fabricação. FPGAs contém

28

estruturas chamadas blocos lógicos e uma malha de interconexões programáveis, como

mostrado na figura 5. Os blocos lógicos dos FPGAs da família Cyclone II da Altera,

utilizados neste trabalho, possuem uma tabela de busca, look-up table ou LUT, que gera as

saídas lógicas para quatro variáveis (sinais) de entrada, e um registrador, além das conexões

da malha.

Figura 5 - Arquitetura de um FPGA. Extraído de (TOCCI; WIDMER; MOSS, 2007)

FPGAs são largamente utilizados para a realização de tarefas específicas, quando o número

de dispositivos a serem produzidos não justifica a produção de circuitos integrados dedicados

(ASICs, application-specific integrated circuits) ou durante as etapas de desenvolvimento e

prototipação do sistema. Recentemente, o uso de FPGAs em produtos finais tem crescido,

sobretudo em equipamentos de teste e medição (osciloscópios, geradores de funções, etc.)

devido ao seus custos, que vêm diminuindo, e à facilidade de reconfiguração dos FPGAs, que

permite o reuso de plataformas de hardware em diferentes produtos .

A configuração dos FPGAs se dá através de linguagens de descrição de hardware, HDL,

Entre as HDL mais utilizadas estão as linguagens VHDL (DEWEY, 1983), Verilog e

SystemVerilog.

VHDL surgiu através da demanda do Departamento de Defesa, DoD, dos EUA para uma

linguagem de descrição de circuitos integrados padronizada para as indústrias de defesa e

aeroespacial. Desenvolvida inicialmente com objetivo de documentação dos circuitos

29

integrados, VHDL se mostrou adequada para a simulação destes Cis, e posteriormente para o

uso em automação do projeto eletrônico, EDA (eletronic design automation). É uma

linguagem fortemente tipada e estruturada, baseada por definição do DoD na linguagem de

programação Ada. Este trabalho utilizou VHDL em todos os módulos da arquitetura

implementada no FPGA.

30

3 Trabalhos Relacionados

Introdução 3.1.

Muitas arquiteturas de suporte a software-defined radio vem sendo propostas, pela

indústria e pela academia. Duas abordagens alternativas às tradicionais arquiteturas centradas

em ASIC tem dominado: a primeira, baseada na utilização de hardware reconfigurável e a

segunda, de arquiteturas centradas em processadores (DSP ou ASIP)(RAMACHER et al.,

2011). No entanto, uma plataforma de SDR não se restringe apenas ao processador de banda

base, sendo necessário também o desenvolvimento do front-end de RF, adequado aos padrões

convencionados.

Neste capítulo são discutidos alguns trabalhos que se aproximam do objetivos do

projeto proposto nesta dissertação, que é de desenvolver não apenas o processador mas os

componentes adicionais da plataforma, incluindo parte do front-end de RF, integrado no

mesmo FPGA.

Arquiteturas baseadas em processador 3.2.

Alguns trabalhos recentes contribuíram muito na fundamentação de arquiteturas de

DSPs alternativas aos DSPs tradicionais, para execução das tarefas de processamento de

banda base.

Os trabalhos de Tell e Nilsson (TELL; NILSSON; LIU, 2005b) (NILSSON et al.,

2005) propõem uma arquitetura, chamada Single Instruction stream – Multiple Tasks, ou

SIMT, que reúne o paralismo de instrução largamente utilizado nos DSPs comerciais

tradicionais, com o paralelismo de dados, típico das aplicações multimídia, nas quais o

processamento de banda base se inclui. A arquitetura SIMT explora a natureza vetorial dos

31

programas de banda base, com um trade-off entre uma arquitetura de paralelismo de instrução

explícito (VLIW – very long instruction word) com o paralelismo de dados SIMD (single-

instruction, multiple data).

Figura 6 - Arquitetura SIMT (TELL; NILSSON; LIU, 2005b)

A arquitetura SIMT introduz as instruções de aritmética de complexos, adequadas às

aplicações de processamento de banda base, e que não são normalmente implementadas nos

DSPs usuais. Cada unidade funcional executa operações sobre vetores de dados com tamanho

arbitrário, e distribuídos em bancos de memória independentes. A execução das operações

sobre vetores pode durar muitos ciclos de clock, no entanto o controlador pode despachar

instruções seguintes para execução concorrente em outras unidades funcionais.

Embora tenha desempenho suficiente para execução de esquemas de modulação sofisticados

como OFDM, em aplicações como Digital Video Broadcasting (DVB) e WiMax, o suporte à

programação utilizando linguagens de alto nível é limitado, devido às características da

arquitetura que dificultam a implementação de compiladores.

Com objetivo de reduzir o consumo de potência em dispositivos móveis, a arquitetura

SODA (signal processing on-demand), proposta por (LEE; CHAKRABARTI; MUDGE,

2010) utiliza uma abordagem multi-core para um processador de banda base.

A arquitetura SODA é composta por um processador de controle, quatro núcleos

SIMD e uma memória comum (scratchpad) a todos os núcleos. Cada núcleo contém dois

pipelines que suportam instruções escalares, tipo RISC, e instruções sobre vetores com até 32

valores de 16 bits. A figura 7 mostra o diagrama de blocos da arquitetura.

32

Figura 7 - Arquitetura SODA(LEE; CHAKRABARTI; MUDGE, 2010)

O suporte a aplicações de propósito geral é limitado na arquitetura SODA, e inexistente na

arquitetura SIMT, por serem ambas arquiteturas muito especializadas, não sendo adequadas

para execução de tarefas dos protocolos de comunicação além da camada física.

A arquitetura X-GOLD, proposta pela Infineon Technologies (RAMACHER et al., 2011)

resolve o problema da execução de tarefas de propósito geral, com a inclusão de uma CPU

com conjunto de instruções ARM11, lado a lado com um subsistema para SDR composto por

quatro elementos de processamento (PE) para operações vetoriais SIMD. Os comandos para

cada PE são divididos em três slots: uma instrução lógica/aritmética, uma instrução de acesso

a memória e uma terceira instrução para comunicação entre os PEs. Cada PE é formado por

um núcleo RISC com 270 instruções, em um pipeline de 7 estágios, além do caminho de

dados SIMD. As aplicações alvo da arquitetura incluem: GSM, EDGE, GPRS, UMTS, HSPA,

e LTE.

33

Figura 8 - Arquitetura GOLD-X(RAMACHER et al., 2011)

Estas três abordagens representam o estado da arte dos processadores de banda base

utilizados em comunicações móveis, com algumas das técnicas propostas já tendo sido

incorporadas nos processadores de banda base para telefonia celular mais recentes. Entretanto,

as soluções descritas, assim como a arquitetura Ardberg (ANJUM et al., 2011), AnySP entre

outras, por serem voltadas às aplicações de telefonia móvel, LTE, TV digital, e redes LAN

sem-fio, não são as mais adequadas aos sistemas de comunicação que se enquadram na

categoria de internet-of-things (IoT). Estes dispositivos em geral possuem limitações de

potência, área e custo, e não demandam processamento de banda larga.

Neste contexto, o trabalho de (CHEN et al., 2016) propõe uma arquitetura de

coprocessador de banda base voltado às aplicações de IoT. A Figura 9 ilustra a arquitetura,

que conta com um microcontrolador ARM Cortex-M0+ que se comunica com o datapath de

SDR através do barramento de memória. O sistema como um todo é capaz, de executar

programas para as modulações 4-OQPSK e FSK, para Bluetooth Low Energy (BLE) com

potência inferior a 2mW, tendo sido implementado num processo CMOS de 28nm.

34

Figura 9 - Arquitetura do sistema proposto por (CHEN et al., 2016)

Discussão 3.3.

As soluções apresentadas, embora tenham alto desempenho nas aplicações para as quais

foram projetadas, foram concebidas para implementação em circuito integrado, para

utilização em produtos de eletrônica de consumo. Estes trabalhos não definem o front-end de

RF, nem os componentes adicionais do sistema, como os upconverters e downconverters que

são normalmente utilizados para modulação nas frequências utilizadas para transmissão e

recepção.

A arquitetura SIMT introduz as instruções de aritmética complexa, e o suporte do caminho

de dados do processador aos tipos de dados complexos, embora este tipo de operação possa

ser executado em apenas um ciclo, utilizando arquiteturas VLIW ou SIMD.

No desenvolvimento de aplicações em software-defined radio é comum a utilização do

framework GNU Radio (GNURADIO, 2016). Este conjunto de ferramentas de software para

processamento digital de sinais, blocos, que podem ser integrados formando um fluxo de

dados. GNU Radio permite não só a implementação de protocolos e formatos de onda já

existentes, mas também a prototipação de novos esquemas e formatos de onda. GNU Radio,

porém, exige a utilização de um processador de propósito geral, tipicamente x86, embora

existam esforços para que seja portado a outras arquiteturas que possibilitem seu uso em

sistemas embarcados (MA et al., 2014). Para emprego do GNU Radio na prototipação e

35

implementação dos sistemas, é necessário ainda um front-end de RF compatível, entre os

disponíveis no mercado (Ettus Research, 2016).

Na Tabela 2 são listadas as características principais dos trabalhos discutidos acima. Como

será discutido nos capítulos seguintes, neste trabalho buscou-se o desenvolvimento de uma

plataforma de hardware e software para aplicações de software-defined radio, baseada em

FPGA e pelas limitações naturais desta tecnologia de projeto, voltada a aplicações de

processamento de banda base em banda estreita, com foco em permitir a prototipação e o

desenvolvimento de novas aplicações e formatos de onda. A arquitetura do processador, no

entretanto é independente da tecnologia utilizada, podendo ser portada para outros

dispositivos FPGA e ou ASIC.

Neste cenário de utilização, o trabalho proposto se enquadra como viabilizador de uma

etapa intermédiária no fluxo de projeto de sistemas de comunicação, que tem o seu

desenvolvimento iniciado utilizando-se ferramentas como GNU Radio e MATLAB, de alto

nível de abstração, em seguida tem seu software portado para um sistema como o da

arquitetura proposta, e por último é implementado em sua versão final, em arquiteturas de

processadores de banda base especializados, como os discutidos anteriormente neste capítulo.

Tabela 2- Comparativo entre os Trabalhos Relacionados

(Tell,

Nilsson e

Liu, 2007)

(RAMACHE

R et al.,

2011)

(LEE;

CHAKRABART

I; MUDGE,

2010)

(CHEN et

al., 2016)

(GNURadi

o)

Aplicação DVB/

WiMax

LTE WCDMA IoT Genérico

Linguagem Assembly/C Assembly/C Assembly/C Assembly/

C

C/Python

Aritmética Complexos/

Ponto Fixo

Ponto Fixo Ponto Fixo Ponto Fixo Ponto

Flutuante

Aceleração de

Criptografia

Não Sim Não Não x86:

AES-NI

Tecnologia de

Projeto

CMOS CMOS CMOS CMOS SW + HW

adicional

Ferramentas

de software

Proprietária Proprietária Proprietária Proprietári

a

Open-

source GPL

36

4

Visão Geral do Projeto

Introdução 4.1.

Neste capítulo é apresentada a estrutura completa da plataforma de hardware e software

proposta a ser detalhada nos capítulos seguintes, bem como é discutida metodologia de

projeto utilizada para o seu desenvolvimento, baseada no fluxo de projeto descrito em (LIU,

2008). O fluxograma desta metodologia é mostrado na Figura 10.

Figura 10 - Fluxograma da metodologia de projeto utilizada Análise dos

requisitos do sistema, exploração

das aplicações

Especificação do Conjunto de

Instruções base

Planejamento da arquitetura do processador

Especificação das Instruções de

aplicação específica

Geração do modelo RTL do processador

base

Escolha e profiling das aplicações

Benchmarking

Incorporação da extensão ao

processador base

Geração do Modelo RTL das unidades funcionais de aplicação específica

Benchmarking

Geração do Assembler e compilador

Versão Final

37

Análise dos requisitos 4.2.

Na primeira fase do projeto foi feita a análise das possíveis aplicações e dos requisitos do

sistema a ser desenvolvido. Para este trabalho, foram analisadas as aplicações de software-

defined radio e os algoritmos de processamento digital de sinais mais utilizados na área, de

modo a definir para quais aplicações o sistema deverá ser especializado.

Nesta etapa foram avaliados:

A disponibilidade do HW a ser utilizado, FPGAs e outros componentes;

Divisão de tarefas entre processador, periféricos e hardware adicional;

O conjunto de algoritmos de processamento digital de sinais, específico da

aplicação alvo, a serem otimizados;

Escolha dos casos de uso do sistema e da metodologia de avaliação do

desempenho;

Dentre as arquiteturas de processador de aplicação específica discutidos no capítulo 2,

optou-se pela customização parcial de um conjunto de instruções já existente, a arquitetura

RISC-V. A customização parcial do ISA permite o reuso das ferramentas de desenvolvimento

de software, como assembler, compilador e debugger, além de permitir o acesso à base de

código já existente para a arquitetura. A arquitetura RISC-V foi escolhida por seu conjunto de

instrução RISC básico e pelo suporte existente para extensões do ISA desde sua concepção. A

partir deste conjunto de instrução base, procedeu-se com as demais etapas do fluxo de projeto.

Planejamento da arquitetura do processador 4.3.

Antes de dar início ao projeto das instruções de aplicação específica, foi necessário o

desenvolvimento da arquitetura geral do sistema e da microarquitetura do processador. O

processador e sua plataforma (memórias e periféricos) foram especificados em nível de

transações entre circuitos combinacionais e registradores (RTL), com o projeto de todas as

unidades de computação, barramentos, módulos de controle, além dos decodificadores,

multiplexadores e demultiplexadores necessários para a interface entre cada uma das

unidades, de acordo com a especificação definida na arquitetura RISC-V. Esta etapa é

detalhada no capítulo 6, com a descrição de cada módulo da microarquitetura do processador.

Projeto RTL 4.4.

O projeto e a implementação de sistemas digitais pode ser realizado utilizando-se diferentes

níveis de abstração (GAJSKI et al., 2009). O nível de abstração RTL, ou register-transfer

38

level, é um desses níveis, em que o sistema é descrito por meio da relação entre as funções

lógicas e os elementos de armazenamento (memória ou registradores). A descrição dos

sistemas normalmente é feita por meio de linguagens de descrição de hardware (HDL), como

VHDL, Verilog, SystemVerilog ou SystemC.

Nesta etapa, além da descrição em H DL do processador, também foi realizada a descrição de

sua plataforma de hardware, barramento de periféricos, e hierarquia de memórias. O código

em HDL foi então submetido ao processo de síntese, utilizando ferramentas de software

específicas para o FPGA a ser utilizado, o que viabilizou a prototipação e os testes do sistema.

Benchmarking 4.5.

Benchmarking é o processo de análise de desempenho de um processador, considerando o

hardware e o software ou ainda a qualidade dos compiladores (LIU, 2008). Os programas

utilizados nesta análise (benchmarks) geram informações como o número de ciclos

necessários para o processador realizar uma tarefa, o tamanho do código (custo de memória) e

verificam o funcionamento do processador, comparando os resultados obtidos com os

resultados esperados para um conjunto de tarefas/aplicações.

O processo de benchmarking é iterativo, como mostra a Figura 10. Com a execução dos

programas dos benchmarks são encontrados erros e detectados pontos da arquitetura que

prejudicam o desempenho do processador, que devem ser corrigidos. Este processo dura até

que os requisitos do projeto sejam cumpridos, e que o processador se comporte como

esperado para cada uma das aplicações de teste. Os benchmarks utilizados para validação do

processador e da plataforma são discutidos no capitulo 8.

Profiling das Aplicações 4.6.

O objetivo de um processador de aplicação específica, como um DSP ou no nosso caso de

um processador de banda base, é atingir o desempenho adequado ou especificado pela

aplicação, adequando os custos de projeto, de área de circuito ou de potência necessária, de

acordo com os requisitos do projeto. Para tanto é necessário o entendimento da aplicação de

forma a identificar que partes dos seus algoritmos são críticas, que afetam o desempenho e os

custos do projeto.

Profiling (LIU, 2008) é uma técnica que permite estimar os custos de execução e de

memória do código-fonte de uma aplicação. Analisando o código-fonte de um programa,

pode-se encontrar quais as funções que quando compiladas geram maior código objeto, ou de

39

máquina (análise estática), e o número de vezes que estas são chamadas durante a execução

do programa (análise dinâmica). Desta maneira, encontram-se os kernels, ou núcleos, o

conjunto de operações aritméticas mais frequentes. Os detalhes do processo de profiling

utilizado é discutido no capítulo 5, que trata do projeto do conjunto de instruções do

processador e da inclusão das novas instruções no assembler do GCC.

Integração do processador e projeto da plataforma 4.7.

Para possibilitar o desenvolvimento de aplicações em software-defined radio, é necessário

além do processador de banda base, de um front-end de RF e de periféricos que auxiliem o

processador nestas tarefas. Além do processador de banda base outros módulos fazem parte

da arquitetura do sistema, como mostrada na Figura 11.

Figura 11- Diagrama de blocos da arquitetura do sistema proposta. Processador e periféricos: UART –

Universal Asynchronous Receiver-Transmitter (porta serial), GPIO – general purpose input-output, SSP

– synchronous serial port, DUC- digital upconverter, DDC – digital downconverter, DAC I/F, digital-

analog converter interface, ADC I/F – analog-digital converter interface. ADC e DAC externos ao FPGA.

O processador, seguindo uma arquitetura Harvard, possui memórias separadas para

programa (instruções) e dados. A memória de instruções, por sua vez, é dividida fisicamente

em duas memórias independentes: memória de inicialização, ou boot, e a memória de

aplicação. A memória de boot é a responsável pelo armazenamento das rotinas de

inicialização do sistema de arquivos FAT, e carrega os programas armazenados em um cartão

40

de memória Secure Digital (SD). Os periféricos no barramento WISHBONE são mostrados na

Figura 4.2. Os periféricos incluem: Interfaces de comunicação serial síncrona (SSP) e

assíncrona (UART), duas portas de entrada e saída de 16 bits (GPIO) e interface de rádio,

formada por um up-converter no caminho de transmissão, e um down-converter, no caminho

de recepção dos sinais de rádio. A interface de rádio recebe e envia sinais aos conversores de

sinal (ADC e DAC), fora do FPGA.

41

5

Projeto do Conjunto de Instruções

Introdução 5.1.

A principal diferença entre um processador de aplicação específica (ASIP) e um

processador de propósito geral é o seu domínio de aplicação (LIU, 2008). Processadores de

propósito geral são projetados buscando prover desempenho em várias classes de aplicações,

das mais variadas áreas e complexidades. O desempenho de um GPP não necessariamente

será o melhor para todas as classes de aplicações, tendo como objetivo o melhor desempenho

na média das aplicações. Um ASIP, por outro lado, possui instruções e microarquitetura que

limitam seu uso no processamento de classes de aplicações específicas, por exemplo um

ASIC dedicado ao processamento de áudio/video, ou no caso deste trabalho, no

processamento de sinais de rádio em banda base.

No projeto de um ASIP, a escolha da arquitetura do processador é a primeira, e mais

importante etapa. Duas formas de seleção da arquitetura são possíveis: a utilização de uma

arquitetura de referência ou, a geração de uma arquitetura dedicada, com caminho de dados

customizado para a aplicação desejada.

O desenvolvimento de uma arquitetura dedicada a uma aplicação (ou a uma classe de

aplicações) passa pela partição das tarefas entre software e hardware. A escolha entre

hardware e software para uma função depende da avaliação de várias métricas como tamanho,

potência, desempenho, custo, garantia de programabilidade para vários algoritmos dentro da

classe de aplicações, bem como a flexibilidade do sistema, sendo este processo de escolha

42

conhecido como hardware/software codesign (GAJSKI; ZHU; DÖMER, 1997). Uma

arquitetura dedicada porém, pode dificultar a implementação de compiladores para linguagens