Relatorio 3 Aoc

-

Upload

pedro-henrique-costa -

Category

Documents

-

view

214 -

download

1

description

Transcript of Relatorio 3 Aoc

-

UNIVERSIDADE FEDERAL DE SO PAULO

Instituto de Cincia e Tecnologia

Campus So Jos dos Campos

Relatrio: Apresentao da Controladora

Pedro Henrique de Oliveira Lopes Costa RA 86923

Professor Dr. Tiago de Oliveira Disciplina: Laboratrio de Arquitetura e

Organizao de Computadores

22 de junho de 2015

So Jos dos Campos SP

-

2

RESUMO

O projeto em si consiste na elaborao de um processador, passando pela

definio de quais instrues ele deve ser capaz de processar, at o

processamento efetivo de tais. Em um primeiro momento restringimo-nos a

definir as instrues e fazer um esquemtico de como seria a parte funcional do

processador. Seguindo, apresentamos a descrio em Verilog da memria

principal, memria de instrues, PC, ULA e banco de registradores. Agora

ento, apresentamos a descrio dos mdulos chamados de controladora e de

processamento. Sendo assim, vale ressaltar que a ideia do projeto do aluno a

construo de um processador o qual pretende realizar operaes bsicas e

operaes um pouco mais elaboradas, sendo que em um futuro prximo,

deveremos rodar um sistema operacional e criar um compilador para funcionar

neste processador.

-

3

SUMRIO

1. Introduo..........................................................................Pgina 4

2. Objetivos............................................................................Pgina 5

3. Fundamentao Terica....................................................Pgina 6

4. Desenvolvimento do Trabalho...........................................Pgina 8

5. Discusses.........................................................................Pgina 19

6. Referncias Bibliogrficas..................................................Pgina 20

Listas de Figuras e Tabelas:

Fig 1. Esquemtico de funcionamento e caminhos do processador. Pgina 6

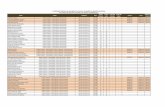

Fig 2. Diagrama de ondas para controladora.................................. Pgina 15

Tab 1: Formato da instruo............................................................. Pgina 8

-

4

1. INTRODUO

As unidades de controle dos processadores tem por funes, trs

operaes bsicas: buscar, decodificar e executar. Sendo assim, os

processadores funcionam de maneira cclica, sempre passando por essas trs

operaes. Existem muitos modelos de processadores nos mercados, sendo

que eles possuem dois tipos de unidades de controle: fixa ou programvel. Os

programveis possuem a opo de terem as instrues escritas pelos

programador, enquanto as unidades de controle fixas possuem as instrues j

programadas. Exemplos de processadores de controladoras fixas so os

8080/8085.

No caso do projeto em questo, estamos construindo um processador

com conjunto fixo de instrues, ou seja, nossa controladora j ter as instrues

pr-gravadas nela, cabendo ela apenas interpretar as instrues de entrada.

Visto isso, percebemos que a elaborao de um processador baseada

em etapas, onde em uma primeira etapa, devemos definir a finalidade a qual o

nosso processador deseja atender, seguido das definies de quais instrues

que ele deve executar e como executar, para ento comearmos a parte prtica,

fazendo cada mdulo que ir compor partes do processador. Neste relatrio

iremos descrever o processo de construo para a controladora e para o

processamento.

-

5

2. OBJETIVOS

Os objetivos gerais do projeto so descrever em Verilog um processador

capaz de realizar operaes aritmticas e lgicas bsicas, compreendendo

instrues e realizando-as. No entanto, os objetivos especficos dessa etapa so

a apresentao dos cdigos em Verilog e os diagramas de onda dos mdulos

controladora e processamento, demonstrando assim o andamento do projeto.

Esta a ltima etapa antes da execuo das descries no FPGA.

-

6

3. FUNDAMENTAO TERICA

Na hora de descrever um processador em Verilog, precisamos saber

como as coisas acontecem na execuo desse tipo de linguagem e ainda como

um processador deve funcionar e ser dividido.

Como dito em [1] e [2], em uma unidade de controle temos o

entendimento do opcode de uma instruo, enviando sinais para cada um dos

mdulos, dizendo para cada um se ele deve ou no executar algo e como

executar. No caso do projeto em questo, a controladora far ainda mais coisas

como ser visto mais frente, visto que ela, ao interpretar o opcode, divide o

cdigo de instruo em partes, onde cada parte um endereo ou um valor.

Outro ponto importante dito em [3] o que precisamos para montar um

processador, ou seja, os mdulos necessrios para o bom funcionamento de um

processador. Neste assunto, temos que precisaremos de um esquema com ULA,

PC, memria ram, memria de instrues, banco de registradores, uma

controladora e um mdulo que rena o funcionamento de todos eles.

Colocado estes pontos, vamos apresentar novamente nosso esquemtico

(j apresentado no primeiro e segundo relatrios), com os ajustes finais feitos. A

Figura 1 representa esse esquemtico.

Figura 1. Esquemtico de funcionamento e caminhos do processador.

-

7

Na Figura 1, vemos que do relatrio 1 e do 2 para esse tivemos a

colocao e o endereamento de cada canal de ligao para os mdulos, onde

cada linha representa um sinal que transmitido entre os mdulos.

-

8

4. DESENVOLVIMENTO DO TRABALHO

Depois de construdas a memria principal, a memria de instrues, o

banco de registradores, a ULA e o contador de programa, nos atentamos agora

para as unidade chamadas de controladora e de processamento.

Como j tnhamos definido, a escolha do tamanho da instruo feita foi de

32 bits, divididos conforme a Tabela 1.

Tabela 1: Formato da instruo

Op code (5 bits)

Onde gravar

(5 bits)

Onde ler (5 bits)

Onde ler ou valor inteiro (5 bits ou 0

bits)

Valor inteiro ou endereo de

memria (12 bits ou 17 bits 16 bits

usuais)

Sendo assim, teramos 32 registradores disponveis (25) e um Op code

capaz de entender 32 instrues diferentes para serem executadas. Em Onde

gravar e Onde ler temos os registradores que devem servir de destino e de

origem para os dados. J em Valor inteiro e Endereo de memria temos um

valor para operaes imediatas ou um endereo de memria que ser usado em

operaes do tipo load e store.

Feitas as devidas colocaes, seguimos com o cdigo do mdulo

controladora, seguido do seu diagrama de ondas, representado na Figura 2.

module controladora( 1

input [31:0]instrucao_saida, 2

output reg [4:0]controle_ula, 3

output reg [15:0]valor, 4

output reg [15:0]endereco_branch, 5

output reg [1:0]controle_registradores, 6

output reg [4:0]endereco_registrador3, 7

output reg [4:0]endereco_registrador2, 8

output reg [4:0]endereco_registrador1, 9

output reg [1:0]controle_memoria, 10

output reg [15:0]endereco_memoria, 11

output reg [15:0]registrador_memoria, 12

output reg [15:0]jump, 13

output reg [1:0]controle_pc, 14

output reg [1:0]controle_moduloio 15

-

9

); 16

17

always@(instrucao_saida) 18

begin 19

if(instrucao_saida[31:27]==5'b00000) //add 20

begin 21

controle_ula=5'b00000; 22

controle_registradores=2'b01; 23

controle_pc=2'b00; 24

endereco_registrador1=instrucao_saida[26:22]; 25

endereco_registrador2=instrucao_saida[21:17]; 26

endereco_registrador3=instrucao_saida[16:12]; 27

end 28

if(instrucao_saida[31:27]==5'b00001) //addi 29

begin 30

controle_ula=5'b00001; 31

controle_pc=2'b00; 32

endereco_registrador1=instrucao_saida[26:22]; 33

endereco_registrador2=instrucao_saida[21:17]; 34

valor=instrucao_saida[15:0]; 35

end 36

if(instrucao_saida[31:27]==5'b00010) //sub 37

begin 38

controle_ula=5'b00010; 39

controle_registradores=2'b01; 40

controle_pc=2'b00; 41

endereco_registrador1=instrucao_saida[26:22]; 42

endereco_registrador2=instrucao_saida[21:17]; 43

endereco_registrador3=instrucao_saida[16:12]; 44

end 45

-

10

if(instrucao_saida[31:27]==5'b00011) //subi 46

begin 47

controle_ula=5'b01101; 48

controle_pc=2'b00; 49

endereco_registrador1=instrucao_saida[26:22]; 50

endereco_registrador2=instrucao_saida[21:17]; 51

valor=instrucao_saida[15:0]; 52

end 53

if(instrucao_saida[31:27]==5'b00100) //and 54

begin 55

controle_ula=5'b00011; 56

controle_registradores=2'b01; 57

controle_pc=2'b00; 58

endereco_registrador1=instrucao_saida[26:22]; 59

endereco_registrador2=instrucao_saida[21:17]; 60

endereco_registrador3=instrucao_saida[16:12]; 61

end 62

if(instrucao_saida[31:27]==5'b00101) //andi 63

begin 64

controle_ula=5'b01010; 65

controle_pc=2'b00; 66

endereco_registrador1=instrucao_saida[26:22]; 67

endereco_registrador2=instrucao_saida[21:17]; 68

valor=instrucao_saida[15:0]; 69

end 70

if(instrucao_saida[31:27]==5'b00110) //or 71

begin 72

controle_ula=5'b00100; 73

controle_registradores=2'b01; 74

controle_pc=2'b00; 75

-

11

endereco_registrador1=instrucao_saida[26:22]; 76

endereco_registrador2=instrucao_saida[21:17]; 77

endereco_registrador3=instrucao_saida[16:12]; 78

end 79

if(instrucao_saida[31:27]==5'b00111) //ori 80

begin 81

controle_ula=5'b01011; 82

controle_pc=2'b00; 83

endereco_registrador1=instrucao_saida[26:22]; 84

endereco_registrador2=instrucao_saida[21:17]; 85

valor=instrucao_saida[15:0]; 86

end 87

if(instrucao_saida[31:27]==5'b01000) //jump 88

begin 89

controle_pc=2'b01; 90

jump=instrucao_saida[15:0]; 91

end 92

if(instrucao_saida[31:27]==5'b01001) //branch 93

begin 94

controle_ula=5'b00111; 95

controle_registradores=2'b01; 96

controle_pc=2'b10; 97

endereco_branch=instrucao_saida[15:0]; 98

endereco_registrador2=instrucao_saida[26:22]; 99

endereco_registrador3=instrucao_saida[27:17]; 100

end 101

if(instrucao_saida[31:27]==5'b01010) //branch not equal 102

begin 103

controle_ula=5'b01000; 104

controle_registradores=2'b01; 105

-

12

controle_pc=2'b10; 106

endereco_branch=instrucao_saida[15:0]; 107

endereco_registrador2=instrucao_saida[26:22]; 108

endereco_registrador3=instrucao_saida[27:17]; 109

end 110

if(instrucao_saida[31:27]==5'b01011) //slt 111

begin 112

controle_ula=5'b00101; 113

controle_registradores=2'b01; 114

controle_pc=2'b00; 115

endereco_registrador1=instrucao_saida[26:22]; 116

endereco_registrador2=instrucao_saida[21:17]; 117

endereco_registrador3=instrucao_saida[16:12]; 118

end 119

if(instrucao_saida[31:27]==5'b01100) //slti 120

begin 121

controle_ula=5'b00110; 122

controle_pc=2'b00; 123

endereco_registrador1=instrucao_saida[26:22]; 124

endereco_registrador2=instrucao_saida[21:17]; 125

endereco_registrador3=instrucao_saida[16:12]; 126

end 127

if(instrucao_saida[31:27]==5'b01101) //load 128

begin 129

controle_memoria[1:0]=2'b00; 130

controle_registradores=2'b10; 131

controle_pc=2'b00; 132

endereco_registrador1=instrucao_saida[26:22]; 133

endereco_memoria=instrucao_saida[15:0]; 134

end 135

-

13

if(instrucao_saida[31:27]==5'b01110) //store 136

begin 137

controle_memoria[1:0]=2'b01; 138

controle_pc=2'b00; 139

endereco_registrador1=instrucao_saida[26:22]; 140

endereco_memoria=instrucao_saida[15:0]; 141

end 142

if(instrucao_saida[31:27]==5'b01111) //not 143

begin 144

controle_ula=5'b01001; 145

controle_registradores=2'b01; 146

controle_pc=2'b00; 147

endereco_registrador1=instrucao_saida[26:22]; 148

endereco_registrador2=instrucao_saida[21:17]; 149

endereco_registrador3=instrucao_saida[16:12]; 150

end 151

if(instrucao_saida[31:27]==5'b10000) //noti 152

begin 153

controle_ula=5'b01100; 154

controle_pc=2'b00; 155

endereco_registrador1=instrucao_saida[26:22]; 156

endereco_registrador2=instrucao_saida[21:17]; 157

valor=instrucao_saida[15:0]; 158

end 159

if(instrucao_saida[31:27]==5'b10001) //input 160

begin 161

controle_moduloio=2'b00; 162

controle_pc=2'b00; 163

end 164

if(instrucao_saida[31:27]==5'b10010) //output 165

-

14

begin 166

controle_moduloio=2'b01; 167

controle_pc=2'b00; 168

end 169

if(instrucao_saida[31:27]==5'b10011) //>= 170

begin 171

controle_ula=5'b01110; 172

controle_registradores=2'b01; 173

controle_pc=2'b00; 174

endereco_registrador1=instrucao_saida[26:22]; 175

endereco_registrador2=instrucao_saida[21:17]; 176

endereco_registrador3=instrucao_saida[16:12]; 177

end 178

if(instrucao_saida[31:27]==5'b10100) //>=i 179

begin 180

controle_ula=5'b01111; 181

controle_pc=2'b00; 182

endereco_registrador1=instrucao_saida[26:22]; 183

endereco_registrador2=instrucao_saida[21:17]; 184

valor=instrucao_saida[15:0]; 185

end 186

if(instrucao_saida[31:27]==5'b10101) //loadi 187

begin 188

controle_pc=2'b00; 189

controle_registradores=2'b10; 190

endereco_registrador1=instrucao_saida[26:22]; 191

registrador_memoria=instrucao_saida[15:0]; 192

end 193

end 194

endmodule 195

-

15

Na Figura 2 vemos que controladora est executando corretamente a leitura das

instrues que entram e separando cada bit dela de acordo com a instruo,

enviando os sinais de controles para os mdulos e tambm os endereos de

escrita e, ou, leitura.

Figura 2. Diagrama de ondas para controladora.

Nas prximas linhas veremos ento a descrio para o processamento, o

qual no iremos expor o diagrama de ondas, por ainda no termos carregado a

memria de instrues com instrues, mas os testes apontam o bom

funcionamento de todos os mdulos, estando preparados para ser executado no

FPGA.

module processamento( 196

input clk, 197

output [31:0]testeinstrucao, 198

output [4:0]testereg1, 199

output [4:0]testereg2, 200

output [4:0]testereg3, 201

output [15:0]testula, 202

output [15:0]testememprincipal 203

); 204

205

wire [15:0]pc; 206

wire [31:0]instrucao_saida; 207

wire [1:0]controle_registradores; 208

wire [4:0]endereco_registrador1; 209

-

16

wire [4:0]endereco_registrador2; 210

wire [4:0]endereco_registrador3; 211

wire [15:0]ula; 212

wire [15:0]registrador_memoria; 213

wire [1:0]controle_memoria; 214

wire [15:0]endereco_memoria; 215

wire [15:0]store; 216

wire [3:0]controle_ula; 217

wire [15:0]valor; 218

wire [15:0]valor1; 219

wire [15:0]valor2; 220

wire [15:0]endereco_branch; 221

wire [1:0]controle_pc; 222

wire [15:0]branch; 223

wire [15:0]jump; 224

wire [1:0]controle_moduloio; 225

226

memoriainstrucao(.pc(pc), 227

.clk(clk), 228

.instrucao_saida(instrucao_saida)); 229

controladora(.instrucao_saida(instrucao_saida), 230

.controle_ula(controle_ula), 231

.valor(valor), 232

.endereco_branch(endereco_branch), 233

.controle_registradores(controle_registradores), 234

.endereco_registrador3(endereco_registrador3), 235

.endereco_registrador2(endereco_registrador2), 236

.endereco_registrador1(endereco_registrador1), 237

.controle_memoria(controle_memoria), 238

.endereco_memoria(endereco_memoria), 239

-

17

.jump(jump), 240

.controle_pc(controle_pc), 241

.controle_moduloio(controle_moduloio)); 242

bancoderegistradores(.controle_registradores(controle_registradores), 243

.endereco_registrador1(endereco_registrador1), 244

.endereco_registrador2(endereco_registrador2), 245

.endereco_registrador3(endereco_registrador3), 246

.ula(ula), 247

.registrador_memoria(registrador_memoria), 248

.clk(clk), 249

.valor1(valor1), 250

.valor2(valor2), 251

.store(store)); 252

memoriaprincipal(.controle_memoria(controle_memoria), 253

.endereco_memoria(endereco_memoria), 254

.store(store), 255

.clk(clk), 256

.registrador_memoria(registrador_memoria)); 257

unidadelogicaearitmetica(.controle_ula(controle_ula), 258

.valor1(valor1), 259

.valor2(valor2), 260

.valor(valor), 261

.endereco_branch(endereco_branch), 262

.ula(ula), 263

.branch(branch)); 264

contadordeprograma(.controle_pc(controle_pc), 265

.jump(jump), 266

.branch(branch), 267

.clk(clk), 268

.pc(pc)); 269

-

18

assign testeinstrucao=instrucao_saida; 270

assign testereg1=endereco_registrador1; 271

assign testereg2=endereco_registrador2; 272

assign testereg3=endereco_registrador3; 273

assign testememprincipal=endereco_memoria; 274

assign testula=ula; 275

endmodule 276

-

19

5. DISCUSSES

Depois do que foi apresentado, percebemos que at ento nenhuma parte

apresentou erro de execuo, os erros podero surgir na fase que segue, ou

seja na fase de execuo das descries no FPGA. Podemos dizer tambm, que

no h atraso no cronograma esperado para o projeto, sendo que os testes para

execuo no FPGA j comearam a serem feitos.

-

20

6. REFERNCIAS BIBLIOGRFICAS

1 DIAS, MORGADO: Sistemas Digitais Princpios e Prtica, 3

edio.

2 HARRIS, DAVID MONEY: Digital Design and Computer Architecture;

3 STALLINGS, WILLIAM: Arquitetura e Organizao de

Computadores, 8 edio;