barramentos.pdf

-

Upload

canalhosthospedagemdesites -

Category

Documents

-

view

238 -

download

0

Transcript of barramentos.pdf

-

8/17/2019 barramentos.pdf

1/54

1

Placas MãePlacas MãeComponentes/BarramentosComponentes/Barramentos

-

8/17/2019 barramentos.pdf

2/54

2

Sistemas de barramentosSistemas de barramentosIntel e AMD -CHIPSETIntel e AMD -CHIPSET

VídeoVídeo

PCIPCI

SerialSerialParalelelaParalelela

!dio!dio

ControladoraControladoraIDE"SATA"#DDIDE"SATA"#DD

$SB$SB

Et%ernetEt%ernet

Hyper-Transport

CHIPSET690

-

8/17/2019 barramentos.pdf

3/54

3

Placa mãe para processador Penti!m IIPlaca mãe para processador Penti!m II

-

8/17/2019 barramentos.pdf

4/54

4

Mot%er-board para processadoresMot%er-board para processadoresPenti!m-&Penti!m-&

-

8/17/2019 barramentos.pdf

5/54

5

Placa mãe para processadores d!al corePlaca mãe para processadores d!al core

Processador

Ponte-Norte

Ponte-SulMemória

PCI

IDE

AGP

FDD

-

8/17/2019 barramentos.pdf

6/54

6

#ormato AT e AT'#ormato AT e AT'

AT ()*+,-)**. conecta-se a 0onte atra12s !mAT ()*+,-)**. conecta-se a 0onte atra12s !mconector de )3 pinos4 #ornece tensão de )3V econector de )3 pinos4 #ornece tensão de )3V e5V4 $tili6a-se de conectores DI7 para teclados45V4 $tili6a-se de conectores DI7 para teclados4Desli8amento por %ard9are4Desli8amento por %ard9are4

AT' (a partir de )**. conecta-se a 0onte porAT' (a partir de )**. conecta-se a 0onte por!m conector de 3: (AT' )4:. o! 3& (AT' 34:.!m conector de 3: (AT' )4:. o! 3& (AT' 34:.pinos4 #ornece tensão de )3V" 5V e ,4,V4 $tili6a-pinos4 #ornece tensão de )3V" 5V e ,4,V4 $tili6a-se de conectores Mini-DI7 para teclados4se de conectores Mini-DI7 para teclados4Desli8amento por %ard9are e so0t9are4 E1ol!iDesli8amento por %ard9are e so0t9are4 E1ol!ipara as Mini-AT' e Micro-AT'4para as Mini-AT' e Micro-AT'4

#le;-AT' (Intel." 7ini-IT'" nano-IT'" pico-IT'#le;-AT' (Intel." 7ini-IT'" nano-IT'" pico-IT'(Via. e BT' (Intel.4(Via. e BT' (Intel.4

-

8/17/2019 barramentos.pdf

7/54

7

Plane Circ!it Board - PCBPlane Circ!it Board - PCB

7a placa de circ!ito impresso são soldados os7a placa de circ!ito impresso são soldados osdemais componentes4 < 0ormada por & a ):demais componentes4 < 0ormada por & a ):placas (+ a 3: 0aces.4placas (+ a 3: 0aces.4

Podemos encontrar n!m PCB=Podemos encontrar n!m PCB= Slots de e;pansão>Slots de e;pansão> Soc?et>Soc?et> Banco de mem@ria>Banco de mem@ria> Conectores IDEs>Conectores IDEs>

C%ipsets (7orte e S!l.>C%ipsets (7orte e S!l.> Capacitores" resistores" !mpers" etc444>Capacitores" resistores" !mpers" etc444> Barramentos (ISA" EISA" PCI" AP" $SB" etc444.Barramentos (ISA" EISA" PCI" AP" $SB" etc444. Bios>Bios>

etc444etc444

-

8/17/2019 barramentos.pdf

8/54

8

!e !ma placa-mãe top de lin%a de1e terF !e !ma placa-mãe top de lin%a de1e terF#onte= %ttp=//9994tecm!ndo4com4br/placa-mae/*G*+-o-!e-!ma-placa-mae-top-de-lin%a-de1e-ter-4%tm#onte= %ttp=//9994tecm!ndo4com4br/placa-mae/*G*+-o-!e-!ma-placa-mae-top-de-lin%a-de1e-ter-4%tm

A placa de1e ser 0!t!reproo0>A placa de1e ser 0!t!reproo0> so!ete certo= so!ete certo=

Intel= #CJA)," #CJA ))5:"Intel= #CJA)," #CJA ))5:" #CJA ))55" etc444#CJA ))55" etc444

AMD= AM," #M)" #M3" etc444AMD= AM," #M)" #M3" etc444 c%ipset 0a6 toda di0erenKa> c%ipset 0a6 toda di0erenKa> Compatibilidade com mem@ria DDL, de altaCompatibilidade com mem@ria DDL, de alta

1elocidade (),,,/)::MH6.>1elocidade (),,,/)::MH6.> SATA B para alto desempen%o>SATA B para alto desempen%o> $SB ,4: 2 imprescindí1el>$SB ,4: 2 imprescindí1el>

Mltiplos slots PCI-E;press>Mltiplos slots PCI-E;press> Adicionais são sempre bem-1indos (Placa de redeAdicionais são sempre bem-1indos (Placa de rede

i8abit / Som / Bl!etoot% / G"+ canais / HDMI / etc444.i8abit / Som / Bl!etoot% / G"+ canais / HDMI / etc444.

-

8/17/2019 barramentos.pdf

9/54

9

nBoard ; 00BoardnBoard ; 00Board

nBoard !ma placa mãe com dispositi1osnBoard !ma placa mãe com dispositi1osonboard inte8ra placa de som" placa de 1ídeoonboard inte8ra placa de som" placa de 1ídeo(opcional. e placa de rede4(opcional. e placa de rede4

- C!sto / - N!alidade- C!sto / - N!alidade

00Board os dispositi1os são acoplados a placa00Board os dispositi1os são acoplados a placamãe atra12s de slots de e;pansão4mãe atra12s de slots de e;pansão4

O C!sto / O N!alidadeO C!sto / O N!alidade

A opKão por onboard o! o00board se d peloA opKão por onboard o! o00board se d peloclc!lo de c!sto ; bene0ício4clc!lo de c!sto ; bene0ício4

-

8/17/2019 barramentos.pdf

10/54

10

Barramento= de0iniKãoBarramento= de0iniKão

barramento de !m sistema de comp!taKão 2 o barramento de !m sistema de comp!taKão 2 oelemento respons1el pela interli8aKão doselemento respons1el pela interli8aKão dosdemais componentes" cond!6indo de mododemais componentes" cond!6indo de modosincroni6ado o 0l!;o de in0ormaKQes de dados"sincroni6ado o 0l!;o de in0ormaKQes de dados"endereKos e sinais de controle- de acordo comendereKos e sinais de controle- de acordo com

!ma pro8ramaKão de ati1idade pre1iamente!ma pro8ramaKão de ati1idade pre1iamentede0inida pela $C4de0inida pela $C4

barramento em !m sistema comp!tacional barramento em !m sistema comp!tacionaldi1ide-se em=di1ide-se em=

)- Barramento de dados>)- Barramento de dados>

3- Barramento de endereKos>3- Barramento de endereKos>

,- Barramento de controle4,- Barramento de controle4

-

8/17/2019 barramentos.pdf

11/54

11

Compartil%amento entreCompartil%amento entredispositi1os de !m sistemadispositi1os de !m sistema

comp!tacionalcomp!tacional$CP Mem@ria

Dispositi1oEntrada

Dados

EndereKo

Controle

-

8/17/2019 barramentos.pdf

12/54

12

Consiste em múltiplas linhas condutoras cadaConsiste em múltiplas linhas condutoras cadauma permitindo a passagem de um it deuma permitindo a passagem de um it dein!orma"#o $se%a de uma instru"#o ou de umin!orma"#o $se%a de uma instru"#o ou de um

dado&' (ais arramentos possuem di!erentesdado&' (ais arramentos possuem di!erentestamanhos $)uantidades de its&* dependendotamanhos $)uantidades de its&* dependendodo modelo do processador utili+ado' ,aloresdo modelo do processador utili+ado' ,alorestpicos s#o .* /0* 12* 03 e /2. its'tpicos s#o .* /0* 12* 03 e /2. its'

Barramento de dadosBarramento de dados

-

8/17/2019 barramentos.pdf

13/54

13

Barramento de endereKosBarramento de endereKos 4 arramento de endere"o 5 utili+ado para o4 arramento de endere"o 5 utili+ado para o

processador indicar de onde )uer l6 $uscar& umprocessador indicar de onde )uer l6 $uscar& umdado ou para onde dese%a gra78-lo'dado ou para onde dese%a gra78-lo'Normalmente* a )uantidade de its de umNormalmente* a )uantidade de its de umendere"o espec!ica a m89ima capacidade de umendere"o espec!ica a m89ima capacidade de ummódulo de memória principal'módulo de memória principal'

4 7alor in8rio colocado no arramento de4 7alor in8rio colocado no arramento deendere"os* tam5m pode representar o endere"oendere"os* tam5m pode representar o endere"ode um dispositi7o de entrada e sada' Em geral*de um dispositi7o de entrada e sada' Em geral*

um ou mais its do endere"o* mostram se oum ou mais its do endere"o* mostram se oendere"o indicado se re!ere a um módulo deendere"o indicado se re!ere a um módulo dememória principal ou dispositi7o de E:S'memória principal ou dispositi7o de E:S'

-

8/17/2019 barramentos.pdf

14/54

14

Barramento de controleBarramento de controle 4 arramento de controle 5 constitudo de inúmeras4 arramento de controle 5 constitudo de inúmeras

linhas pela )uais !luem sinais espec!icos dalinhas pela )uais !luem sinais espec!icos daprograma"#o do sistema'programa"#o do sistema'

Sinais de controleSinais de controle comumente empregados noscomumente empregados nosarramentos de controle s#o;arramentos de controle s#o;

Jeit!ra de dadosJeit!ra de dados $&- sinali+a para o$&- sinali+a para ocontrolador de memória decodi!icar o endere"ocontrolador de memória decodi!icar o endere"ocolocado no arramento de endere"os e trans!erir ocolocado no arramento de endere"os e trans!erir oconteúdo do arramento de dados para as c5lulasconteúdo do arramento de dados para as c5lulaspara o arramento de dados'para o arramento de dados'

Escrita de dadosEscrita de dados $&- sinali+a para$&- sinali+a parao controlador de memória decodi!icar colocado noo controlador de memória decodi!icar colocado noarramento de endere"os e trans!erir o conteúdoarramento de endere"os e trans!erir o conteúdodo arramento de dados para as c5lulasdo arramento de dados para as c5lulasespeci!icadas'especi!icadas'

-

8/17/2019 barramentos.pdf

15/54

15

Sinais de controleSinais de controle

Jeit!ra de E/S (I/ read.Jeit!ra de E/S (I/ read. @ processo semelhante@ processo semelhanteao de leitura de dados na memória'ao de leitura de dados na memória'

Escrita de E/S (I/ 9rite.Escrita de E/S (I/ 9rite. @ processo semelhante@ processo semelhanteao de leitura de dados na memória'ao de leitura de dados na memória'

Certi0icaKão de trans0erRncia de dadosCerti0icaKão de trans0erRncia de dados(trans0er AC.(trans0er AC. @ o dispositi7o acusa o t5rmino da@ o dispositi7o acusa o t5rmino datrans!er6ncia para a CPtrans!er6ncia para a CP

Pedido de interr!pKão (Interr!pt re!est.Pedido de interr!pKão (Interr!pt re!est. @@Indica ocorr6ncia de uma interrup"#o'Indica ocorr6ncia de uma interrup"#o'

Lel@8io (cloc?.Lel@8io (cloc?. @ por onde passam os pulsos de@ por onde passam os pulsos desincroni+a"#o dos e7entos durante o !uncionamentosincroni+a"#o dos e7entos durante o !uncionamentodo sistema'do sistema'

-

8/17/2019 barramentos.pdf

16/54

16

Tipos de barramentosTipos de barramentos

At!almente os modelos de or8ani6aKãoAt!almente os modelos de or8ani6aKãode sistemas de comp!taKão adotadosde sistemas de comp!taKão adotadospelos 0abricantes poss!em di0erentespelos 0abricantes poss!em di0erentestipos de barramentos4tipos de barramentos4

Barramento localBarramento local == < o barramento de maior 1elocidade de< o barramento de maior 1elocidade de

trans0erRncia de dados" 0!ncionando"trans0erRncia de dados" 0!ncionando"normalmente" na mesma 0reRncia donormalmente" na mesma 0reRncia dorel@8io do processador4rel@8io do processador4

Este barramento cost!ma interli8ar oEste barramento cost!ma interli8ar oprocessador aos dispositi1os de maiorprocessador aos dispositi1os de maior1elocidade (para não atrasar as1elocidade (para não atrasar asoperaKQes do processador." !e são=operaKQes do processador." !e são= Mem@ria cac%eMem@ria cac%e Mem@ria principal4Mem@ria principal4

-

8/17/2019 barramentos.pdf

17/54

17

Barramento de sistemaBarramento de sistema ;; Alguns !aricantesAlguns !aricantesadotam o modelo em )ue o arramento localadotam o modelo em )ue o arramento localinterliga o processador B memória cache e estainterliga o processador B memória cache e estase interliga aos módulos de memória principalse interliga aos módulos de memória principal$AM& por um outro arramento denominado$AM& por um outro arramento denominadoarramento do sistema* de modo a n#o permitirarramento do sistema* de modo a n#o permitiracesso do processador diretamente B memóriaacesso do processador diretamente B memória

principal' ma inter!ace de controle sincroni+a oprincipal' ma inter!ace de controle sincroni+a oacesso entre as memórias'acesso entre as memórias'

Barramento de e;pansãoBarramento de e;pansão ;; onde se interligamonde se interligamos dispositi7os de E:S* como discos magn5ticos*os dispositi7os de E:S* como discos magn5ticos*

7deos* impressoras* D,Ds* CD-4Ms* etc' Este7deos* impressoras* D,Ds* CD-4Ms* etc' Estearramento se conecta ao arramento do sistemaarramento se conecta ao arramento do sistemapor inter!aces de controle $costumam serpor inter!aces de controle $costumam serconhecidas comoconhecidas como pontes ou ridgespontes ou ridges&* )ue&* )uesincroni+am as di!erentes 7elocidades dossincroni+am as di!erentes 7elocidades dos

arramentos'arramentos'

-

8/17/2019 barramentos.pdf

18/54

18

Modelo con1encional deModelo con1encional debarramentobarramento

Memória

Principal

CacheUCP

Barramento do Sistema

Ponte

Inter!ace"

Barramento de E/S (Expansão)

Tecla#o Mo#em $e#e SCSI= Small Computer System

Interface

Barramento Jocal

-

8/17/2019 barramentos.pdf

19/54

19

Modelo aper0eiKoado de barramentoModelo aper0eiKoado de barramento

$CP Cac%e

PonteMem@riaPrincipal

Barramento do sistema

Ponte

Barramento de E/S de alta 1elocidade (PCI o! AP.

,deo ede

Barramento de E/S de con1encional (ISA.

Modem (eclado Mouse

SCSI Ponte

Barramento local

-

8/17/2019 barramentos.pdf

20/54

20

A largura ou tamanho de um arramento 5 uma unidade deA largura ou tamanho de um arramento 5 uma unidade demedida )ue caracteri+a a )uantidade de in!orma"es $itsmedida )ue caracteri+a a )uantidade de in!orma"es $itsem geral& )ue pode !luir simultaneamente pelo arramento'em geral& )ue pode !luir simultaneamente pelo arramento'

No caso de !ia"#o consiste na )uantidade de !ios paralelosNo caso de !ia"#o consiste na )uantidade de !ios paralelose9istentes no arramento* ao passo )ue em circuitose9istentes no arramento* ao passo )ue em circuitosimpressos $placas&* consiste nos tra"os impressos na placaimpressos $placas&* consiste nos tra"os impressos na placacom material condutor* por onde !lui a corrente el5trica'com material condutor* por onde !lui a corrente el5trica'

Esta largura* maior ou menor* se constitui tam5m em umEsta largura* maior ou menor* se constitui tam5m em umdos elementos )ue a!etam a medida de desempenho de umdos elementos )ue a!etam a medida de desempenho de umsistema* %untamente com a dura"#o de cada it ou sinal' Asistema* %untamente com a dura"#o de cada it ou sinal' Ata9a de trans!er6ncia* )ue* em geral* 5 dada em its $ its*ta9a de trans!er6ncia* )ue* em geral* 5 dada em its $ its*Mits& por segundo* depende !undamentalmente da larguraMits& por segundo* depende !undamentalmente da largurado arramento'do arramento'

4 inter7alo de tempo re)uerido para mo7er um grupo de4 inter7alo de tempo re)uerido para mo7er um grupo deits ao longo do arramento 5 denominadoits ao longo do arramento 5 denominado ciclo de tempociclo de tempo do arramento ou simplesmentedo arramento ou simplesmente ciclo do barramentociclo do barramento $&'$&'

l dP l d

-

8/17/2019 barramentos.pdf

21/54

21

Protocolos deProtocolos debarramentobarramento

Para entender o !uncionamento do arramento dePara entender o !uncionamento do arramento deum computador* 5 preciso en!ati+ar o aspecto doum computador* 5 preciso en!ati+ar o aspecto docompartilhamento )ue caracteri+a essecompartilhamento )ue caracteri+a essecomponente* ou se%a* o arramento interligacomponente* ou se%a* o arramento interligadi7ersos componentes as in!orma"es só podemdi7ersos componentes as in!orma"es só podem

!luir uma de cada 7e+* sen#o ha7er8 colis#o e a!luir uma de cada 7e+* sen#o ha7er8 colis#o e ain!orma"#o ser8 perdida'in!orma"#o ser8 perdida'

argura do arramento; )uantidade deargura do arramento; )uantidade de

in!orma"#o $num de its& )ue pode !luir peloin!orma"#o $num de its& )ue pode !luir peloarramentoarramento

Protocolos de arramento; padres adotados paraProtocolos de arramento; padres adotados para

a sincroni+a"#o* largura* m5todo de acesso ea sincroni+a"#o* largura* m5todo de acesso e7elocidade'7elocidade'

-

8/17/2019 barramentos.pdf

22/54

22

Ta;as de trans0erRnciaTa;as de trans0erRncia; de!ine o; de!ine onúmero m89imo denúmero m89imo de =tes=tes )ue o)ue oarramento pode trans!erir'arramento pode trans!erir'

E9emplo /;E9emplo /;

Pentium 3 com HS de 12 itsPentium 3 com HS de 12 itstraalhando a 3MJ+;traalhando a 3MJ+;

12 its K 3 =tes12 its K 3 =tes

ta9a K 3 L 3MJ+ta9a K 3 L 3MJ+

ta9a K /0MH:sta9a K /0MH:s

-

8/17/2019 barramentos.pdf

23/54

23

4s próprios !aricante de CP t6m procurado4s próprios !aricante de CP t6m procuradocriar uma padroni+a"#o na de!ini"#o decriar uma padroni+a"#o na de!ini"#o deprotocolos* com a inten"#o de !acilitar a cone9#oprotocolos* com a inten"#o de !acilitar a cone9#ode uma gama maior de componentes'de uma gama maior de componentes'

$7IB$S$7IB$S; $de!inido pela Digital E)uipment Co'& @; $de!inido pela Digital E)uipment Co'& @DEC* praticamente !ora de usoDEC* praticamente !ora de uso

MCAMCA @ Micro Channel Architecture $de!inido pela@ Micro Channel Architecture $de!inido pelaIHM* para o sistema PS-2&' Nunca conseguiuIHM* para o sistema PS-2&' Nunca conseguiuado"#o por outro !aricante* nem mesmo a IHM oado"#o por outro !aricante* nem mesmo a IHM oadotou por completo* tendo sido aandonado'adotou por completo* tendo sido aandonado'

Tipo de protocolosTipo de protocolos

-

8/17/2019 barramentos.pdf

24/54

24

ISAISA (Industry Standard Architecture)(Industry Standard Architecture) Harramento do PC da IHM !oi padr#o de !ato para osHarramento do PC da IHM !oi padr#o de !ato para os

sistemas aseados no processador ...* pois )uase todossistemas aseados no processador ...* pois )uase todosos clones de PC eram aseados nele' Para tornar poss7el oos clones de PC eram aseados nele' Para tornar poss7el oapro7eitamento em seus sistemas de placas de E:Sapro7eitamento em seus sistemas de placas de E:S!aricadas por terceiros'!aricadas por terceiros'

Características:Características: 4 arramento PC da IHM possua 02 linhas de sinais*4 arramento PC da IHM possua 02 linhas de sinais*

sendo;sendo; 2 linhas para endere"ar a memória$Capacidade de2 linhas para endere"ar a memória$Capacidade de

endere"ar /MH=tes &endere"ar /MH=tes & . linhas para dados. linhas para dados

/ linha para ati7ar a leitura na memória/ linha para ati7ar a leitura na memória / linha para ati7ar a escrita na memória/ linha para ati7ar a escrita na memória / linha para ati7ar leitura de E:S/ linha para ati7ar leitura de E:S / linha para ati7ar a escrita em E:S/ linha para ati7ar a escrita em E:S Al5m dessas e9istiam tam5m linhas de sinais paraAl5m dessas e9istiam tam5m linhas de sinais para

re)uisi"#o e garantia de interrup"es e utili+a"#o dare)uisi"#o e garantia de interrup"es e utili+a"#o dat5cnica DMA't5cnica DMA'

-

8/17/2019 barramentos.pdf

25/54

25

PC-A( e9igia um us de /0 its compat7elPC-A( e9igia um us de /0 its compat7el

com I:4 Channelcom I:4 Channel /0 its de dados/0 its de dados !re)6ncia; .MJ+!re)6ncia; .MJ+ ta9a K /0MH:s'ta9a K /0MH:s'

Detalhes do conector $& ISA

ISAISA (Industry Standard Architecture)(Industry Standard Architecture)

-

8/17/2019 barramentos.pdf

26/54

26

EISAEISA (Extend Industry Standard Architecture)(Extend Industry Standard Architecture)

Proposto pela Compa) para ser compat7elProposto pela Compa) para ser compat7elcom o ISA-/0* adicionando no7os recursos;com o ISA-/0* adicionando no7os recursos; Harramento de dados de 12 itsHarramento de dados de 12 its Fre)6ncia de opera"#o compat7elFre)6ncia de opera"#o compat7el

$.MJ+&'$.MJ+&' ta9a K 12MH:sta9a K 12MH:s

Slot muito parecido com o ISA* por5m maisSlot muito parecido com o ISA* por5m maisalto e com percurso limitado'alto e com percurso limitado'

4 arramento EISA 5 compat7el com o4 arramento EISA 5 compat7el com oarramento ISA* entretanto pode trans!erir 3arramento ISA* entretanto pode trans!erir 3=tes por ciclo* en)uanto o ISA só pode=tes por ciclo* en)uanto o ISA só podetrans!erir 2 =tes por ciclo' Assim*otrans!erir 2 =tes por ciclo' Assim*o

arramento EISA pode alcan"ar 11*1 Mh+'arramento EISA pode alcan"ar 11*1 Mh+'

-

8/17/2019 barramentos.pdf

27/54

27

EISAEISA (Extend Industry Standard(Extend Industry Standard Architecture) Architecture)

-

8/17/2019 barramentos.pdf

28/54

28

VJB VESA Jocal B!sVJB VESA Jocal B!s VESAVESA (( Video Electronic Standards AssociationVideo Electronic Standards Association ) )

At5 ent#o os arramentos eram muito lentosAt5 ent#o os arramentos eram muito lentospara o processamento de imagens'para o processamento de imagens' Harramento de dados; 12 itsHarramento de dados; 12 its

Fre)6ncia id6ntica a !re)6ncia deFre)6ncia id6ntica a !re)6ncia dearramento do processadorarramento do processador

E9; para um 3.0D3-/ )ue traalhaE9; para um 3.0D3-/ )ue traalhacom um arramento a 11MJ+* o uscom um arramento a 11MJ+* o us

,H teria;,H teria;

ta9a K 3L11M K /12MH:sta9a K 3L11M K /12MH:s $podendo$podendochegar a 3MH:s&chegar a 3MH:s&

-

8/17/2019 barramentos.pdf

29/54

29

VJB VESA Jocal B!sVJB VESA Jocal B!s

-

8/17/2019 barramentos.pdf

30/54

30

PCIPCI (Peripheral Component Interconnect)(Peripheral Component Interconnect)

Desen7ol7ido pela Intel* tornando-se )uase umDesen7ol7ido pela Intel* tornando-se )uase um

padr#o para todo o mercado* como arramentopadr#o para todo o mercado* como arramentode E:S de alta 7elocidade'de E:S de alta 7elocidade'

Permite trans!er6ncia de dados em 12 e 03 its aPermite trans!er6ncia de dados em 12 e 03 its a7elocidade de 11MJ+ e de 00MJ+* no m89imo'7elocidade de 11MJ+ e de 00MJ+* no m89imo'

Interconecta-se ao arramento local e outroInterconecta-se ao arramento local e outroarramento* tipo ISA* atra75s de um circuito paraarramento* tipo ISA* atra75s de um circuito paracompatiili+ar as di!erentes caractersticas entrecompatiili+ar as di!erentes caractersticas entreeles'eles'

Apresenta ta9as de trans!er6ncia de at5 /12Apresenta ta9as de trans!er6ncia de at5 /12MH:s* com 12 itsMH:s* com 12 its

Possui suporte para o padr#o PnP $Plug and Pla=&Possui suporte para o padr#o PnP $Plug and Pla=&

-

8/17/2019 barramentos.pdf

31/54

31

PCIPCIPerip%eral ComponentPerip%eral ComponentInterconnectedInterconnected

-

8/17/2019 barramentos.pdf

32/54

32

PCIPerip%eral ComponentPCIPerip%eral ComponentInterconnectedInterconnected

-

8/17/2019 barramentos.pdf

33/54

33

PCIPCI (Peripheral Component(Peripheral ComponentInterconnect)Interconnect)

Cone9#o do us do microprocessadorCone9#o do us do microprocessadorcom arramento PCI 5 atra75s decom arramento PCI 5 atra75s deum chip chamadoum chip chamado P4N(E HS 4CAP4N(E HS 4CA

@ PCI@ PCI

J8 duas pontes;J8 duas pontes; Norte; Conecta o HS 4CA ao PCINorte; Conecta o HS 4CA ao PCI Sul; Conecta o PCI ao ISA'Sul; Conecta o PCI ao ISA'

-

8/17/2019 barramentos.pdf

34/54

34

PCIPCI (Peripheral Component(Peripheral ComponentInterconnect)Interconnect)

Microprocessador Cac%eB$S local

Ponte7orte

PCI

HD

Vídeo

PonteS!l

ISADispositi1o A

Dispositi1o B

Peri02ricosJentos

LM

Barramento '

Mem@riaPrincipal

-

8/17/2019 barramentos.pdf

35/54

35

PCI-'PCI-' (Peripheral Component Interconnect Extended)(Peripheral Component Interconnect Extended)

PCI-'PCI-' $Peripheral Component Interconnect$Peripheral Component InterconnectE9tended& !oi desen7ol7ido para melhorar aE9tended& !oi desen7ol7ido para melhorar aper!ormance do arramento PCI de 03per!ormance do arramento PCI de 03 bitsbits' A' Aprincipal di!eren"a* com rela"#o ao PCIprincipal di!eren"a* com rela"#o ao PCI

tradicional* 5 o aumento da !re)6ncia detradicional* 5 o aumento da !re)6ncia deopera"#o* )ue s#o duas; / e /11opera"#o* )ue s#o duas; / e /11 M!M!''

4 arramento PCI- de /11 MJ+ 5 capa+ de4 arramento PCI- de /11 MJ+ 5 capa+ de

trans!erir /03trans!erir /03 M"#sM"#s* a mesma ta9a de* a mesma ta9a deopera"#o do AGP 39' N#o con!undir PCI- comopera"#o do AGP 39' N#o con!undir PCI- comPCI-E9press'PCI-E9press'

-

8/17/2019 barramentos.pdf

36/54

36

Esta 5 uma e7olu"#o do PCI de 03 its* )ueEsta 5 uma e7olu"#o do PCI de 03 its* )ued8 mais um passo adiante em termos ded8 mais um passo adiante em termos de7elocidade*7elocidade* mant5m a compatiilidade commant5m a compatiilidade comas placas PCI atuaisas placas PCI atuais''

Na 7erdade* as e7olu"es do PCI- seNa 7erdade* as e7olu"es do PCI- selimitam ao n7el lógico e a uma maiorlimitam ao n7el lógico e a uma maior!re)6ncia de opera"#o' 4 número de!re)6ncia de opera"#o' 4 número detrilhas e o !ormato !sico dos slots continuatrilhas e o !ormato !sico dos slots continuao mesmo'o mesmo'

E9istem duas 7erses do PCI-* )ue operamE9istem duas 7erses do PCI-* )ue operamaa )::):: e ae a ),,),, MJ+* sempre com 03 its porMJ+* sempre com 03 its porciclo de clocO'ciclo de clocO'

4 PCI- 5 um sucessor natural para o PCI de4 PCI- 5 um sucessor natural para o PCI de

03 its nos ser7idores'03 its nos ser7idores'

PCI-'PCI-' (Peripheral Component Interconnect Extended)(Peripheral Component Interconnect Extended)

-

8/17/2019 barramentos.pdf

37/54

37

PCI-'PCI-' (Peripheral Component(Peripheral ComponentInterconnect Extended )Interconnect Extended )

-

8/17/2019 barramentos.pdf

38/54

38

PCI E;pressPCI E;press A tecnologia PCI E9press conta com um recurso )ueA tecnologia PCI E9press conta com um recurso )ue

permite o uso de uma ou mais cone9es seriais* isto 5*permite o uso de uma ou mais cone9es seriais* isto 5*

caminhos $tam5m chamados de lanes& paracaminhos $tam5m chamados de lanes& paratrans!er6ncia de dados'trans!er6ncia de dados'

Se um determinado dispositi7o usa um caminho*Se um determinado dispositi7o usa um caminho*ent#o di+-se )ue este utili+a o arramento PCI E9pressent#o di+-se )ue este utili+a o arramento PCI E9press/*/*

Se utili+a 3 cone9es* sua denomina"#o 5 PCI E9pressSe utili+a 3 cone9es* sua denomina"#o 5 PCI E9press3 e assim por diante' Cada lane pode ser3 e assim por diante' Cada lane pode seridirecional* ou se%a* recee e en7ia dados'idirecional* ou se%a* recee e en7ia dados'

Cada cone9#o usada no PCI E9press traalha com .Cada cone9#o usada no PCI E9press traalha com .its por 7e+* sendo 3 em cada dire"#o' A !re)6nciaits por 7e+* sendo 3 em cada dire"#o' A !re)6nciausada 5 de 2*Q GJ+* mas esse 7alor pode 7ariar' Assimusada 5 de 2*Q GJ+* mas esse 7alor pode 7ariar' Assim

sendo* o PCI E9press / consegue traalhar com ta9assendo* o PCI E9press / consegue traalhar com ta9asde 2Q MH por segundo* um 7alor em maior )ue osde 2Q MH por segundo* um 7alor em maior )ue os/12 MH do padr#o PCI'/12 MH do padr#o PCI'

Atualmente* o padr#o PCI E9press traalha com at5Atualmente* o padr#o PCI E9press traalha com at5/0* o e)ui7alente a 3 MH:s' Certamente* com o/0* o e)ui7alente a 3 MH:s' Certamente* com opassar do tempo* esse limite aumentar8'passar do tempo* esse limite aumentar8'

PCI EPCI E;press

-

8/17/2019 barramentos.pdf

39/54

39

PCI E;pressPCI E;press

Conector PCI E9pres

macho

Conector PCI E9pres !6mea $S4(&

-

8/17/2019 barramentos.pdf

40/54

40

PCI E;pressPCI E;press

PCI 7s PCI 7s PCI E9press

-

8/17/2019 barramentos.pdf

41/54

41

PCI 7s' PCI- 7s' PCI E9press

http://images.tomshardware.com/2006/05/22/six_975x_enthusiast_motherboards_for_today_and_tomorrow/asus2_975x_board_big.jpg

-

8/17/2019 barramentos.pdf

42/54

42

PCI PCI - PCI-e9p

i

http://images.tomshardware.com/2006/05/22/six_975x_enthusiast_motherboards_for_today_and_tomorrow/asus2_975x_board_big.jpghttp://images.tomshardware.com/2006/05/22/six_975x_enthusiast_motherboards_for_today_and_tomorrow/asus2_975x_board_big.jpghttp://images.tomshardware.com/2006/05/22/six_975x_enthusiast_motherboards_for_today_and_tomorrow/asus2_975x_board_big.jpghttp://images.tomshardware.com/2006/05/22/six_975x_enthusiast_motherboards_for_today_and_tomorrow/asus2_975x_board_big.jpghttp://images.tomshardware.com/2006/05/22/six_975x_enthusiast_motherboards_for_today_and_tomorrow/asus2_975x_board_big.jpghttp://images.tomshardware.com/2006/05/22/six_975x_enthusiast_motherboards_for_today_and_tomorrow/asus2_975x_board_big.jpg

-

8/17/2019 barramentos.pdf

43/54

43

pci

Pci - 9

Pci - e9press

-

8/17/2019 barramentos.pdf

44/54

44

PCIPCIPerip%eral ComponentPerip%eral ComponentInterconnectedInterconnected

AP ( l d hi )($A l t d % hi P t&)

-

8/17/2019 barramentos.pdf

45/54

45

APAP ($Accelerated %raphics Port&)($Accelerated %raphics Port&) Harramento desen7ol7ido por 78rios !aricantes*Harramento desen7ol7ido por 78rios !aricantes*

por5m* liderados pela Intel* com o propósito depor5m* liderados pela Intel* com o propósito de

acelerar as trans!er6ncias de dados do 7deo paraacelerar as trans!er6ncias de dados do 7deo paraa memória* especialmente dados para 1D' (rata-a memória* especialmente dados para 1D' (rata-se* pois* de um arramento espec!ico $parase* pois* de um arramento espec!ico $para7deo&* n#o gen5rico* por5m* de alta 7elocidade7deo&* n#o gen5rico* por5m* de alta 7elocidadede trans!er6ncia por ligar 7deo diretamente Bde trans!er6ncia por ligar 7deo diretamente B

memória principal'memória principal'

-

8/17/2019 barramentos.pdf

46/54

46

bUeti1o= 8r0icos ,D e 1ídeosbUeti1o= 8r0icos ,D e 1ídeos

full'motionfull'motion

>>

Disponí1el a partir do Penti!m II>Disponí1el a partir do Penti!m II> Conector semel%ante ao PCI>Conector semel%ante ao PCI>

Microprocessador Cac%e

B$S local

Ponte7orte

PCISlots PCI444

PonteS!l

Barramento '

Slot APMem@riaPrincipal

APAP ($Accelerated %raphics Port&)($Accelerated %raphics Port&)

-

8/17/2019 barramentos.pdf

47/54

47

AGP usa a memória do microcomputadorAGP usa a memória do microcomputadorpara a renderi+a"#o* permitindo r8pidapara a renderi+a"#o* permitindo r8pidaatuali+a"#o pelo processadoratuali+a"#o pelo processador

Geralmente h8 apenasGeralmente h8 apenas um único slotum único slot* pois* poisaplica-se a 7deoaplica-se a 7deo

(a9as; (a9as; 200MH:s $/9&200MH:s $/9&

Q11MH:s $29&Q11MH:s $29& /GH:s $39&/GH:s $39& 2'/GH:s $.9&'2'/GH:s $.9&'

APAP ($Accelerated %raphics Port&)($Accelerated %raphics Port&)

-

8/17/2019 barramentos.pdf

48/54

48

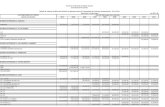

ComparaKão entre o AP e o PCI E;pressComparaKão entre o AP e o PCI E;press

PCI E9press /0; 3 MH:s

PCI E9press .; 2 MH:sAGP .; 2/2. MH:s

PCI E9press 2; Q MH:sAGP 3; /03 MH:s

PCI E9press /; 2Q MH:sAGP /; 200 MH:s

-

8/17/2019 barramentos.pdf

49/54

49

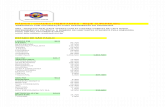

$SB - $ni1ersal Serial B!s$SB - $ni1ersal Serial B!s

$m padrão de barramento e;terno !e$m padrão de barramento e;terno !epermite a cone;ão de 1rios peri02ricospermite a cone;ão de 1rios peri02ricose;ternos ao comp!tador" atra12s de !mae;ternos ao comp!tador" atra12s de !manica inter0ace e !m nico protocolo"nica inter0ace e !m nico protocolo"eliminando a necessidade de instalaKão eeliminando a necessidade de instalaKão econ0i8!raKão de placas e;tras4 $tili6acon0i8!raKão de placas e;tras4 $tili6a!atro contatos 3 para dados () para!atro contatos 3 para dados () paraen1iar e o!tro para receber. e 3 paraen1iar e o!tro para receber. e 3 paratransmissão de ener8ia (345 9atts.4transmissão de ener8ia (345 9atts.4

-

8/17/2019 barramentos.pdf

50/54

50

$SB - $ni1ersal Serial B!s$SB - $ni1ersal Serial B!s

VersQes=VersQes=

)4;. Transmitem apenas )"5 MB/s (o! seUa")4;. Transmitem apenas )"5 MB/s (o! seUa")3 me8abits.)3 me8abits.

34:. Transmitem at2 : MB/s (o! seUa" &+:34:. Transmitem at2 : MB/s (o! seUa" &+:me8abits.me8abits.

,4:. Transmitem at2 :: MB/s (o! seUa" &"+,4:. Transmitem at2 :: MB/s (o! seUa" &"+8i8abits.8i8abits.

-

8/17/2019 barramentos.pdf

51/54

51

$SB - $ni1ersal Serial B!s$SB - $ni1ersal Serial B!sTipos=Tipos=

Tipo A/MTipo A/M mais com!m" padrão mais com!m" padrão!tili6ado nos pendri1es>!tili6ado nos pendri1es>

Tipo B/MTipo B/M conector !adrado" conector !adrado"!tili6ado em impressoras" modems!tili6ado em impressoras" modemsadsl e o!tros dispositi1os>adsl e o!tros dispositi1os>

Tipo Mini-$SB 5P/M e Mini-$SB &P/MTipo Mini-$SB 5P/M e Mini-$SB &P/M

!tili6ado em cel!lares" cmeras!tili6ado em cel!lares" cmerasdi8itais" mp,plaWers" palmtopsdi8itais" mp,plaWers" palmtopse o!tros dispositi1os4e o!tros dispositi1os4

-

8/17/2019 barramentos.pdf

52/54

52

$SB - $ni1ersal Serial B!s$SB - $ni1ersal Serial B!sTipos=Tipos=

Tipo Micro-$SB (A e B.Tipo Micro-$SB (A e B. !tili6ado em cel!lares" !tili6ado em cel!lares"cmeras di8itais" mp,plaWers" palmtopscmeras di8itais" mp,plaWers" palmtopse o!tros dispositi1os4 Ta;a de trans0erencia dee o!tros dispositi1os4 Ta;a de trans0erencia de

&+: Mbps4&+: Mbps4

%

%

%&

-

8/17/2019 barramentos.pdf

53/54

53

$SB - $ni1ersal Serial B!s$SB - $ni1ersal Serial B!s

USB 3.0 A-Type

(no)n a* +S,perSpee#+- i* commonl. !o,n# on ho*t controller* in comp,ter* an# h,/*-

the &*t.le connector i* a !lat- rectan,lar inter!ace Thi* inter!ace hol#* the connection in

place /. !riction )hich mae* it er. ea*. !or ,*er* to connect an# #i*connect In*tea# o!

ro,n# pin*- the connector ,*e* !lat contact* )hich can )ith*tan# contin,o,* attachment an#remoal er. )ell The &*ocet connector proi#e* a +#o)n*tream+ connection that i*

inten#e# !or ,*e *olel. on ho*t controller* an# h,/* Thi* connector i* *imilar in *ie an#

*hape to the &T.pe connector ,*e# in S% 20 S% 11 application* Ho)eer- the S%

30 &t.pe ha* a##itional pin* that are not !o,n# in the S% 20 S% 11 &T.pe The S%

30 connector i* #e*ine# !or S% S,perSpee# application*- ho)eer- it )ill carr. #ata !rom

*lo)er *pee# connection*- an# it i* /ac)ar#* compati/le )ith S% 20 port* S% 30 &

connector* are o!ten /l,e in color to help i#enti!. them !rom preio,* er*ion*

.! "#ps ($00 %Bps)

-

8/17/2019 barramentos.pdf

54/54

$SB - $ni1ersal Serial B!s$SB - $ni1ersal Serial B!s

$m padrão de barramento de dados !e$m padrão de barramento de dados !epermite a cone;ão de 1rios peri02ricospermite a cone;ão de 1rios peri02ricose;ternos ao comp!tador" atra12s de !mae;ternos ao comp!tador" atra12s de !manica inter0ace e !m nico protocolo"nica inter0ace e !m nico protocolo"eliminando a necessidade de instalaKão eeliminando a necessidade de instalaKão econ0i8!raKão de placas e;tras4con0i8!raKão de placas e;tras4