MODELAGEM E CONTROLE DE CONVERSORES ......(BM) é multiplicada ao ganho do conversor QZ-source. Na...

Transcript of MODELAGEM E CONTROLE DE CONVERSORES ......(BM) é multiplicada ao ganho do conversor QZ-source. Na...

MODELAGEM E CONTROLE DE CONVERSORES ELEVADORES DETENSÃO BASEADOS NO CONVERSOR QZ-SOURCE

Tiago M. K. Faistel1, António M. S. S. Andrade2, Ronaldo A. Guisso1, Éder Bridi1, Wagner A. Ayres1,Hélio L. Hey1, Mário L. S. Martins 1

1Universidade Federal de Santa Maria, Santa Maria – RS, Brasil2Universidade Federal de Santa Maria, Cachoeira do Sul – RS, Brasile-mail: [email protected], [email protected]

Resumo – Este artigo apresenta um conjunto de quatroconversores elevadores de tensão CC-CC, baseados noconversor QZ-source e em células de circuitos elevadoresde tensão do tipo boost e super-lift. Ao associar ascélulas elevadoras de tensão na entrada do conversor QZ-source, dependendo da configuração, o ganho desses podemultiplicar ou somar com o ganho de tensão do conversorQZ-source. Com o intuito de demonstrar a simplicidadede operação dos conversores propostos, a topologia demaior ordem, QZ-source com célula fator boost e super-lifté modelado e controlado. Por fim, para validar as análisesteóricas, dois protótipos de 200 W foram implementadosexperimentalmente.

Palavras-chave – Conversores CC-CC, QZ-source,Técnicas de Circuitos elevadores de tensão.

I. INTRODUÇÃO

Nos últimos anos, os sistemas de energia renováveis, taiscomo: energia fotovoltaica (FV), células combustíveis e etc,estão se desenvolvendo rapidamente. O nível de tensãofornecido por essas fontes de energia é geralmente baixa (<50 V). Para que esses forneçam energia a rede elétrica énecessário dois estágios de processamento de energia [1]. Oprimeiro estágio é constituído por um conversor CC-CC dealto ganho de tensão que regula a tensão do barramento paraque seja possível conectar um inversor e fornecer energia àrede elétrica [2]–[4].

Assim, o interesse nos conversores CC-CC de altoganho de tensão (high step-up) aplicados em sistemas deenergias fotovoltaicas tem aumentado nos últimos anos [5].Nesse sentido, diferentes técnicas para elevar a tensão dosconversores estão sendo explorados, tais como: indutoracoplado [6], multiplicador de tensão [7], indutores chaveados[8], capacitor chaveados [9], conversores em cascata eempilhados [10], [11], etc. Porém, ao utilizar essas técnicas,a complexidade do conversor pode aumentar e diminuir orendimento do mesmo.

O conceito de fonte Z ou fonte de impedância foi propostopela primeira vez por Peng [12]. Essa topologia pode seraplicada em conversores CC-CA, CC-CC, CA-CA e CA-CC.Entre as topologias de fonte Z modificadas, o QZ-source é umasolução simples porém eficiente [13]. Esse tipo de conversorpermite um estágio elevador de tensão (shoot-through state),o que não é permitido em inversores tradicionais [13],[14]. Conforme [2], os estudos sobre topologias QZ-sourceconcentram-se principalmente no campo de conversores CC-

CA, enquanto a aplicação conversores CC-CC ainda é umalacuna a preencher.

Nesse sentido, o presente trabalho propõe uma abordagemsimples para associar células boost e super-lift (capacitorchaveado) na entrada do conversor QZ-source. Para evidenciaros benefícios desta abordagem, essas topologias são analisadasteoricamente. Para validação dos estudos teóricos, doisprotótipos de 200 W são avaliados experimentalmente, tantoem malha aberta quanto em malha fechada.

Este artigo encontra-se dividido em três seções. Na SeçãoII, as topologias de conversores QZ-source com células booste super-lift são proposto e avaliados em relação ao ganhoe esforço de tensão nos semicondutores. Na Seção III, aanálise em regime permanente é feita de modo a modelar econtrolar as duas melhores topologias. Por fim, resultadosexperimentais são mostrados na Seção IV.

II. TOPOLOGIAS AVALIADAS

Conforme supracitado, muitas técnicas tem sido utilizadaspara melhorar o desempenho dos conversores. Nessa seção,diferentes técnicas que fazem uso de circuitos elevadoresde tensão são associadas ao conversor QZ-source, com ointuito de aumentar o ganho de tensão, sem que se perda asimplicidade de operação desses conversores.

A. Conversor QZ-source com células elevadoras de tensãoA partir das discussões feitas, o conversor QZ-source (QZS)

é apresentado na Figura 1 com uma célula elevadora de tensãogenérica na sua entrada. Como pode ser visto, os pontos"r, x, y, u e z" são destacados. A partir destas referências,circuitos elevadores de tensão podem ser associados. Assim,na Figura 2 é apresentado um conjunto de quatro célulaselevadoras de tensão. A Figura 2(a) apresenta a célula boostcomplementar (BS). Ao associar essa célula no conversor QZ-source, a parcela do ganho da célula (BS) é somada ao ganhodo conversor QZ-source, o que não acontece com a célulafator boost (BM) (2(b)). A parcela do ganho referente a(BM) é multiplicada ao ganho do conversor QZ-source. NaFigura 2(c) e (d), as células (BSLS) (BSLM) são apresentadas,respectivamente. Como pode ser visto, nessas duas célulasé adicionado o capacitor C1 é denominado super-lift, oucapacitor chaveado.

Ao associar essas células de circuitos elevadores detensão no conversor QZ-source, quatro novas topologias sãogeradas, de acordo com a Figura 3. Nas Figuras 3(a) e(b) são apresentados os conversores QZ-source com célulacomplemento boost (QZS-BS) e com célula fator boost (QZS-BM), respectivamente. Do mesmo modo, nas Figuras 3(c) e

TABELA IResumo de Principio de Operação.

QZS-BS QZS-BM QZS-BSLS QZS-BSLM

S ON OFF ON OFF ON OFF ON OFFD1 ON OFF ON OFF ON OFF ON OFFD2 — — ON OFF — — ON OFFD3 OFF ON OFF ON OFF ON OFF ONDs ON OFF ON OFF ON OFF ON OFFDo OFF ON OFF ON OFF ON OFF ON

(d) os conversores QZ-source com célula complemento booste super-lift (QZS-BSLS) é fator boost e super-lift (QZS-BSLM)são ilustrado, na devida ordem. As principais característicasdesses conversores são avaliadas a seguir.

Para análise da operação do conversor, para um períodode comutação, são feitas as seguintes considerações: osconversores operam em regime permanente; a tensão deentrada é constante; os capacitores são grandes o suficientepara manter as tensões constantes (sem ondulação); todos ossemicondutores possuem comportamento ideal, ou seja, semperdas de potência.

B. Princípio de OperaçãoAs topologias apresentadas possuem como principal

característica dois estágios de operação. No primeiroestágio, o interruptor S é acionado (ON) e os indutoressão magnetizados. No segundo estágio, o interruptor S ébloqueado (OFF) e os indutores são desmagnetizados. ATabela I resume as etapas de operação de todos os conversores.A Figura 4 mostra suas formas de onda principais.

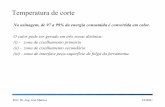

C. Ganho de TensãoConforme é apresentado em [2], o ganho estático do

conversor QZ-source (MQZS) é igual a (1). Com aassociação destas células, o ganho obtido pode ser somado oumultiplicado com o ganho do conversor QZ-source

MQZS =1

1−2D. (1)

onde D é a razão-cíclica (shoot-through state).

Para o conversor QZ-source com célula complementoboost, o ganho estático (MQZS−BS) é dado por (2). Como podeser visto, a parcela do ganho dessa célula é somada ao ganhodo conversor QZ-source.

MQZS−BS =1

1−D+MQZS. (2)

Por outro lado, o ganho estático do conversor QZ-sourcecom célula fator boost (MQZS−BM) é dado por (3). Como podeser visto a parcela do ganho dessa célula é multiplicada aoganho do conversor QZ-source.

MQZS−BS =1

1−DMQZS. (3)

ry

x u

z

C2

VoVi

L2

células SC1

D1 L3

S

Do

Co RoVoSC

D

S

Do

Co Ro

z z

Fig. 1. Conversor QZ-source (QZS).

D1

DsL1

r

y

x

u

z

(a)

C2

D2

DsL1

r

y

x

z

(b)

C1

D1

L1C1

D1

L1

r

y

x

z

Ds

(c)

C1

D1

L1

C2

D2C1

D1

L1

r

y

x

z

Ds

(d)

Fig. 2. Técnicas de circuitos elevadores de tensão: (a) complementoboost (BS). (b) fator boost (BM). (c) complemento boost e super-lift(BSLS). (d) fator boost e super-lift (BSLM)

Utilizando a mesma metodologia, o ganho dos conversoresQZ-source com células complementares boost e super-lift(MQZS−BSLS) e fator boost e super-lift (MQZS−BSLS) sãodefinidos de acordo com (4) e (5), respectivamente.

MQZS−BSLS = (1

1−D+1)+MQZS. (4)

MQZS−BSLM = (1

1−D+1)MQZS. (5)

A Figura (5) mostra o comportamento do ganho estáticodos conversores. Como pode ser visto, para a razão-cíclicamenor que 0,22 (aproximadamente), o conversor QZ-sourcecom células complemento boost e super-lift apresenta maiorganho estático. Enquanto que para D > 0,22, o conversor QZ-source com células fator boost e super-lift possui maior ganhoestático. Desta forma, fica evidente que dependendo da faixade operação, um desses conversores pode ser escolhido.

yC2

VoVi

L2

SC1

D1 L3

S

Do

Co RoVoSC

D

S

Do

Co RoD1

Ds

L1

(a)

yC2

VoVi

L2

SC1

D1 L3

S

Do

Co RoVoSC

D

S

Do

Co RoC2

D2

Ds

L1

D1

(b)

C1 C4

D1

VoVi

L1

S

L2

C3

D3 L3

Ds

S

Do

Co Ro

C1 C4

D1

VoVi

L1

SC3

D3

Ds

S

Do

Co Ro

(c)

C2

D2C1 C4

D1

VoVi

L1

S

L2

C3

D3 L3

Ds

S

Do

Co RoC2

D2C1 C4

D1

VoVi

L1

SC3

D3

Ds

S

Do

Co Ro

(d)

Fig. 3. Conversor QZ-source com: (a) complemento boost (QZS-BS).(b) fator boost (QZS-BM). (c) complemento boost e super-lift (QZS-BSLS). (d) fator boost e super-lift (QZS-BSLM)

.

vgs

t

DTS(1-D)TS

t0 t1 t2

t

t

t

iL1

iL2

iL3

Fig. 4. Principais formas de ondas teóricas.

00

1

0,05 0,1 0,15 0,2 0,25 0,3 0,4 0,45 0,50,35

2

3

4

5

6

7

8

9

10

QSZ sourceMQZSBSMQZSBMMQZSBSLSMQZSBSLM

Razão Cíclica ( )D

Gan

ho E

stát

ico

(M)

Fig. 5. Ganho Estático vs Razão-cíclica.

D. Esforço de tensão nos semicondutoresDefinidos os ganhos estáticos dos conversores, os esforços

de tensão no semicondutores são apresentados na TabelaII. Como pode ser visto, os esforços estão associados aorespectivos ganhos. Desta forma, pode-se dizer que para umamesma aplicação, os conversores com maior ganho estáticoterão menores esforços de tensão, devido a uma menor razão-cíclica.

III. MODELAGEM E CONTROLE

Após análise sucinta das topologias propostas, o conversorQZ-source com células fator boost e super-lift é escolhidopara que sejam realizados o controle e a modelagem. Esteconversor, apresenta maior ganho estático e devido a umnúmero maior de elementos passivos, na sua modelagem,surgem equações com maior ordem numérica. Entretanto, ametodologia apresentada nessa seção pode ser aplicada emoutros conversores de menor ordem. No diodo D1 e nocapacitor C4 foram consideradas a resistência serie equivalente(ESR), definida por r.

A. Modelagem• Etapa 1: 0 < t < DTs

A operação do conversor durante esta etapa é de acordo com

TABELA IIEsforços de Tensão nos Semicondutores.

QZS QZS-BS QZS-BM QZS-BSLS QZS-BSLM

D1 —1

1−D1

1−D1

1−D1

1−DD2 —

11−D

—1

1−D1

1−DD3 MQzs

11−D

+MQzs1

1−DMQzs

2−D1−D

+MQzs2−D1−D

MQzs

Ds —1

1−D1

1−D1

1−D+1

11−D

+2

Do MQzs1

1−D+MQzs

11−D

MQzs2−D1−D

+MQzs2−D1−D

MQzs

S MQzs1

1−D+MQzs

11−D

MQzs2−D1−D

+MQzs2−D1−D

MQzs

a Tabela I. As equações da operação do conversor duranteesta etapa são definidas pelas equações (6) a (13). O tempode duração desta etapa é DTs. A tensão em L1, L2 e L3 sãodefinidas, respectivamente por

L1diL1

dt= vi, (6)

L2diL2

dt= vC2 + vC4 + iL2 r, (7)

L3diL3

dt= vC3 . (8)

A corrente nos capacitores C1, C2, C3, C4 e Co é definidarespectivamente por

C1dvC1

dt=

vi − vC1

r, (9)

C2dvC2

dt=−iL2 , (10)

C3dvC3

dt=−iL3 , (11)

C4dvC4

dt=−iL2 , (12)

CodvCo

dt=−

vC0

Ro. (13)

O vetor que representa os estados é expresso porx(t) =

[iL1 iL2 iL3 vC1 vC2 v3 v4 vCo

]T , o vetorde entrada como u(t)

[vi], e o vetor de saída como

y(t)[

vo]. As equações (6) a (13) podem ser escritas na

forma de um sistema de matrizes como (14) e (15).

Kdx(t)

dt= A1x(t)+B1u(t) (14)

y(t) = H1x(t)+E1u(t) (15)

onde

K =

L1 0 0 0 0 0 0 00 L2 0 0 0 0 0 00 0 L3 0 0 0 0 00 0 0 C1 0 0 0 00 0 0 0 C2 0 0 00 0 0 0 0 C3 0 00 0 0 0 0 0 C4 00 0 0 0 0 0 0 Co

(16)

A1 =

0 0 0 0 0 0 0 00 −r 0 0 1 0 1 00 0 0 0 0 1 0 00 0 0 − 1

r 0 0 0 00 −1 0 0 0 0 0 00 0 −1 0 0 0 0 00 −1 0 0 0 0 0 00 0 0 0 0 0 0 − 1

Ro

(17)

B1 =[

1 0 0 1r 0 0 0 0

]T (18)

H1 =[

0 0 0 0 0 0 0 1]

(19)

E1 =[

0]

(20)

• Etapa 2: DTs ≤ t < Ts

A operação do conversor durante esta etapa é de acordo coma Tabela I. O tempo de duração desta etapa é (1−D)Ts. Astensões em L1, L2 e L3 são expressas, respectivamente, por:

L1diL1

dt= vi + vC1 − vC2 (21)

L2diL2

dt= vC2 − vC3 (22)

L3diL3

dt= vC3 − vCo (23)

A corrente nos capacitores C1, C2, C3, C4 e Co, é dadarespectivamente por,

C1dvC1

dt= iL1 (24)

C2dvC2

dt= iL1 − iL2 (25)

C3dvC3

dt= iL2 +

−vC4 + vCo − vC3

r− iL3 (26)

C4dv4

dt=

−vC4 + vCo − vC3

r(27)

CodvCo

dt= iL3 −

−vC4 + vCo − vC3

r−

vCo

Ro(28)

As equações (21) a (28) podem ser escritas na forma de umsistema de matrizes, como definido pelas equações (29) e (30).

Kdx(t)

dt= A2x(t)+B2u(t) (29)

y(t) = H2x(t)+E2u(t) (30)

A2 =

0 0 0 1 −1 0 0 00 0 0 0 1 −1 0 00 0 0 0 0 1 0 −1−1 0 0 0 0 0 0 01 −1 0 0 0 0 0 00 1 −1 0 0 a a −a0 0 0 0 0 a a −a0 0 1 0 0 −a −a b

(31)

onde, a =−1/r e b =−1/Ro −1/r.

B2 =[

1 0 0 0 0 0 0 0]T (32)

H2 =[

0 0 0 0 0 0 0 1]

(33)

E2 =[

0]

(34)

Equações de equilíbrio CC O vetor querepresenta os estado de equilíbrio é dado porx =

[IL1 IL2 IL3 VC1 VC2 V3 V4 VCo

]T , e ovetor de equilíbrio de saída por Y =

[vo]. O sistema de

matrizes é construído através da equação (35). O vetor deentrada é expresso por U =

[vi], sendo que IL1 , IL2 , IL3 , VC1 ,

VC2 , VC3 , VC4 e VCo , são os valores em regime permanente, ouseja, são os valores médios das variáveis iL1 , iL2 , iL3 , vC1 , vC2 ,vC3 , v4 e vCo .

X = −A−1BUY =

(−HA−1B+E

)U

(35)

ondeA = A1D+A2(1−D)B = B1D+B2(1−D)H = H1D+H2(1−D)E = E1D+E2(1−D)

(36)

TABELA IIIParâmetros dos Conversores

Parâmetros Valor

Diodos - D1,D2,D3 e D4 MBR20200CT (200 V)MOSFET IRFP4668PbF (200 V)

Capacitores - C1; C2; C3; C4; Co 18; 30; 6,6; 18; 3,3 uFIndutores - L1; L2; L3 104; 416; 220 uH

Frequência de Chaveamento - fs 50 kHzRazão-cíclica QZS-BSLM - D 0,255Razão-cíclica QZS-BSLS - D 0,290

B. Modelo CA de pequenos sinaisAs equações de estado do modelo linear CA de pequenos

sinais são definidas pela equação (37) a (38), onde up =[u d

]T , onde ˆu(t) e d (t) são perturbações de pequenossinais no vetor de entrada e na razão cíclica. Onde x(t) e y(t)são perturbações resultantes nos vetores de estado e saída.

Para obter o modelo linear, deve-se assumir que o sinaisperturbados são muito menores que seus valores em regimepermanente.

dx(t)dt

= Apx(t)+Bpup (t) (37)

y(t) = Hpx(t)+Epup (t) (38)

ondeAp = K−1ABp = K−1 [ B (A1 −A1)X+(B1 −B2)U

]Hp = HEp =

[E (H1 −H2)X+(E1 −E2)U

] (39)

As funções de transferências podem ser encontradasaplicando a Transformada de Laplace nas Equações (37) e(38), resultando na equação (40).

y(s) = Hp(sI8,8 −Ap

)−1 Bpu(s) (40)

A partir das equações da modelagem e dos parâmetrosdefinidos na Tabela III, pode se obter a função de transferência(41) que relaciona a saída pela razão cíclica.

Gvo,d =A(s)B(s)

(41)

onde A(s) = a7s7+ ...+a1s+a0, B(s) = s8+b7s7+ ...+b1s+b0, e

a0 = 4,09×1037 a1 = 3,06×1033 a2 = 2,98×1025

a3 = 1,28×1025 a4 = 3,12×1020 a5 = 9,84×1015

a6 = -2,74×1011 a7 = -4,62×105

b0 = 5,08×1034 b1 = 9,92×1030 b2 = 2,17×1027

b3 = 1,90×1023 b4 = 1,49×1019 b5 = 7,59×1014

b6 = 2,49×1010 b7 = 7,86×105

A validação do modelo é realizada comparando ocomportamento do modelo linear, com o conversor simulado,quando ambos são submetidos às mesmas condições deentrada. Aplicando na planta obtida pela modelagem, umdegrau de 5% na tensão de entrada, vi =1,87 V, que resulta emvi = 37,4+ 1,87 = 39,27, no tempo de 0,03 segundos, ondeé apresentado na Figura 6. De maneira análoga, um degrau devi =-1,87 V resultando em vi = 37,4+1,87 = 37,4 é aplicadoem 0,04 s, fazendo com que o modelo retorne ao valor inicial.

160

165

170

175

180

185

190SimulaçãoModelo

Ten

são

de

Saí

da

(v)o

0,03 0,035 0,04 0,045 0,05 Tempo (s)

Degrau +Δi iv v

Degrau -Δi iv v

Fig. 6. Validação do modelo através de degrau na tensão de entrada.

Mag

nit

ude

Fas

e(d

eg)

(dB

)

110

210 310 410 510Frequência (Hz)

-100

-50

0

50

100

-360

-180

0

180

360

28 Hz

90º

Malha abertaMalha aberta x Controlador

Fig. 7. Diagrama de Bode.

C. Projeto do controladorPara projetar o controlador discreto, deve-se obter o modelo

discreto da planta no plano z, considerando o efeito doZOH. A partir o modelo no plano z multiplica-se a plantadiscretizada por z−1, fazendo isso é inserido a dinâmica doatraso de uma amostra, que ocorre na atualização da lei decontrole, o controlador é apresentado na equação (42).

Cvo (z) =3.887×10−5z−3,45×10−5

z−1(42)

Onde a frequência de corte é 28 Hz, a margem de fase 90◦,conforme pode ser visto na Figura 7.

IV. RESULTADOS EXPERIMENTAIS

Com o intuito de validar as análises teóricas, dois protótiposde 200 W foram avaliados experimentalmente. Os conversoresmontados são: conversor QZ-source com célula complementoboost e super-lift (QZS-BSLS) e conversor QZ-source comcélula fator boost e super-lift (QZS-BSLM). Os parâmetrosdos conversores são apresentados na Tabela III. Paraimplementar os conversores, uma fonte da Agilent E4360A,carga eletrônica RBL488 e o DSP TMS320F28335.

Para validar o ganho de tensão dos conversores, na Figura8(a) são apresentadas as formas de onda da tensão aplicada nogate dos Mosfet (vgs), o painel escolhido é o CS5A-200, tensãode entrada (vi = 37,4 V), tensão de saída (vo = 175 V) bemcomo a tensão no capacitor C1 (vC1 = 37,4 V) referentes aoconversor QZS-BSLM. A Figura 8(b) apresenta formas de ondada tensão aplicada no gate do interruptor (vgs ), de tensão deentrada (vi = 37,4 V), a tensão de saída (vo = 175 V), referentesao conversor QZS-BSLS.

Na Figura 9 são apresentadas as formas de onda referentesao esforço de tensão nos interruptores vS e nos diodos vD1e vD2 dos conversores conversores QZS-BSLM e QZS-BSLS.Como pode ser visto, o esforço máximo desses componentesé igual a tensão de saída, o que está de acordo com a Tabela II.

Na Figura 10(a) são apresentadas as formas de onda datensão aplicada no gate do interruptor S (vgs), tensão nos

diodos D1, D2 e D3, (vD1), (vD2) e (vD3) respectivamente,referentes ao conversor QZS-BSLM. A Figura 10(b)apresentadas as formas de onda da tensão aplicada nogate do interruptor S (vgs), tensão nos diodos D1 e D3, (vD1) e(vD3), respectivamente, referentes ao conversor QZS-BSLS.

Em relação aos magnéticos dos conversores, as formasde onda de suas correntes estão dadas na Figura 11. NaFigura 11(a) são apresentadas as formas de onda da tensãoaplicada no gate do interruptor S (vgs), e corrente nos indutoresL1, L2 e L3, (iL1), (iL2) e (iL3), respectivamente, referentes aoconversor QZS-BSLM. A Figura 11(b) apresentadas as formasde onda da tensão aplicada no gate do interruptor S (vgs), e acorrente nos indutores L1, L2 e L3, (iL1), (iL2) e (iL3), na devidaordem, referentes ao conversor QZS-BSLS.

Para validar a modelagem e controle dos conversores QZS-BSLM e QZS-BSLS, foi gerado um distúrbio (step) na cargadesses conversores de 100 % para 50 %. O resultado desse éilustrado na Figura 12. Na Figura 12(a) são apresentadas asformas de onda da tensão de saída vo e da corrente de saída iodo conversor QZS-BSLM. Como pode ser visto, antes e depoisdo distúrbio o conversor regula a tensão de saída em 175 V,que é o valor desejado. Em relação ao conversor QZS-BSLS, asformas de onda da tensão de saída vo e da corrente de saída iosão ilustradas na Figura 12(b). Assim como o outro conversor,antes e depois do distúrbio o conversor regula a tensão desaída em 175 V. Durante o período transitório, ambos osconversores apresentam respostas dinâmicas similares, comtempo de acomodação da ordem de 10 ms e sobressinal decerca de 20 %. Por fim, a Figura 13 apresenta os resultados

vi

vgs

vC1

vO

(a)

vo

vgs

vi

(b)

Fig. 8. Resultados experimentais: vgs, vi, vo e vC1. (a) ConversorQZS-BSLM. (b) Conversor QZS-BSLS.

vS

vgs

vDS

vDO

(a)

vs

vgs

vDS

vDO

(b)

Fig. 9. Resultados experimentais: (vgs), (Vs), (vDS) e (vDO). (a)Conversor QZS-BSLM. (b) Conversor QZS-BSLS.

vD1

vgs

vD2

vD3

(a)

vD3

vgs

vD1

(b)

Fig. 10. Resultados experimentais: (vgs), (vD1); (vD2) e (vD3). (a)Conversor QZS-BSLM. (b) Conversor QZS-BSLS.

vgs

iL1

iL2

iL3

(a)

vgs

iL1

iL2

iL3

(b)

Fig. 11. Resultados experimentais: (vgs), (iL1); (iL2) e (iL2). (a)Conversor QZS-BSLM. (b) Conversor QZS-BSLS.

vo

io

(a)

vo

io

(b)

Fig. 12. Resultados experimentais em malha fechada. (a) ConversorQZS-BSLM. (b) Conversor QZS-BSLS.

20 40 60 80 100 120 140 160 180 200

Potência (W)

89

90

91

92

93

Ren

dim

ento

(%

)

QZS-BSLS

QZS-BSLM

Fig. 13. Rendimento dos conversores QZS-BSLM e QZS-BSL .

do rendimento dos conversores QZS-BSLM e QZS-BSLS. Emtoda faixa da potência de entrada (Pi), o conversor QZS-BSLMapresenta maior rendimento. De certo modo pode-se dizer essefato acontece porque o conversor QZS-BSLM possui maiorganho estático, consequentemente opera com menor razão-cíclica (D) e possui menores esforços nos componentes.

V. CONCLUSÕES

Este artigo apresentou quatro novos conversores elevadoresde tensão CC-CC, baseados no conversor QZ-source e célulasde circuitos elevadores de tensão. Ao associar as célulasno conversor QZ-source, foi realizada a análise do o ganhodesses conversores, onde dependendo da configuração podeser multiplicado ou somado ao ganho do conversor QZ-source. O conversor QZ-source com célula fator boost esuper-lift (QZS-BSLM), foi modelado e controlado, onde foidemonstrado a simplicidade e viabilidade da proposta. Paravalidar as análises teóricas, dois protótipos de 200 W foramimplementados experimentalmente. O que demonstrou que oconversor QZ-source com célula fator boost e super-lift (QZS-BSLM) apresenta melhor desempenho dentre os conversoresestudados.

AGRADECIMENTOS

O presente trabalho foi realizado com apoio daCoordenação de Aperfeiçoamento de Pessoal de NívelSuperior - Brasil (CAPES/PROEX) - Código de

Financiamento 001 e do Instituto Nacional de Ciência eTecnologia em Geração Distribuída (INCT-GD) - CNPqprocesso no. 465640/2014-1, CAPES 23038.000776/2017-54e FAPERGS 17/2551-0000517-1.

REFERÊNCIAS

[1] Q. Li and P. Wolfs, “A review of the single phase photovoltaicmodule integrated converter topologies with three different dclink configurations,” IEEE Transactions on Power Electronics,vol. 23, pp. 1320–1333, May 2008.

[2] H. Shen, B. Zhang, and D. Qiu, “Hybrid z-source boost dc-dc converters,” IEEE Transactions on Industrial Electronics,vol. 64, pp. 310–319, Jan 2017.

[3] V. T. Odaguiri, R. T. H. Júnior, and A. L. Batschauer, “Cálculodos esforços de corrente nos semicondutores do inversor fontez,” Eletrônica de Potência - SOBRAEP, vol. 21, pp. 224–233,Setembro 2016.

[4] F. L. Tofoli, D. d. C. Pereira, W. J. de Paula, andD. d. S. Oliveira Júnior, “Survey on non-isolated high-voltagestep-up dc-dc topologies based on the boost converter,” IETPower Electronics, vol. 8, no. 10, pp. 2044–2057, 2015.

[5] M. Forouzesh, Y. P. Siwakoti, S. A. Gorji, F. Blaabjerg,and B. Lehman, “Step-up dc-dc converters: A comprehensivereview of voltage-boosting techniques, topologies, andapplications,” IEEE Transactions on Power Electronics, vol. 32,pp. 9143–9178, Dec 2017.

[6] Q. Zhao, F. Tao, and F. C. Lee, “A front-end dc/dcconverter for network server applications,” in 2001 IEEE 32ndAnnual Power Electronics Specialists Conference (IEEE Cat.No.01CH37230), vol. 3, pp. 1535–1539 vol. 3, 2001.

[7] A. M. S. S. Andrade, E. Mattos, L. Schuch, H. L. Hey, andM. L. da Silva Martins, “Synthesis and comparative analysis ofvery high step-up dc-dc converters adopting coupled-inductorand voltage multiplier cells,” IEEE Transactions on PowerElectronics, vol. 33, pp. 5880–5897, July 2018.

[8] M. A. Salvador, T. P. Horn, T. B. Lazzarin, and R. F. Coelho,“Conversor cc-cc de alto ganho obtido pela combinação entreredes de indutor e de capacitor chaveados,” Eletrônica dePotência - SOBRAEP, vol. 23, pp. 161–170, abr./jun 2018.

[9] B. Axelrod, Y. Berkovich, and A. Ioinovici, “Switched-capacitor/switched-inductor structures for gettingtransformerless hybrid dc-dc pwm converters,” IEEETransactions on Circuits and Systems I: Regular Papers,vol. 55, pp. 687–696, March 2008.

[10] A. M. S. S. Andrade and M. L. d. S. Martins, “Quadratic-boostwith stacked zeta converter for high voltage gain applications,”IEEE Journal of Emerging and Selected Topics in PowerElectronics, vol. 5, pp. 1787–1796, Dec 2017.

[11] A. M. S. S. Andrade, H. L. Hey, L. Schuch, and M. L.da Silva Martins, “Comparative evaluation of single switchhigh-voltage step-up topologies based on boost and zeta pwmcells,” IEEE Transactions on Industrial Electronics, vol. 65,pp. 2322–2334, March 2018.

[12] F. Z. Peng, “Z-source inverter,” IEEE Transactions on IndustryApplications, vol. 39, pp. 504–510, Mar 2003.

[13] J. Anderson and F. Z. Peng, “Four quasi-z-source inverters,”in 2008 IEEE Power Electronics Specialists Conference,pp. 2743–2749, June 2008.

[14] N. Vázquez, E. Baeza, A. Perea, C. Hernández, E. Vázquez,and H. López, “Z and qz source inverters as electronic ballast,”IEEE Transactions on Power Electronics, vol. 31, pp. 7651–7660, Nov 2016.