Apostila_2013

Transcript of Apostila_2013

“Oficina de Microfabricação: Projeto e Construção de CI´s MOS”

CCS e FEECUNICAMP

Janeiro de 2013

Coordenador: Prof. José Alexandre Diniz

Aluno:

1

Sumário

1. Evolução de Microeletrônica a Microssistemas2. Conceitos Básicos para Semicondutores3. Semicondutores4. Junções em Semicondutores5. Capacitor MOS6. Transistor MOSFET7. Escalamento e Limites dos Dispositivos MOS8. Integração de Processos: CMOS em Si9. Estruturas de Dispositivos Semicondutores10. Plasma Etching11. Deposição de Filmes Finos12. Conceitos de Vácuo.13. Projeto de Processos e Dispositivos14. Microssistemas: Fabricação e Aplicações15. Introdução à Tecnologia LIGA16. Projeto de CI´s MOS.17. Horários das atividades/aulas18. Descrição do Processo MOS do CCS para a fabricação dos Chips 19. Fluxo dos processos para a obtenção dos Chips Fabricados20. Relatório de processos para a obtenção dos Chips Fabricados21. Relatório de medidas dos Chips Didáticos (Univ. Edinburg) 22. Relatório de medidas dos Chips Fabricados23. Corrosão Anisotrópica do Silício.24. Enquête de Opinião.

Nota: Os capítulos 1 a 16 encontram-se gravados em CD e apenas os capítulos 17 a 24 encontram-se impressos neste caderno.

2

PREFÁCIO

O curso “Oficina de Microfabricação: Projeto e Construção de CI’s MOS” foi oferecido pela primeira vez em janeiro de 1999, como uma disciplina do Curso de Extensão da UNICAMP, por um esforço conjunto do Centro de Componentes Semicondutores, CCS, e da Faculdade de Engenharia Elétrica e de Computação. Desde então, o curso vem sendo repetido periodicamente em nível de disciplina de extensão (FEE107), bem como, em nível de disciplina de graduação (EE941) e de pós-graduação (IE326). Trata-se de disciplina com 2/3 de atividades práticas em laboratório e 1/3 de atividades em sala de aula. Ao todo, o curso é oferecido três vezes ao ano, atendendo assim até 45 alunos ao ano.

Gostaríamos de expor em primeiro lugar os motivos que nos levaram a realizar este trabalho, e/ou os resultados que dele esperamos.

A eletrônica tornou-se a área econômica mundial mais volumosa, com um mercado global acima de US$ 1 trilhão. Boa parte deste mercado é de componentes semicondutores, com um mercado da ordem de US$ 200 bilhões (no ano 2000). A área tem crescido a taxas anuais médias de 16% ao longo das últimas 4 décadas, fenômeno este inigualável em qualquer outra área. Toda esta evolução e crescimento econômico são baseados na tecnologia de fabricação de circuitos integrados, ou seja, dos chips. Um relatório da associação americana de indústrias de semicondutores, SIA, apresenta os seguintes dados marcantes em seu relatório de 1997:

O valor agregado de produtos semicondutores é de 59%, versus 21% para a indústria automobilística.

Indústria de semicondutores emprega 1,5 milhões de pessoas no USA, com soma de salários de US$ 50 bilhões e pagamento de impostos de US$ 18 bilhões.

A taxa de crescimento de emprego na indústria de semicondutores cresceu em média 4,3 % no período entre 1992 a 1996, versus 0,5 % na média das outras indústrias de manufatura.

Atualmente temos chips incorporados em um enorme número de produtos, incluindo todos os sistemas eletrônicos de telecomunicações e de informática, satélites, impressoras, controle de processos industriais, robótica, automóveis, aviões e outros meios de transporte, utensílios domésticos, entretenimento, educação, agricultura, medicina, etc. Produtos com inovação e competitivos devem incorporar uma certa “inteligência”, ou seja, circuitos integrados. Desta forma, um país moderno e competitivo no século 21, não pode prescindir de fabricar bens de eletrônica e de microeletrônica em particular.

A tecnologia de fabricação de circuitos integrados é baseada em técnicas de microfabricação, que foram desenvolvidas para este fim. Atualmente estas mesmas técnicas vêm sendo usadas para um número grande de outras aplicações, tais como dispositivos e circuitos tipo:

a) optoeletrônicos, b) fotônicos, c) microssensores, d) microatuadores, e) micromecânicos, f) estruturas para biologia e medicina, g) montagem de placas de circuitos impressos modernos.

Vários destes tipos de dispositivos e circuitos, constituem os microssistemas ou MEMS/MOEMS (Micro-Opto-Electro-Mechanical-Systems) e são responsáveis pela

3

nova revolução emergente, chamada de revolução da automatização total (produção automatizada, casas inteligentes, carros inteligentes, etc....).

Dada a importância econômica dos circuitos integrados e as novas aplicações para as mesmas técnicas de microfabricação, é fundamental o ensino das mesmas em grande escala. Quanto mais pessoas conhecerem o tema, resultarão os seguintes benefícios:a) Aumento da probabilidade de iniciativas industriais de produtos especiais ou

novos produtos em nichos de mercados. Estes nichos podem ser ocupados por empresas menores, inclusive de origem local.

b) Complemento ao nível de projetistas de circuitos integrados, o que é fundamental para o desenvolvimento de novos produtos, com maior valor agregado. O conhecimento profundo dos processos construtivos de CI’s não é uma condição necessária para um projetista, porém ajuda. O entendimento do processo de fabricação, das origens das regras de projeto, da física e dos modelos dos dispositivos, permitirá o projetista “criar” mais.

c) Constitui uma das condições e incentivos para a vinda de empresas multinacionais de produção de chips em larga escala.

d) Permite ocupar oportunidades não atendidas pelos países do primeiro mundo, por falta de mão de obra em nível de engenharia eletrônica e de computação. Segundo estimativa da SEMI, existe uma demanda mundial anual de 200 mil novos engenheiros em microeletrônica, enquanto que as universidades formam da ordem de 100 mil engenheiros anualmente. Contatos pessoais na Europa e USA confirmam a grande falta de engenheiros e pesquisadores para atender a demanda de desenvolvimento nestes países.

Todo desenvolvimento de tecnologia de ponta só é possível com a disponibilidade de recursos humanos de qualidade e em grande quantidade. Muitos países, conscientes deste fato, têm organizado programas de ensino para suprir esta demanda para áreas específicas e prioritárias. Só para mencionar um país, citamos o programa da França. A França possui um programa de ensino de microeletrônica, financiado pelos ministérios de educação e de indústria, com a participação aberta a todas as universidades do país. Por meio deste programa, as instalações dos laboratórios mais avançados, disponíveis em algumas poucas universidades ficam disponibilizadas para serem usadas no oferecimento de disciplinas de microeletrônica para alunos das outras universidades. Este programa treina mais de 1000 alunos anualmente, durante a década de 90.

Baseado na importância do ensino de microeletrônica, no modelo acima da França e no fato que poucas universidades no país possuem instalações completas para oferecimento de disciplinas práticas de microfabricação, o CCS, junto com a FEEC da UNICAMP vem oferecendo o curso “Oficina de Microfabricação: Projeto e Construção de CI´s MOS”, em nível de extensão (aberto a alunos de outras universidades), bem como em nível de graduação e pós-graduação (aberto a alunos da UNICAMP).

A Quem se Destina: Alunos de graduação de 3o a 5o ano de cursos de engenharia, física, química e

tecnologia. Alunos de pós-graduação de cursos de engenharia, física, química e biologia Professores universitários, de ensino técnico e até de 2o grau.

4

Carga Horária: FEE107- de extensão: duas semanas em período integral, com total de 80h aula,

oferecido nos períodos de férias escolares de janeiro, ou de acordo com solicitações.

EE941 – de graduação, 75 h, com 5 h semanais ao longo do 2o semestre do ano letivo.

IE316 – de pós-graduação, 60 h, com 4 h semanais ao longo do 1o semestre do ano letivo.

Ementa Resumida:Revisão de teoria de semicondutores e de dispositivos MOS; descrição dos

processos de fabricação, projeto de dispositivos e blocos básicos de CI´s MOS, fabricação de um chip teste contendo dispositivos isolados e um circuito básico, medidas de caracterização de materiais, processos, dispositivos e do circuito fabricado. Adaptações à ementa do curso podem ser feitas para grupos específicos de alunos, dependendo da sua formação e interesse. Durante as aulas de laboratório de microfabricação, os alunos participam efetivamente da fabricação de lâminas de Si contendo um chip com estruturas, dispositivos e blocos de circuitos de teste. As aulas são divididas da seguinte forma nas seguintes atividades, como pode ser observado no calendário de horários:

Atividade Tempo totalSeminários 27 h

Laboratório de microfabricação 24 hLaboratório de medidas de dispositivos 17 h

Laboratório de simulações e CAD 6 hVisitas a laboratórios: (LPD/IFGW e

Itaucom)6 h

Número de alunos por turma e freqüência dos cursos: Máximo 15 alunos por turma (limitação dos equipamentos de laboratório) Freqüência de cursos: 3 vezes ao ano.

Agradecimentos:Agradecemos em primeiro lugar a todos os colegas, pesquisadores e

funcionários do CCS, FEEC e LPD/IFGW, que tornaram o oferecimento do curso possível. Agradecemos aos palestrantes convidados. Somos gratos a todos que contribuíram para a realização do curso, em especial, aos alunos participantes, pelo interesse e entusiasmo. São estes que nos motivam e nos fazem acreditar nas perspectivas de uso deste conhecimento, em benefício da sociedade, que nos financia. Somos gratos à FINEP, CAPES/PADCT, INCT-Namitec/CNPq e FAPESP, pelos auxílios financeiros recebidos.

Profs. Jacobus W. Swart e José Alexandre DinizCampinas, 28 de janeiro de 2013.

5

Oficina de Microfabricação: Projeto e Construção de CI´s MOSPlanejamento – Janeiro/Fevereiro 2013- CCS/UNICAMP

1a Semana – 2ª feira, 28/01/13.Hora Local Atividade Instrutores8:30 Sem. Apresentação Jacobus, Diniz.9:00 Sem. Revisão de Semicondutores Jacobus10:00 Café10:15 Lab. Oxidação de campo Diniz, Godoy10:30 Sem. Integr. de Proc. MOS-CCS + Teoria Cap. MOS Jacobus 12:00 Almoço13:30 Sem. Limpeza de Lâminas Diniz, Regina14:30 Lab. a) Visita ao Lab.

b) Medidas lâmina: espessura, tipo, resistividadeDoi, Diniz, MaraGodoy, Beny.

16:30 Sem. Modelo de oxidação e Fotogravação Diniz.

1a Semana – 3ª feiraHora Local Atividade Instrutores8:30 Sem. Integração processos: nMOS Si-poly e CMOS. Jacobus10:00 Café10:15 Lab. a) Fotogravação, fonte e dreno + etch.

b) Medida espessura de óxidoc) Medidas de chip didático

Godoy, Diniz, ReginaJair.Diniz, Beny, Leandro

Nota: as 3 atividades de lab. são realizadas em rodízio, até final do dia.

1a Semana - 4ª feira Hora Local Atividade Instrutores8:30 Sem. Difusão e implantação de íons Jacobus.10:00 Café10:15 Lab. Implantação de íons de S/D Lino, Valter11:00 Sem. Etching úmido e seco Stanislav12:00 Almoço13:00 Sem. Caracterização camadas dopadas + Simul.

Atlas e AthenaJacobus, Leandro, Jair

14:00 Lab.PC´s

a) Medidas chip didáticob) Medida SEM/FIBc) Simulação de processos

Diniz, Beny, LeandroAlfredo, MarcosJair

Nota1 : as 2 atividades de lab. ás 14h são realizadas em rodízio, até final do dia.

1a Semana - 5a feiraHora Local Atividade Instrutores8:30 Sem. Processos CVD Doi9:30 Café9:45 Lab Recozimento e oxidação Diniz, Godoy11:00 PC’s Relatórios12:00 Almoço13:00 Lab.

PC´sa) Medidas chip didáticob) Simulações Atlas e Athena

Diniz, Leandro.Jair

15:00 PC’s RelatóriosNota: as atividades de lab. às 9:45 e às 13h são realizadas em rodízio.1a Semana - 6a feiraHora Local Atividade Instrutores8:30 Sem. Evolução da Microeletrônica Jacobus10:15 Lab Café10:30 Sem. Regras de Escalamento e Limites. Jacobus11:30 Sem. Layout do chip CCS2 – Programa Magic Emilio12:00 Almoço13:00 Lab. a) Fotogravação porta + etching

b) Demonstração plasma, sputteringc) Medidas: tox., xJ, Rs

Godoy, Jair, Regina, DinizStanislav, DoiBeny, Mara, Diniz.

Nota: as atividades às 13:00 h são realizadas em rodízio, até final do dia.

6

2a Semana - 2ª feira, 04/02/13Hora Local Atividade Instrutores8:30 Sem. Cargas no sistema SiO2/Si Diniz10:00 Café10:15 Lab. Oxidação de porta Diniz, Godoy, Regina11:00 Sem. Conceitos de vácuo e metalização Doi12:00 Almoço13:00 Lab. Medidas: tox., Rs, xJ

Fotogravação de contatos + etchingMedidas chip didático

Beny, JairGodoy, ReginaDiniz, Leandro

Nota: as 3 atividades de lab. às 13h são realizadas em rodízio, até final do dia.

2a Semana - 3ª feiraHora Local Atividade Instrutores8:30 Sem. Modelos MOSFET. Jacobus.10:00 Café10:10 Lab. Carregar lâminas na evaporadora Doi, Diniz, Godoy10:30 Sem. Encapsulamentos de CI Pacheco e/ou M. Biasoli12:00 Almoço13:00 Lab. Evaporação de Al Doi, Diniz, Godoy14:00 Lab. a) Fotogravação de interconexões

b) Etching de Si para Microestruturas MEMSc) Metrologia MEMS (óptico e SEM/FIB)

Godoy, Jair, Regina DinizMárcia, Alfredo

Nota: as 3 atividades de lab. às 14h são realizadas em rodízio, até final do dia.

2a Semana - 4ª feiraHora Local Atividade Instrutores8:30 Sem Dispositivos optoeletrônicos Newton.10:00 LPD Visita e demonstrações Newton, Beny.12:00 Almoço13:00 Lab. Evaporação de Al / costas das lâminas

Recozimento de sinterizaçãoDoi, Diniz, Godoy.

14:00 Lab.PC´s

a) Medidas dos dispositivos fabricadosb) Relatório

Diniz, Beny, Jair, Leandro

Nota: as 2 atividades de lab. às 14h são realizadas em rodízio, até final do dia.

2a Semana – 5ª feiraHora Local Atividade Instrutores8:30 Lab

PC’sMedidas dos dispositivos fabricadosRelatórios

Diniz, Beny, Jair, Leandro

12:00 Almoço13:00 Lab.

PC’sMedidas dos dispositivos fabricadosRelatório

Diniz, Beny, Jair, Leandro

2a Semana – 6a feiraHora Local Atividade Instrutores8:30 CTI Visita e demonstrações Jacobus12:30 Almoço14:00 Sem. Introdução a MEMS e Micro-usinagem. Jacobus15:30 Avaliação Final e entrega de Relatório Jacobus/Diniz

7

Descrição do Processo MOS do CCS/UNICAMP José Alexandre Diniz

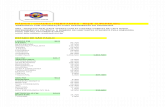

O processo MOS consiste basicamente das etapas que estão apresentadas na Figura 1. Nos itens posteriores deste capítulo, as etapas são descritas e explicadas detalhadamente.

6 . R e m o ç ã o d o f o t o r r e s i s t e

7 . I m p l a n t a ç ã o I ô n i c a

a ) 1 1 B + , E = 5 0 k e V , 5 x 1 0 1 5 c m - 2

b ) 3 1 P + , E = 5 0 k e V , 5 x 1 0 1 5 c m - 2 , n a s c o s t a s d a l â m i n a .

8 . R e c o z i m e n t o e o x i d a ç ã o ú m i d a

9 . F o t o g r a v a ç ã o d e c a n a l e c o n t a t o s , e t c h d o ó x i d o e r e m o ç ã o d of o t o r r e s i s t e , f i n a l i z a n d o c o m a l i m p e z a R C A

1 1 . F o t o g r a v a ç ã o d e c o n t a t o s , e t c h d o ó x i d o e r e m o ç ã o d o f o t o r r e s i s t e ,f i n a l i z a n d o c o m a l i m p e z a R C A

1 2 . E v a p o r a ç ã o d e a l u m í n i o

1 3 . F o t o g r a v a ç ã o d e i n t e r c o n e x õ e s e e t c h d o a l u m í n i o , r e m o ç ã o d of o t o r r e s i s t e e s i n t e r i z a ç ã o d e c o n t a t o s

1 . L â m i n a s d e s i l í c i o d o t i p o n , ( 1 0 0 ) , c o m r e s i s t i v i d a d e e n t r e 4 e 6 o h m. c m . L â m i n a s p a r a d i s p o s i t i v o s m a i s u m a l â m i n a t e s t e .

M e d i d a s d e r e s i s t i v i d a d e ( 4 p o n t a s ) e e s p e s s u r a .

2 . L i m p e z a p a d r ã o R C A c o m p l e t a .

3 . O x i d a ç ã o ú m i d a , S i O 2 , X o x = 0 , 7 m i c r o n .

4 . A p l i c a ç ã o d o f o t o r r e s i s t e e e x p o s i ç ã o à l u z u l t r a v i o l e t a

5 . E t c h d o ó x i d o e m s o l u ç ã o d e H F / N H 4 F

Figura 1- Processo pMOS do CCS/UNICAMP para fabricação do chip teste

1. O Substrato de Silício

O tipo de dopante, a orientação cristalina e a resistividade do substrato de Si, que será utilizado, são características importantes na fabricação e no desempenho dos dispositivos.

O tipo de dopante, p ou n, determina os portadores majoritários, lacunas ou elétrons, respectivamente, presentes no substrato e qual processo MOS, pMOS ou nMOS, que será empregado. Em lâminas tipo n, executa-se o processo pMOS, enquanto em tipo p, o nMOS, pois o canal de modo enriquecimento ou depleção do transistor MOS é formado por portadores minoritários presentes no substrato. Dispositivos nMOS apresentam mobilidade maior que os pMOS, pois a mobilidade de elétrons é cerca de três vezes maior que a de lacunas. O tipo de dopante pode ser determinado por um sistema de ponta-quente ou pela visualização do formato do substrato, como indicado na Figura 2.

8

N<111>

P<100>P<111>

N<100>

90o

180o

Figura 2 - Tipos de dopantes e as orientações Cristalográficas de Substratos de Si, vistos de cima.

A Figura 2 mostra que a orientação cristalográfica e o tipo de semicondutor podem ser obtidos por inspeção visual do formato da lâmina. Normalmente, para o Si utilizam-se duas possibilidade de crescimento ou orientação direcional <111> ou <100>. O tipo n ou p de semicondutor pode ser identificado pela presença e pelo posicionamento dos chanfros laterais. A orientação cristalográfica pode influir principalmente na taxa de oxidação do substrato e na densidade de defeitos no óxido de Si crescido sobre a lâmina, que originam centros de armadilhamento de cargas no isolante. Estas cargas podem responder de forma indesejável ao campo elétrico aplicado ao dispositvo, reduzindo seu desempenho. Óxidos crescidos sobre lâminas com orientação <100> apresentam menos defeitos que os crescidos sobre substratos com orientação <111>. Para fabricação do Chip teste do CCS são utilizadas lâminas tipo n, para executar o processo pMOS, e com orientação <100>, o que resulta em menos defeitos nos óxidos crescidos.

A resistividade indica qual a concentração de dopantes (portadores majoritários) do substrato de Si. É calculada pelas expressões (1) e (2), onde V/I é medido em um equipamento de quatro pontas, Rs é a resistência de folha e t é a espessura do substrato. Quanto maior a resistividade menor é a concentração de dopantes na lâmina. Normalmente, utilizam-se substratos com concentrações da ordem de 1014 a 1016 cm-3, resultando em correspondentes resistividades de 1 a 22 .cm. Para fabricação do Chip teste do CCS, utilizam-se lâminas com valores de resistividade entre 4 e 6 .cm, com concentração de portadores da ordem de 1015 cm-3.

(Resistência de folha) (1)

(Resistividade) (2)

2. Limpeza padrão RCA

A limpeza das lâminas de silício, representadas em corte lateral na Figura 3, é fundamental num processo de microfabricação. Para garantir uma limpeza eficaz, com a menor quantidade possível de impurezas, segue-se um processo padrão RCA que consiste na seguinte seqüência de etapas, mergulhando-se as lâminas em soluções de:

• H2SO4/H2O2 (4:1) em 80°C por 10 min: esta solução denominada "piranha", utiliza-se para remover principalmente quantidades de gordura presentes na superfície das lâminas de silício;

• HF/H2O (1:10) em temperatura ambiente por 10s: nesta etapa de limpeza remove-se o óxido de Si (SiO2) nativo na superfície do silício. A reação química do processo é a seguinte:

SiO2 + 4HF SiF4 + H2O.;• NH4OH/H2O2/H2O (1:1:5) em 80°C por 10 min: nesta etapa, removem-se a gordura e os

metais do grupo IB e IIIB (Cu, Ag, Zn, Cd); • HCl/H2O2/H2O (1:1:5) em 80°C por 10 min: nesta etapa dissolvem-se os íons alcalinos e

hidróxidos de Fe+3, Al+3 e Mg+3 das superfícies dos substratos.

9

Entre uma solução e outra, as lâminas são submetidas a um enxágüe com água DI (deionizada) 18 M.cm por 3min. A secagem destas lâminas é feita com jato de nitrogênio. No item 2.3 é apresentado o procedimento inteiro de limpeza RCA.

Figura 3- Representação da lâmina de Si em corte lateral

2.1 – Material Utilizado. O material normalmente utilizado na limpeza de lâminas é listado abaixo:

• 3 béquers de vidro pyrex • 1 béquer de polipropileno• 1 "hot plate"• 1 barqueta de quartzo• 1 pinça de aço inoxidável• 1 pinça de polipropileno• 1 litro de Ácido Sulfúrico (H2SO4)• 1 litro de Ácido Fluorídrico (HF)• 1 litro de Hidróxido de Amônia (NH4OH)• 1 litro de Ácido Clorídrico (HCl)• 1 litro de Peróxido de Hidrogênio (H2O2)Toda água utilizada é deionizada de 18 M.cm e todos os produtos químicos utilizados são

de grau eletrônico.

2.2. Limpeza dos béquers, barquetas e pinças.Antes do início da limpeza das lâminas, verifica-se se os recipientes e materiais que serão

manipulados estão limpos. Caso contrário, ocorre duas etapas de limpeza destes materiais: a de pré-lavagem e a de retirada de gordura. A etapa de pré-lavagem é a seguinte: os béquers, as barquetas e as pinças são lavados com detergente apropriado. Outra possibilidade é que aos invés da lavagem com detergente, os béquers e as barquetas, que formam basicamente a parte de vidraria, podem ser mergulhados em uma solução de água régia (HCl/HNO3 (3:1)) com posterior enxágüe em água DI (deionizada). Em seguida, executa-se a etapa de retirada da gordura dos materiais com o seguinte procedimento:

Fazer uma solução de H2O + H2O2 + NH4OH na proporção de 7:2:1;Enxaguar o béquer com água;Verificar visualmente se o béquer está realmente limpo (as gotas de água devem escorrer

das paredes do vidro).

2.3. Procedimento para limpeza das lâminas de SilícioEm béquers separados prepare as soluções de:

(I) H2SO4 + H2O2 na proporção de 4:1 (solução “piranha”);(II) HF + H2O na proporção de 1:10 (solução para remoção do óxido nativo);(III) NH4OH + H2O2 + H2O na proporção de 1:1:5 (solução para remoção de gordura e metais

do grupo IB e IIIB (Cu, Ag, Zn, Cd));(IV) HCl + H2O2 + H2O na proporção de 1:1:5 (solução para remoção de íons alcalinos e

hidróxidos de Fe+3, Al+3 e Mg+3);Com estas soluções deve-se obedecer o seguinte procedimento:

• Aqueça as soluções à 80° C no "hot plate";• Mergulhe a lâmina por 10 minutos na solução (I);• Enxágüe em água corrente por 3 minutos e deixe mais 3 minutos dentro do béquer com

água;• Mergulhe a lâmina por 30 segundos na solução (II); • Enxágüe em água corrente por 3 minutos e depois deixe as lâminas por mais 3 minutos

dentro do béquer com água;• Mergulhe a lâmina por 10 minutos na solução (III);• Enxágüe novamente em água corrente por 3 minutos e depois deixe as lâminas por mais 3

minutos dentro do béquer com água;• Mergulhe a lâmina por 10 minutos na solução (IV);• Enxágüe novamente em água corrente por 3 minutos e depois deixe as lâminas por mais 3

minutos dentro do béquer com água;

10

• Seque as lâminas com Nitrogênio (N2);• Coloque as lâminas na caixa para transportá-las;• Não exponha as lâminas limpas ao ambiente do laboratório.

IMPORTANTE: Neutralizar todas soluções antes de descartar na pia. Utilizar avental e luvas durante qualquer manipulação de produtos químicos e de lâminas.

3.Oxidação Úmida de Campo para Isolação de Dispositivos

Substrat de Si tipo-n

Figura 4- Representação da lâmina de Si em corte lateral com óxido de campo crescido.

A oxidação úmida é realizada colocando-se as lâminas de Si no forno térmico convencional em alta temperatura de 1000 °C e em ambiente de H2O (vapor) e de O2. Esta etapa é executada para formação do óxido de Si de campo, que isola um dispositivo do outro na lâmina. A Figura 4 representa o óxido de Si crescido sobre o substrato de Si. Para isso, a espessura do óxido de campo deve ser maior que 0.5m. Para controle do processo, clive uma lâmina teste em 4 partes denominadas T1, T2, T3 e T4. Coloque-as junto com as lâminas inteiras onde serão confeccionados os dispositivos. Com estas amostras teste pode-se fazer as medidas de espessura do óxido.

O procedimento de oxidação úmida no CCS/UNICAMP é o seguinte:• Utilize o Forno de Penetração de Fósforo em temperatura de 1000 °C;• Execute a entrada da barqueta de quartzo com as lâminas no forno em ambiente de N2, com

fluxo de 1l/min, por um tempo maior que 3 min;• Deixe as lâminas neste ambiente de N2 por 10 min;• Desligue a linha de N2 , ligue a linha de O2 , com fluxo de 1l/min, e deixe as lâminas neste

ambiente por 10 min (oxidação seca);• Ligue o sistema de borbulhador O2/H2O, com aproximadamente 63 gotas de H2O/min, para

manter as lâminas em ambiente úmido por 180 min (oxidação úmida);• Desligue o sistema de borbulhador O2/H2O, ligue a linha de N2 , com fluxo de 1l/min, e deixe

as lâminas neste ambiente por 10 min (recozimento do óxido crescido);• Execute a saída da barqueta de quartzo com as lâminas do forno em ambiente de N2, com

fluxo de 1l/min, por um tempo maior que 3 min;Observações: A espessura esperada do óxido é da ordem de 0.8 µm.

4. Processo Fotolitográfico do Primeiro Nível de Máscara para Obtenção de Fonte/Dreno

A fotolitografia é a etapa de processo exigida para gravar padrões de uma máscara para o substrato onde é fabricado o chip. A Figura 5 mostra basicamente o processo fotolitográfico. Utilizando-se de um sistema de “spinner” em alta velocidade de rotação, maior que 3000 rpm, por centrifugação espalha-se sobre a camada do óxido uma resina foto-resistiva, que é um líquido orgânico polimérico, denominado fotorresiste. Este resiste é colocado em uma estufa em temperatura de aproximadamente 100ºC para secar. A Figura 5(a) mostra a representação do fotorresiste espalhado sobre o óxido de campo. Esta resina polimerizada não é solúvel em certos solventes, denominados reveladores. Executa-se a despolimerização por luz ultravioleta que passa através das aberturas da máscara que contém o padrão a ser transferido ao substrato, como representado na Figura 5(b). A parte opaca da máscara evita a exposição à luz ultravioleta das regiões do substrato que serão posteriormente processadas. Para remover a parte do resiste despolimerizada, utiliza-se o solvente revelador.

11

(a)

Óxido de Si

Substrato

(b)

Resiste

Óxido de Si

Substrato

Figura 5- Representação da lâmina de Si em corte lateral com óxido de campo crescido. Representa-se em (a) o fotorresiste espalhado sobre o óxido e em (b) a despolimerização do

resiste pela exposição à luz ultravioleta para transferência de padrão da máscara para o óxido.

Para o início da fotolitografia, estando a lâmina limpa e a umidade do ambiente abaixo de 50%, espalha-se sobre a amostra o promotor de aderência do resiste, denominado HMDS, em um spinner em alta velocidade de rotação de 7000 rpm por 40 segundos. Em seguida, uma camada de fotorresiste é aplicada sobre a lâmina com o HMDS espalhado. Para isso, deposita-se algumas gotas de fotorresiste (AZ 1350J) sobre a lâmina, espalha-se o fotorresiste através do spinner em alta velocidade de rotação de 7000 rpm por 40 segundos, coloca-se a lâmina na estufa para secagem e aderência do fotorresiste. Após a aderência do resiste, coloca-se a lâmina e a máscara em uma fotoalinhadora com fonte de luz ultravioleta. Na fotoalinhadora, alinha-se a máscara e a lâmina através do sistema óptico, e aciona-se a exposição aos raios ultra-violeta (UV) do substrato com resiste, em uma potência de 9mW.cm-2 durante 20 segundos, despolimerizando as regiões expostas. A revelação do resiste é executada através da imersão das lâminas em solução MF-312/H2O (1:1) por 60s. Para finalizar, coloca-se as lâminas na estufa em 90ºC por 30 min para endurecimento do resiste não revelado.

5. Remoção do Óxido para Obtenção da Fonte/Dreno

Resiste

Óxido de Si

Substrato

Figura 6- Representação da lâmina de Si em corte lateral com óxido de campo removido nas áreas sem proteção do resiste.

Como representado na Figura 6, a etapa de fotolitografia é utilizada para remover seletivamente o óxido de algumas regiões, que serão processadas posteriormente para a obtenção da fonte/dreno do transistor MOS. Executa-se a remoção do óxido mergulhando-se as lâminas em uma solução tampão ("Buffer") de HF e NH4F. Para controle da remoção do óxido coloca-se junto nesta solução as amostras teste T3 e T4 com óxido crescido sobre os substratos. Esta solução corrói o óxido de silício a uma taxa de 100nm/min e não reage nem com o resiste e nem com o substrato de Si. Verifica-se que o óxido está totalmente removido quando estas áreas nas lâminas sem resiste de proteção ou as amostras teste T3 e T4 apresentar-se totalmente secas quando retiradas da solução “Buffer”. Após a retirada do óxido, retira-se a

12

camada protetora de fotorresiste com acetona. A Figura 7 mostra a lâmina sem a camada protetora de fotorresiste sobre o óxido e as áreas expostas do substrato.

Óxido de Si

Substrato

Figura 7- Representação da lâmina de Si em corte lateral sem a camada protetora de fotorresiste sobre o óxido e as áreas expostas do substrato.

6. Implantação de Íons de Boro e de Fósforo para Obtenção da Fonte/Dreno e de Contato Ôhmico Metal-Semicondutor na Base do

Substrato, Respectivamente.

(a)

Óxido de Si

Substrato

(b)

Óxido de Si

Substrato

Figura 8- Representação da lâmina de Si em corte lateral com óxido de campo crescido protegendo as áreas do substrato que não devem ser implantadas. Representa-se em (a) a

implantação de Boro para formação de fonte/dreno do transistor MOS e em (b) a implantação de Fósforo para obtenção de contato ôhmico metal-semicondutor na base do substrato.

Utiliza-se a implantação de íons para dopagem do tipo n, com Fósforo, ou p, com Boro, em substratos de Si. A Figura 8 mostra em (a) a implantação de Boro para formação de fonte/dreno do tipo p+ do transistor MOS e em (b) a implantação de Fósforo para obtenção de contato ôhmico metal-substrato tipo n+ na base do substrato. O óxido de Si serve como camada protetora contra a implantação de íons (Figura 8) no substrato.

O processo de implantação iônica permite controlar os seguintes parâmetros:i) a energia fornecida (pelo campo elétrico) ao íons, que determina a profundidade média de

penetração em uma determinada estrutura atômica; ii) a carga total implantada (dose), que é fornecida pela corrente do feixe; iii) a espécie química implantada, que é selecionada por um espectrômetro de massa; iv) a contaminação mínima do substrato, que é estabelecida pelo alto vácuo (10-8 Torr) exigido

nas câmaras de implantação e pela execução do processamento em temperatura ambiente (processo frio);

v) a uniformidade lateral e a definição espacial da região implantada, que são monitoradas pelo sistema automático de varredura do feixe iônico sobre o alvo (sistema x-y com lentes eletrostáticas).

Desta maneira, o processo forma camadas implantadas com controle preciso da uniformidade, da definição espacial, da contaminação e do perfil de distribuição dos íons que depende da dose implantada e da energia do feixe iônico. Uma vez que a seleção do íon é feita por um espectrômetro de massa, não é necessária a utilização de fontes de materiais de alta pureza, para a geração de íons. No processo pMOS do CCS, para implantação de íons de Boro e de Fósforo

13

emprega-se as fontes de Nitreto de Boro (BN) e de Fluoreto de Fósforo (PF5), respectivamente. A implantação iônica é realizada em um implantador GA-4204 EATON. São implantados íons de Boro, para formação de regiões p+ nas áreas de fonte e dreno, e de Fósforo nas costas da lâmina, para obtenção de contato ôhmico metal-substrato tipo n+ na base do substrato. Para controle as amostras T3 e T4 também são implantadas. Os parâmetros de implantação são:

• íons 11B+, com energia de 50 keV e com dose de 5 x 1015 cm-2 para as regiões p+ ;• íons 31P+ com energia de 50 keV e com dose de 5 x 1015 cm-2, para as regiões n+ nas costas

da lâmina. A lâmina é colocada no porta-substrato do implantador em ângulo de 7º com o feixe e girada

sobre seu próprio eixo de 20º, para evitar a canalização de íons dentro do substrato semicondutor.

7. Recozimento para Ativação de Dopantes Implantados com Posterior Oxidação Úmida para Formação de Óxido na Região de

Fonte/Dreno

O recozimento pós-implantação para reconstrução das camadas implantadas e ativação dos dopantes nas regiões n+ e p+ (Figura 9). Realiza-se o recozimento em forno convencional, em ambiente de N2, com temperatura de 10000C e tempo de 20 min. A oxidação úmida posterior é realizada para a formação de óxido na região p+ de Fonte/Dreno. Realiza-se a oxidação também em forno convencional, em ambiente de O2, com temperatura de 10000C e tempo de 100 min. O procedimento para o recozimento pós-implantação com posterior oxidação úmida é similar ao mostrado no item 3. A única diferença é que depois da entrada das lâminas no forno convencional ao invés de deixar os substratos em ambiente de N2 por 10min, aumente este tempo para 20 min para a execução do recozimento. O restante do procedimento é o mesmo já apresentado. Para controle dos processos coloca-se junto com as lâminas, onde estão sendo fabricados os dispositivos, as amostras testes T1, T2, T3 e T4. Obtém-se a medida de espessura do óxido crescido sobre os cacos T1 e T3. Remove-se com solução “Buffer” de HF o óxido crescido sobre caco T4. Mede-se no mesmo caco T4, a resistência de folha Rs e a profundidade de junção da camada implantada Xj. A medida de Rs é feita pelo equipamento de quatro pontas com descrito no item 1. Para a medida de Xj, desbasta-se mecanicamente a lâmina teste e com um líquido revelador obtém-se o contraste de imagem (verificada por um microscópio óptico) entre a parte dopada e a não dopada, como mostra a Figura 10. O resultado esperado para a região p+ da fonte/dreno é da ordem de 1,4m.

Óxido de Si

Substrato

Figura 9- Representação da lâmina de Si em corte lateral submetida ao recozimento para ativação de dopantes implantados com posterior oxidação úmida para formação de óxido na

região p+ de Fonte/Dreno

Figura 10 - Ranhura feita para medir profundidade de junção Xj

14

8. Processo Fotolitográfico do Segundo Nível de Máscara para Definição das Áreas de Porta e de Contatos Metálicos de

Fonte/Dreno. Remoção do Óxido de Campo sobre a Fonte/Dreno seguida da Remoção do Fotorresiste, Finalizando com a Limpeza

RCA.

Fonte/Dreno Porta

Óxido de Si

Substrato Figura 11- Representação da lâmina de Si em corte lateral submetida ao processo

fotolitográfico do segundo nível de máscara para definição das áreas de porta e de contatos metálicos com posterior remoção do óxido da fonte/dreno seguido da remoção do fotorresiste,

finalizando com a limpeza RCA.

O processo fotolitográfico do segundo nível de máscara é feito para a abertura no substrato das regiões de contatos metal-semicondutor de fonte/dreno e de porta, como mostra a Figura 11. O procedimento deste processo fotolitográfico é o mesmo apresentado no item 4. Para a abertura destas regiões no substrato, remove-se o óxido de campo crescido sobre a fonte/dreno com solução "Buffer" de HF, seguido da remoção do fotorresiste com as lâminas mergulhadas em acetona, finalizando com uma limpeza RCA completa. Os procedimentos destas etapas já foram descritos nos items 5 e 2, respectivamente.

9. Oxidação Seca para Crescimento do Óxido Fino de Porta

Óxido de Porta

Óxido de Campo

Substrato Figura 12- Representação da lâmina de Si em corte lateral submetida ao processo de oxidação

seca para crescimento do óxido fino de porta com 75nm de espessura.

Executa-se esta etapa para o crescimento do óxido de Si de porta, que forma a estrutura principal do dispositivo metal-óxido-semicondutor. A Figura 12 representa o óxido de Si crescido sobre o substrato de Si. Para isso, a espessura do óxido de porta deve ser menor que 100nm. Realiza-se a oxidação seca colocando-se as lâminas de Si no forno térmico convencional em alta temperatura de 1000 °C e em ambiente oxidante com cloro. A presença do cloro na mistura na forma de tricloroetileno, TCE, neutraliza os íons alcalinos, como o Na+, que podem estar presentes no ambiente de processo e são cargas móveis nos óxido de Si. Estas cargas respondem rapidamente e descontroladamente ao campo aplicado na região de porta dos dispositivos MOS, danificando-os. Portanto, emprega-se o cloro para manter o controle de contaminantes no ambiente oxidante. Para controle do processo, coloque os cacos T1, T2 e T3 junto com as lâminas inteiras onde serão confeccionados os dispositivos. Com os cacos T1, T2 e T3 pode-se medir as espessuras dos óxidos da região de porta , de fonte/dreno e de campo, respectivamente.

O procedimento de oxidação seca no CCS/UNICAMP é o seguinte:• Utilize o Forno de Oxidação com linha secundária de O2+TCE em temperatura de 1000 °C;• Execute a entrada da barqueta de quartzo com as lâminas no forno em ambiente de N2, com

fluxo de 1l/min, por um tempo maior que 3 min;• Deixe as lâminas neste ambiente de N2 por 5 min;• Desligue a linha de N2 , ligue a linha principal de O2 , com fluxo de 1l/min, e deixe as lâminas

neste ambiente por 5 min (oxidação seca sem cloro);

15

50nm

• Desligue a linha principal de O2 e ligue a linha secundária de O2+TCE, com aproximadamente 1% de TCE na mistura, para manter as lâminas em ambiente oxidante com cloro por 30 min (oxidação seca com cloro);

• Desligue a linha secundária de O2+TCE e ligue a linha principal de O2, para manter as lâminas em ambiente oxidante sem cloro por 5 min (oxidação seca sem cloro);

• Ligue a linha de N2 , com fluxo de 1l/min, e deixe as lâminas neste ambiente por 30 min (recozimento do óxido crescido);

• Execute a saída da barqueta de quartzo com as lâminas do forno em ambiente de N2, com fluxo de 1l/min, por um tempo maior que 3 min;

O óxido fino também cresce sobre a região exposta de fonte/dreno, como mostra a Figura 12. A espessura esperada do óxido de porta é da ordem de 50nm.

10. Processo Fotolitográfico do Terceiro Nível de Máscara para Definição das Áreas de Contatos Metálicos de Porta e de

Fonte/Dreno. Remoção do Óxido Fino sobre a Fonte/Dreno seguida da Remoção do Fotorresiste, Finalizando com a Limpeza RCA.

Fonte/Drenocom óxido removido

Porta

Óxido de Si

Substrato

Figura 13- Representação da lâmina de Si em corte lateral submetida ao processo fotolito-gráfico do terceiro nível de máscara para definição das áreas de contatos metálicos de porta e de fonte/dreno, com

posterior remoção do óxido fino sobre a fonte/dreno, seguido da remoção do fotorresiste, finalizando com a limpeza RCA.

Utilizando-se a terceira máscara, executa-se a fotogravação dos locais de abertura dos contatos metálicos de porta e de fonte/dreno. O procedimento deste processo fotolitográfico é o mesmo apresentado no item 4. Para a abertura destas regiões no substrato, remove-se o óxido de campo crescido sobre a fonte/dreno com solução "Buffer" de HF, seguido da remoção do fotorresiste com as lâminas mergulhadas em acetona, finalizando com uma limpeza RCA completa. Os procedimentos destas etapas já foram descritos nos itens 5 e 2, respectivamente.

11. Evaporação de Alumínio para a Formação de Contatos Metálicos de Porta e de Fonte/Dreno

Filme de Al

Fonte/Dreno

Porta

Óxido de Si

Substrato Figura 14- Representação da lâmina de Si em corte lateral submetida ao processo de

evaporação de Alumínio para a formação de contatos metálicos de porta e de fonte/dreno

Para formação de contatos metálicos de porta e de fonte/dreno, evapora-se uma camada de Al de 1m sobre toda a lâmina (Figura 14). No CCS/Unicamp, executa-se a evaporação introduzindo-se as lâminas em uma câmara de alto-vácuo com um sistema de feixe de elétrons, que é usado para fundir a fonte metálica, que se deseja depositar sobre o substrato. A fonte metálica utilizada é de Al com grau de pureza de 99,999%. A pressão de base para iniciar o processo é da ordem de 5 x 10 -7

Torr, que é obtida através de um sistema de vácuo acoplado que contém duas bombas de vácuo do tipos mecânica e difusora. Durante a evaporação, a pressão é de aproximadamente 5.10-5 Torr.

16

12. Processo Fotolitográfico do Quarto Nível de Máscara para Corrosão de Alumínio. Formação de Contatos Metálicos de Porta e

de Fonte/Dreno e de Interconexão Metálica de Dispositivos.

Contato de AlFonte/Dreno

Contato/Porta

Óxido de Si

Substrato

Figura 15- Representação da lâmina de Si em corte lateral submetida ao processo fotolitográfico do quarto nível de máscara para corrosão de Alumínio, obtendo-se a formação de contatos metálicos de porta e de fonte/dreno e de interconexão metálica entre dispositivos.

Utilizando-se a quarta máscara, executa-se a fotogravação dos locais entre os contatos, onde o filme de Al deve ser removido para se separar os contatos e as interconexões (Figura 15). O procedimento deste processo fotolitográfico é o mesmo apresentado no item 4. Após a fotogravação, executa-se a remoção do Al mergulhando-se as lâminas em solução de Ácido Orto Fosfórico + Acido Nítrico (9,5:0,5). A taxa de corrosão do Al nestas condições é de 300nm/min. Em seguida, executa-se a remoção do fotorresiste com as lâminas mergulhadas em acetona, como descrito anteriormente.

13. Evaporação de Al para Formação de Contato Metálico nas Costas do Substrato. Sinterização dos Contatos de Al.

Contato de AlFonte/Dreno

Contato de AlBase

Contato/Porta

Óxido de Si

Substrato

Figura 16- Representação da lâmina de Si em corte lateral submetida ao processo evaporação de Al para formação de contatos metálico nas costas do substrato com posterior

sinterização dos contatos de Al.

Para formação de contatos metálicos de base, evapora-se uma camada de Al de 1m sobre as costas da lâmina (Figura 16). O procedimento de evaporação já foi descrito no item 11. Para terminar os dispositivos, executa-se o processo de sinterização. No processo de sinterização dos contatos de Al, executa-se o recozimento das estruturas metal/semicondutor ou metal/óxido/semicondutor em baixa temperatura de aproximadamente 4500C e em ambiente inerte de N2 e de H2. Esta etapa serve para reestruturar as camadas e reduzir os defeitos nas interfaces das estruturas, que podem ter sido gerados durante a evaporação. Estes defeitos podem ser cargas superficiais de ligações incompletas nas interfaces. Estas ligações incompletas são saturadas pelo hidrogênio presente no ambiente. No CCS/UNICAMP, a fonte de hidrogênio no ambiente de sinterização é o vapor d’água que é arrastado do borbulhador para dentro do forno pelo gás N2.

O procedimento de sinterização de contatos de Al no CCS/UNICAMP é o seguinte:• Utilize o Forno de sinterização de contaos de Al em temperatura de 440 °C;• Execute a entrada da barqueta de quartzo com as lâminas no forno em ambiente de N2, com

fluxo de 1l/min, mais vapor d’água por um tempo maior que 3 min;• Deixe as lâminas neste ambiente de N2 mais vapor d’água por 30 min;• Execute a saída da barqueta de quartzo com as lâminas do forno em ambiente de N2, com

fluxo de 1l/min, mais vapor d’água por um tempo maior que 3 min. Finalizada a fabricação, a próxima etapa é a da caracterização elétrica dos dispositivos.

17

Relatório - Processos pMOS e nMOS tipo enriquecimento

Inicia-se agora uma jornada de três meses através dos processos descritos neste guia, com o intuito de se fabricar transistores pMOS e nMOS, tipo enriquecimento.

6 . R e m o ç ã o d o f o t o r r e s i s t e

7 . I m p l a n t a ç ã o I ô n i c a

a ) 1 1 B + , E = 5 0 k e V , 5 x 1 0 1 5 c m - 2

b ) 3 1 P + , E = 5 0 k e V , 5 x 1 0 1 5 c m - 2 , n a s c o s t a s d a l â m i n a .

8 . R e c o z i m e n t o e o x i d a ç ã o ú m i d a

9 . F o t o g r a v a ç ã o d e c a n a l e c o n t a t o s , e t c h d o ó x i d o e r e m o ç ã o d of o t o r r e s i s t e , f i n a l i z a n d o c o m a l i m p e z a R C A

1 1 . F o t o g r a v a ç ã o d e c o n t a t o s , e t c h d o ó x i d o e r e m o ç ã o d o f o t o r r e s i s t e ,f i n a l i z a n d o c o m a l i m p e z a R C A

1 2 . E v a p o r a ç ã o d e a l u m í n i o

1 3 . F o t o g r a v a ç ã o d e i n t e r c o n e x õ e s e e t c h d o a l u m í n i o , r e m o ç ã o d of o t o r r e s i s t e e s i n t e r i z a ç ã o d e c o n t a t o s

1 . L â m i n a s d e s i l í c i o d o t i p o n , ( 1 0 0 ) , c o m r e s i s t i v i d a d e e n t r e 4 e 6 o h m. c m . L â m i n a s p a r a d i s p o s i t i v o s m a i s u m a l â m i n a t e s t e .

M e d i d a s d e r e s i s t i v i d a d e ( 4 p o n t a s ) e e s p e s s u r a .

2 . L i m p e z a p a d r ã o R C A c o m p l e t a .

3 . O x i d a ç ã o ú m i d a , S i O 2 , X o x = 0 , 7 m i c r o n .

4 . A p l i c a ç ã o d o f o t o r r e s i s t e e e x p o s i ç ã o à l u z u l t r a v i o l e t a

5 . E t c h d o ó x i d o e m s o l u ç ã o d e H F / N H 4 F

Figura 1 - Processo pMOS do CCS/UNICAMP para a fabricação do chip teste

Esta jornada, entretanto, começou muito antes, com a obtenção das lâminas de silício que estão sendo entregues neste momento. Diversas etapas já foram realizadas até então, que vão desde a extração do quartzo, sua redução em Si policristalino (grau metalúrgico), sua purificação em níveis de ppba (grau eletrônico) até a obtenção de Si monocristalino do Si policristalino fundido, resultando em tarugos que, uma vez laminados, deram origem às lâminas.

Dependendo da orientação da semente utilizada, isto é, de um pedaço de Si monocristalino que inicia o processo de crescimento e da quantidade de dopantes inserida no seu decorrer (processo Czchochralski), as lâminas obtidas terão diferentes orientações cristalinas e dopagens.

Assim, antes do início de qualquer modificação nas lâminas, é mister caracterizá-las.

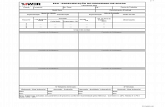

1. Caracterização das lâminas (Data: 13/08/2013)

18

Conforme a convenção do corte dos chanfros, identifique a orientação e o tipo de condutividade para os dois processos:

Figura 2 - Convenção de corte de chanfros para identificação da orientação e do tipo de condutividade

Processo pMOS: lâmina tipo N , orientação: (100)Processo nMOS: lâmina tipo P , orientação: (100)

O que motiva a escolha desta orientação?

Dada essa orientação obtemos um menor índice de defeitos por interface principalmente quando é realizada a clivagem uma vez que ela obedecera a orientação cristalina.

Para a certificação dos tipos de condutividade, utilize a medida de ponta quente. Logo percebido o porquê do nome da medida, o que dá origem ao deslocamento de portadores, portanto à corrente elétrica? Quem define o sentido da corrente?

O que da origem ao deslocamento de portadores é a energia térmica fornecida pela ponta quente que funciona como uma ddp de modo que os elétrons excitados irão se deslocar pelo material na direção da ponta fria. Quem define o sentido da corrente são os elétrons.

Sabido o tipo de condutividade, é preciso quantificar esta propriedade da lâmina através da densidade de impurezas aceitadoras ou doadoras.

Para isto, obtenha, primeiramente, a espessura t da lâmina. Utilize o relógio comparador:

Processo pMOS: t = 305 um Processo nMOS: t = 288 um

Em seguida, meça a resistência V / I através da medida de quatro pontas:19

Processo pMOS: ( V / I ) = (17.6mV/500uA) = 35,2 Processo nMOS: ( V / I ) = (22.4mV/200uA) = 11,2

Conhecido estes valores, calcule a resistividade da lâmina através da seguinte fórmula:

Quais as condições que determinam a validade da fórmula acima?

A validade dessa fórmula é dada pela distancia entre as pontas utilizadas na medida de 4 pontas, que irão determinar o valor da constante (no caso 4.53).

Processo pMOS: = 0,049.cm Processo nMOS: = 0,146.cm

Os valores obtidos estão de acordo com os fornecidos pelo fabricante?

A lâmina N estava fora dos padrões fornecidos pelo fabricante e a lâmina P estava dentro dos padrões.

Conhecido o valor de , obtenha NA e ND através do gráfico x NA,D:

Processo pMOS: ND = 8E+15 cm-3

Processo nMOS: NA = 2E+15 cm-3

Qual a relação entre a concentração de dopantes e a resistividade?

A relação é inversamente proporcional como pudemos observar no decorrer do experimento.

Como último cálculo, obtenha a resistência de folha ou resistência por quadrado:

Processo pMOS: RS = 159,5/quadradoProcesso nMOS: RS = 507,4/quadrado

No meio tempo entre a aula de hoje e a próxima, será realizado nas lâminas do processo nMOS tanto a limpeza completa, padrão RCA, como a implantação de íons de B, de acordo com os seguintes parâmetros:

Implantação Iônica de 11B+: energia E = 65 keV ; dose = 5E13 cm-2.

Por qual motivo isto é feito? A dopagem nas proximidades da superfície influencia no valor da tensão de limiar VT? Explique.

Esse processo é feito na lâmina P, pois quando é realizado o crescimento de oxido há uma perda do dopante (Boro) para o óxido por um processo de difusão. Uma vez que VT é diretamente proporcional a dopagem, se tivermos a perda do Boro e esta não for corrigida teremos um VT menor do que o desejado portanto há necessidade de uma implantação iônica de Boro antes da oxidação formando uma camada P+ na superfície da lâmina que será consumida durante a oxidação.

20

2. Limpeza padrão RCA completa (Data: 20/08/2013)

Para evitar o acúmulo de impurezas na interface entre o Si e o SiO2 que será formado, realize a limpeza padrão RCA completa, com a submersão da lâmina nas seguintes soluções:

H2SO4/H2O2 (4:1) em 80°C por 10 min (solução "piranha");

HF/H2O (1:10) em temperatura ambiente por 10s;

NH4OH/H2O2/H2O (1:1:5) em 80°C por 10 min;

HCl/H2O2/H2O (1:1:5) em 80°C por 10 min;

Entre uma solução e outra, as lâminas são submetidas a um enxágüe com água deionizada (DI), resistividade de 18 M.cm, por 3min. A secagem destas lâminas é feita com jato de nitrogênio.

Descreva as funções de cada etapa da limpeza.

Qual o grau de pureza dos reagentes adequado para o propósito em questão?

A pureza necessária para os reagentes é de 99,999% chamado de grau CMOS. A primeira etapa há a remoção de compostos orgânicos (gordura) porem existe a oxidação da lâmina que torna necessário a remoção do oxido por HF que é a segunda etapa. Ao final dessa etapa percebemos que o óxido foi removido, pois o silício é hidrófobo, portanto não retém água em sua superfície como faz o oxido. A limpeza RCA é a 3º etapa onde é removido metais de transição, cobre II, cálcio, magnésio e compostos orgânicos. A última etapa remove oxido de silício cobre I e metais alcalinos, da um polimento extra e minimiza a rugosidade. No intervalo entre cada etapa a lâmina é exposta por 1 minuto a água deionizada para lavagem do acido para que não haja interação entre os ácidos de cada etapa.

3. Oxidação Úmida (Data:20 /08 /2013 )

Com o intuito de isolar os dispositivos entre si e formar um anteparo para os processos vindouros, como a implantação iônica, inicia-se a oxidação úmida da lâmina de Si.

Por que a oxidação úmida é preferível à seca para a realização destas tarefas?

A oxidação úmida é preferível à seca, pois ela tem uma maior taxa de crescimento e como não é necessário um óxido de alta qualidade ela é a melhor alternativa.

Cônscio da função e do motivo da oxidação úmida, as lâminas são colocadas no forno de

oxidação, sob o seguinte regime de temperatura, ambiente e tempo:

Forno de oxidação, T = 1000 oCAmbiente Tempo (min)

N2 > 3N2 30O2 10

O2 + H2O 180N2 10N2 > 3

Descreva a função de cada etapa.

N2 >3min: Essa etapa é realizada para fazer com que as laminas cheguem a uma temperatura mais próxima a do interior do forno e assim quando empurradas para o fundo do forno elas não sofrerão estresse térmico devido a grandes variações de temperatura.

N2 30min: Essa etapa é realizada para reestruturar a camada cristalina devido a implantação de Boro nas laminas de processo nMOS.

21

O2 10min (oxidação seca): Essa etapa é realizada para que se crie um óxido de boa qualidade e evitar futuras falhas de empilhamento. Porem depois passamos a oxidação úmida pois esse processo tem uma taxa de oxidação baixa.

O2 + H2O 180min (oxidação úmida): Essa etapa é realizada para espessar a camada de óxido criada anteriormente esse processo é utilizado pois possui uma taxa de oxidação alta.

N2 10min (recozimento): Essa etapa é realizada para reestruturar as moléculas do óxido e retirar as possíveis bolhas de H2 que o processo de oxidação úmida libera como produto da reação ocorrida. Se esse processo não fosse realizado teríamos uma baixa tensão de ruptura devido a essas bolhas de H2.

N2 >3min: Essa etapa é realizada para não haver um choque térmico nas lâminas quando elas forem retiradas do forno.

Como dito no item 1, as lâminas são compostas de Si monocristalino, que foi obtido a partir de uma matriz também monocristalina, a semente. Nesta etapa, o óxido, além de consumir parte do Si da lâmina para a formação do SiO2, também está crescendo sobre a lâmina. Tendo estas considerações em mente, o que se pode afirmar sobre a estrutura cristalina do óxido?

Pode-se afirmar que não há estrutura cristalina uma vez que o SiO2 é amorfo.

Retomando a questão feita no item 1, existe alguma influência da orientação da superfície no que diz respeito à taxa de oxidação e à formação de defeitos? A orientação (100) é a mais vantajosa?

Finda a oxidação, meça a espessura da camada de óxido utilizando o interferômetro:

(lâmina N) tox = 738nm (lâmina P) tox = 755nm

Por fim, clive a lâmina de teste pMOS em quatro quadrantes, denominados T1, T2, T3 e T4 e a lâmina de teste nMOS também em quatro, T5, T6, T7 e T8, utilizando a caneta com ponta de diamante .

4. Fotogravação de fonte e dreno (1a máscara) (Data: 27/08/2013)

Realizada a oxidação, inicia-se a etapa de fotogravação de fonte e dreno. O primeiro passo desta etapa consiste na aplicação de fotoresiste sobre a lâmina. Entretanto, antes disso ser feito, a umidade relativa do ar deve ser observada. Por quê?

A umidade deve ser observada, pois o fotoresiste necessita da umidade controlada para ter uma boa aderência na lâmina de silício. No caso do fotoresiste utilizado a umidade recomendada é de 50%

Caso a condição de umidade não esteja satisfeita, aplique o promotor de aderência do resiste HDMS, a uma velocidade de 7000 rpm durante 40 s, para a uniformização da espessura da camada.

Na seqüência, aplique o fotoresiste AZ 1518, a 7000 rpm durante 40 s. Durante o processo de obtenção das lâminas de Si, uma de suas etapas consiste no arredondamento das bordas da lâmina. Relacione esta prática com a etapa em questão.

É realizado o arredondamento das bordas da lâmina para quando realizado o espalhamento do fotoressiste no spinner haja uniformidade na espessura do esmalte. Se não houvesse o arredondamento das bordas o fotorresiste se acumularia mais na borda do que no resto da superfície.

Feito isto, coloque a lâmina no hot plate à aproximadamente 100oC durante 1min para evaporação do solvente e fixação do fotoresiste.

Agora, com o auxílio da fotoalinhadora, grave o padrão da máscara no fotoresiste, expondo o conjunto em luz ultravioleta, polimerizando as regiões expostas de fotoresiste.

22

Realize a revelação do fotoresiste, utilizando o revelador MIF AZ 310 MIF

Descubra o significado da sigla MIF e, por consequência, sua importância para o processo.

MIF significa Metal Ion Free e isso é importante para o processo, pois se houvessem metais no revelador novas impurezas seriam introduzidas na lâmina, o que não é desejável.

Observe no microscópio a revelação feita.

Para finalizar, coloque as lâminas na estufa em 110ºC por 30 min para o enrijecimento do resiste não polimerizado.

5. Etch do óxido (Data: 27/08/2013)

Utilizando a solução-tampão (buffer) de HF e NH4F, remova o óxido das regiões expostas até que todo o óxido presente nas costas tenha sido removido. Com relação aos cacos T3, T4, T7 e T8, a remoção deve ser total.

Qual é a função do buffer? Por que se utiliza o HF?

A função do buffer é de manter o ph da solução constante durante a reação e o HF e utilizado para uma corrosão isotrópica do oxido.

Observe no microscópio a remoção feita. Atente para a remoção lateral, sob o fotoresiste.

6. Remoção do fotoresiste (Data 27/08/2013)

Feita a gravação no óxido, o fotoresiste, com sua missão cumprida, deve ser removido. Isto é feito utilizando-se acetona fria, seguida por isopropanol frio, acetona quente e H2O DI.

Terminado, faça a limpeza padrão RCA completa novamente.

Observe no microscópio o resultado final.

7. Implantação Iônica de fonte e dreno (Data:03/09/2013)

Nesta etapa serão formadas as regiões de fonte e dreno do transistor MOS. Para isto, é preciso alterar as dopagens nestas regiões. Uma das técnicas empregadas para este serviço é a implantação de íons. Quais são as vantagens desta técnica? Qual sua importância para a tecnologia MOS?

A técnica de implantação de íons e utilizada, pois tem-se controle da quantidade de íons implantada na lamina e consegue-se alta pureza dos íons dopantes uma vez que há um seletor de massa no implantador e também e possível controlar a profundidade de implantação através da energia fornecida ao íon.

Demarcadas as regiões de fonte e dreno, ajuste o implantador GA-4204 EATON conforme os seguintes parâmetros (inclua os cacos pMOS T3 e T4 e nMOS T7 e T8 no processo) :

Lâminas pMOS: I/ I de 11B+; E = 50 keV ; = 5E15 cm-2

Lâminas nMOS: I/ I de 31P+; E = 80 keV ; = 7E15 cm-2

Lâminas pMOS (costas): I/ I de 31P+; E = 50 keV ; = 5E15 cm-2

23

Descreva sucintamente o funcionamento do implantador de íons.

O implantador iônico é constituído por uma fonte de íons um sistema de aceleração e focalização do feixe , um sistema de varredura responsável por uma distribuição uniforme no implante do alvo, uma fonte de alta tensão e um sistema de vácuo.

Inicialmente o elemento dopante e selecionado através de sua massa atômica, esse processo é realizado por um defletor de íons que utiliza um campo magnético para direcionar o átomo desejado através do tubo de vácuo entre a fonte e a câmara de implantação, depois esses íons são acelerados com a energia necessária para ser implantado na lâmina. A lâmina deve estar com certo ângulo em relação ao feixe de íons para evitar que, se o íon tiver um diâmetro muito pequeno, ele atravesse a rede cristalina do silício, com esse ângulo garante-se que o íon ira se chocar em algum momento com algum átomo de silício da rede.

Por que é necessário aumentar a dopagem nas costas da lâmina n?

É necessário aumentar a dopagem das costas da lâmina N, para posteriormente ser feito o contato de corpo, e se essa dopagem não fosse feita o contato não seria ôhmico.

Finda a implantação, faça a limpeza padrão RCA completa.

8. Recozimento e oxidação úmida (Data:17/09/13)

Aparte das vantagens da técnica de implantação de íons existe uma desvantagem: a geração de defeitos na rede cristalina a ponto de amorfizar algumas regiões.

A solução para este problema, visando reconstruir estas regiões, é o recozimento térmico. Além deste, qual é o outro motivo para a realização do recozimento?

Outro motivo para a realização do recozimento é que ocorre a total ativação dos dopantes em um processo a 1000ºC/30min.

Aproveitando a necessidade do recozimento, a oxidação úmida é feita em conjunto para aumentar a espessura do óxido de isolação entre dispositivos.

Os parâmetros deste processo, do qual fazem parte todos os cacos, são os seguintes:

Forno de oxidação, T = 1000 oCAmbiente Tempo (min)

N2 > 3N2 5O2 10

O2 + H2O 100O2 10N2 10N2 > 3

Meça as seguintes espessuras com o interferômetro:

Lâmina P:toxT1 = 977nm (valor esperado: 0.8 m)toxT3 = 546nm (valor esperado: 0.6 m)

Lâmina N:toxT1 = 979nm (valor esperado: 0.8 m)toxT3 = 547nm (valor esperado: 0.6 m)

Por que toxT1 não cresceu na mesma proporção que toxT3?

Isso ocorreu, pois na parte já oxidada é necessário que o oxidante difunda no meio já oxidado e alcance o silício. Já na parte exposta o oxidante não precisa difundir e oxida a superfície do silício imediatamente.

24

Após isto, remova o óxido dos cacos T4 e T8 e meça RS e xj. Para medir xj, desbaste mecanicamente a lâmina e utilize o líquido revelador para contrastar a imagem entre a região dopada e a não dopada :

Processo pMOS: ( V / I ) =3.29 RS =14.92Processo nMOS: ( V / I ) = RS =

Processo pMOS: xj = 1.6m Processo nMOS: xj = 1.8m

Faça os comentários pertinentes.

9. Fotogravação de canal e contatos (2a máscara) (Data:01/10/13)

Seguindo os preceitos do item 4, realiza-se a fotogravação de canal e de contatos.

Observe a gravação feita no microscópio.

10. Etch do óxido (Data:01/10/13)

Utilizando a solução-tampão (buffer) de HF, remova o óxido das regiões expostas. Para o caso dos cacos T1 e T5, a remoção do óxido deve ser completa.

Observe no microscópio a remoção feita.

11. Remoção do fotoresiste (Data:01/10/13)

Remova o fotoresiste utilizando acetona fria, seguida por isopropanol frio, acetona quente e H2O DI.

Na seqüência, faça a limpeza padrão RCA completa.

Observe no microscópio o resultado final.

12. Oxidação de porta (Data:08/10/13)

O óxido formado nesta etapa deve ser o de melhor qualidade. Por quê?

O óxido de porta deve possuir melhor qualidade uma vez que ele deve ter alta tensão de ruptura e para evita fugas no capacitor que será formato entro o metal e o semicondutor.

Por que a espessura do óxido é reduzida cada vez mais?

Para que este objetivo seja alcançado, faz-se a oxidação segundo parâmetros a seguir. Inclua no presente processo os cacos T1, T2, T3, T5, T6 e T7.

Forno de oxidação, T = 1000 oCAmbiente Tempo (min)

N2 > 3N2 5O2 5

O2 + 1% TCE 30O2 5N2 30N2 > 3

Por qual motivo se utiliza O2 na terceira etapa? Explique o motivo do uso do TCE e de sua baixa concentração.

25

A terceira etapa é realizada para a obtenção de um óxido inicial de alta qualidade uma vez que o capacitor MOS deve possuir um bom dielétrico para possuir as características citadas anteriormente. Alem disso o O2 serve para eliminar a presença de N2 do forno que se combinado com TCE em alta temperatura iria formar o gás cinza, o mesmo ocorre na quinta etapa para eliminar o TCE do forno. O TCE é utilizado para remover as cargas móveis que estão presentes no óxido e que foram incorporadas durante o processo. A baixa concentração se deve ao fato que se houvesse excesso de TCE, a grande quantidade de cloro iria reagir formar HCl que por sua vez corroeria o SiO2.

Terminado o processo, meça as seguintes espessuras de óxido:

pMOStoxT1,T5 (óxido na região da porta) = 0.055 mtoxT3,T7 (óxido sobre S/D) = 0.0557 m toxT2,T6 (óxido de campo) = 0.0957 m

nMOStoxT1,T5 (óxido na região da porta) =0.0568 m toxT3,T7 (óxido sobre S/D) = 0.0604 m toxT2,T6 (óxido de campo) = 0.0960 m

Faça os comentários cabíveis.

13. Fotogravação dos contatos (3a máscara) (Data:15/10/13)

Considerada as ressalvas feitas no item 4 com relação à umidade, aplique o fotoresiste AZ 5214 à 4000 rpm durante 40 s. Por que se utilizou este fotoresiste em detrimento do AZ 1518?

Esse fotorresiste é utilizado, pois dado o tamanho da abertura do gate o AZ1518 não possui resolução suficiente e assim utiliza-se o AZ 5214.

Aplicado o fotoresiste, coloque as lâminas em estufa à 118 oC durante 2 min.

Na seqüência, grave o padrão da máscara correspondente, expondo as lâminas à luz ultravioleta.

Realize a revelação do fotorresiste, utilizando o revelador AZ 312 MIF e H2O DI (1:1).

Por fim, coloque as lâminas em hot plate à 118 oC durante 40 s.

Observe-as no microscópio.

14. Etch do óxido (Data:15/10/13)

Utilizando a solução-tampão (buffer) de HF, remova o óxido das regiões expostas. Para o caso dos cacos T3 e T7, a remoção do óxido deve ser plena.

Observe no microscópio a remoção feita.

Removido o óxido dos cacos T3 e T7, meça RS e xj:

Processo pMOS: ( V / I ) = 11.85 RS = 53.71/quadradoProcesso nMOS: ( V / I ) = 2.42 RS = 11/quadrado Processo pMOS: xj = 0.502 m Processo nMOS: xj = 0.662 m

Por que o óxido sobre a região dos contatos foi removido no item 9, uma vez que isto poderia ter sido feito nesta etapa?

26

Esse óxido é removido anteriormente, pois uma vez que ele possui uma espessura maior que o óxido criado na oxidação de porta, sua remoção seria muito demorada com uma solução de HF a temperatura ambiente.

15. Remoção do fotoresiste (Data:15/10/13)

Remova o fotoresiste utilizando acetona fria, seguida por isopropanol frio, acetona quente e H2O DI.Observe no microscópio.

16. Evaporação de Al, 1m (Data: 22/10/13)

Antes de depositar o Al, faça a limpeza padrão RCA sem a etapa da "piranha" e a de HF. Por que estas etapas foram excluídas?

Em seguida, ajuste os seguintes parâmetros na evaporadora:

Pressão base = 5 x 10-7 TorrPressão evaporação = 5.10-5 TorrTempo de evaporação = 3 min

Como funciona a evaporadora? Para que serve o planetário?

17. Fotogravação de interconexões (4a máscara) (Data: 22/10/13)

Como o Al foi depositado sobre toda a lâmina, é necessário retirar os curtos formados. Para isto repete-se, para a máscara em questão, o processo descrito no item 4.

Observe o resultado no microscópio.

18. Etch do Al (Data: 22/10/13)

Exposta a região de interesse, a remoção do Al é feita utilizando a solução H3PO4 (350 ml) + HNO3 (30 ml) até que todo Al exposto seja removido.

Qual a função de cada ácido na solução utilizada?

Observe no microscópio o resultado deste etch.

19. Remoção do fotoresiste (Data: 22/10/13)

Remova o fotoresiste utilizando acetona fria, seguida por isopropanol frio, acetona quente e H2O DI.

Observe no microscópio.

20. Evaporação de Al: 0.5 m nas costas das lâminas (Data: 29/10/13)

Para evitar o armazenamento de impurezas na interface Si e Al, limpe a lâmina com solventes.Em seguida, deposite o metal com o auxílio da evaporadora.

21. Sinterização de contatos (Data: 29/10/13)

Agora, coloque as lâminas no forno a 450 oC durante 30 min em ambiente de N2 com vapor d'água (ou gás verde). Por que se utiliza vapor d'água (ou gás verde)?

27

É possível classificar as cargas existentes no sistema SiO2 / Si em quatro tipos: cargas móveis, fixas, presas no óxido e presas na interface. Cite as fontes de cada uma e mencione as soluções adotadas no decorrer de todo o processo de modo a minimizar sua concentração.

28

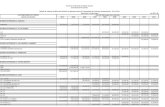

Medidas nos Chips Didáticos (Univ. Edinburg)

1.1) Resistores (chip 1)

a) Temperatura e resistência de folha:

O objetivo é verificarmos e estudarmos o efeito da temperatura sobre o valor da resistência de alguns resistores, e caracterizarmos os mesmos através de sua resistência de folha.

Para tanto utilizaremos o chip 1, cujo esquemático segue na figura abaixo.

R4

R6

R8

14

4

7

8

9

10

13

R3

R2R1

R7

R53

5

161

2 15

12

11

6

R9

contato do poço p

contato do substrato

Figura 1 – Chip didático I

Meça com um ohmímetro os resistores R3 (entre os pinos 2 e 15), R4 (entre os pinos 13 e 14) e R8 (entre os pinos 7 e 13), para duas temperaturas diferentes: ambiente e aproximadamente 77K (temperatura do nitrogênio líquido). Anote os valores na tabela abaixo:

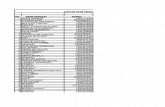

Tabela 1 – Resistências para temperaturas diferentes

Resistores Tambiente (~25o C) TLN2 (~77K)R3 2290Ω 2495 ΩR4 35 Ω 5 ΩR8 830 Ω 648 Ω

Para o calculo da resistência de folha (Rs), utilizamos a seguinte equação:

onde R é a resistência já medida, W e L as dimensões dos resistores (largura e comprimento respectivamente). Essas dimensões se encontram na tabela a seguir.

29

Tabela 2 – Dimensões dos resistoresResistores W (m) L (m)

R3 30 1680R4 10 10150R8 30 1680

De posse dos valores dos resistores e das dimensões dos resistores podemos então calcular a resistência de folha (Rs) e preencher a tabela abaixo:

Tabela 3 – Resistência de folha para temperaturas diferentes

Resistores Rs (~25o C) Rs (~77K)R3 40,9 Ω/folha 44.56 Ω/folhaR4 0,034 Ω/folha 0,005 Ω/folhaR8 14.82 Ω/folha 11,57 Ω/folha

Perguntas:

i) O que é mobilidade? Qual a sua influência sobre o valor dos resistores?ii) Baseado nos valores obtidos para os resistores (Tabela 1), classifique-os quanto ao seu material: metálico, semicondutor tipo n e tipo p. Explique o motivo de sua classificação.iii) Como a temperatura afeta os valores dos resistores? Esse efeito é igual para os três resistores?

Mobilidade é a capacidade de portadores de cargas moverem-se no meio. Quando medimos a resistência observamos que em diferentes temperaturas há uma mudança no valor medido. Isso se deve a alteração da mobilidade em função da temperatura no corpo do semicondutor ou metal. No caso de um semicondutor tipo P (resistor R3) a resistência em temperatura ambiente é menor que a resistência quando resfriado em nitrogênio liquido (à 77K) isso se deve pois o efeito da diminuição vibração térmica é suprimido pelo efeito do congelamento da rede cristalina que atrela os elétrons livres de volta ao núcleo do átomo. No caso do do resistor R8 (semicondutor tipo N) observamos a diminuição da resistência assim como no resistor R4 (tipo metálico) isso se da pelo efeito do aumento da mobilidade dos elétrons frente a diminuição da vibração térmica da rede.

b) Calculo de resistência através da característica VxI e 4 pontas:

Mediremos novamente o valor do resistor R3, utilizando para tanto a característica VxI, cuja montagem é mostrada na figura 2, e a medida de 4 pontas, que apresenta uma montagem diferente (também mostrada na figura 2), havendo a necessidade de se ter corrente circulando entre os pinos do resistor desejado (pinos 2 e 15) e de se medir a tensão entre outros dois pinos (1 e 16).

30

Figura 2 – Montagem para característica VxI e 4 pontas

Feitas as medidas, complete a tabela abaixo:

Tabela 4 – VxI e 4 pontas

Resistor VxI 4 pontasR3 2290Ω 2280 Ω

Perguntas:

i) Qual o princípio da medida de quatro pontas?ii) Qual tipo de medida é mais precisa? VxI ou 4 pontas? Explique.

O princípio da medida de quatro pontas é que será injetada uma corrente no resistor por 2 pontas e a queda de tensão é medida por outras duas pontas. Isso anula o efeito da resistência parasita das pontas de prova que ocorreria caso injetássemos corrente e medíssemos tensão com apenas um par de pontas, isso torna a medida de quatro pontas mais precisa.

31

2 15 2

1

15

16

1.2) Transistores (chip 2)

A esquema a seguir ilustra os dispositivos que compõem o chip 3 e sua respectiva pinagem:

figura 3 - Pinagem do chip 2

figura 4 - dispositivos do chip 2

Utilizando os transistores N3 e P4, realize as medições que seguem:

Utilizando os transistores N3 e P4, realize as medições que seguem abaixo:

a) Obtenha suas curvas características utilizando a HP4145 da sala de medições do CCS. Observe que a mesma possui alguns programas de medições de transistores e diodos prontos.

Abaixo estão as curvas ID x VDS (curva característica) dos transistores N3 e P4 que foram traçadas utilizando o programa PT1P1(para PMOS) e PTNP1(para NMOS).

32

Curva ID x VDS transistor N3:

Curva ID x VDS transistor P4:

33

b) Trace as curvas ID VGS ( HP4145 ) para VDS = 0,1V e VBS = 0V , 1,5V , 3,0V e 4,5V calculando os valores de VT, e (fator de corpo).

Utilizam-se os programas PT1P2(para PMOS) e PTNP2(para NMOS) para traçar as seguintes curvas desejadas:

Curva ID x VGS, transistor N3:

Curva ID x VGS, transistor P4:

34

Para N3:Vt (V) VBS

(V)1.83 0,0

Para P4:Vt (V) VBS

(V)-1.21 0,0-1.53 1,5-1.75 3,0-1.89 4,5

Cálculo do Fator de Corpo:Para o transistor canal-N observou-se que não houve variação de VT com a

tensão VBS, logo, = 0.Para o transistor canal-P, determinou-se , utilizando-se os valores de VT

em função da tensão VBS, da tabela acima e a equação

O valor médio de obtido foi = V½

c) Através das curvas de log(ID) VGS ( HP4145 ) na região sub-limiar com VBS = 0V e VDS = 0V , 1,5V , 3,0V e 4,5V , calcule o fator de idealidade destes transistores. Obs: pode-se traçar uma reta entre dois pontos da curva na HP, o que facilita a obtenção dos coeficientes angular e linear da reta ou mesmo copiar os dados da HP e colocá-los no software Origin.

Utilizamos o programa PT1P3(para PMOS) e PTNP3(para NMOS) para traçar as curvas abaixo.Curva log(ID) x VGS (região sublimiar) para N3:

O fator de idealidade para N3:.

n = [1/grad]/60mV = 1.011/grad = 60.7 mV/dec

Comentários:

35

Curva log(ID) x VGS (região sublimiar) para P4:

O fator de idealidade para P4: n = [1/grad]/60mV = 1.1

1/grad = -66mV/decComentários:

1.3) Diodos (chip 3)

A esquema a seguir ilustra os dispositivos que compõem o chip 3 e sua respectiva

pinagem:

figura 5 - Pinagem do chip 3

36

figura 6 - dispositivos do chip 3

a) Fator de idealidade, tensão de rompimento e capacitância de junção:

O modelo existente para a descrição do comportamento do diodo, proposto por Shockley, estabelece que:

;

onde k é a constante de Boltzmann T é temperatura em Kelvin [K]

Para chegar à este modelo, Shockley teve que fazer algumas aproximações, circunscrevendo o modelo à uma região de validade. Atentando para esta região, é possível verificar o quão próximo estão as condições dos diodos reais das assunções tomadas por Shockley.

Um modo para a verificação deste "quão próximo" é pela introdução de um fator no modelo acima, ad hoc, o chamado fator de idealidade . Assim, a expressão, para VD > 100

mV, o que implica em >> 1, fica:

De posse dos dados ID e VD, plotando ID em escala logarítmica, o fator advém diretamente do coeficiente angular do modelo linearizado:

37

Feitas estas considerações, com o chip no escuro, trace a curva I x V dos diodos D4, D7 e D8 utilizando o analisador de parâmetros HP 4145B, tanto em escala linear como em logarítmica (base 10).

Como a escala de ID está em base 10, o coeficiente angular da reta obtida está relacionado com por:

onde 1/GRAD é a denominação do inverso do coeficiente angular no analisador de

parâmetros.

Tabela 5 – Fator de idealidade

Diodo 1/GRAD [mV/dec] D4 60.6 1.01D7 60.4 1.007D8 60.8 1.013

À luz do que foi feito, comente os resultados obtidos.Observando novamente a expressão de Shockley, vê-se que, à medida que VD diminui,

ID tende à I0. Entretanto, conforme VD é diminuído, o modelo proposto deixa sua região de validade, não contemplando outros fenômenos. Quais fenômenos seriam estes?

Para verificar o comportamento dos três diodos na região reversa e encontrar o valor da tensão de rompimento (Breakdown Voltage BV), utilize o analisador de parâmetros, atentando para o limite do equipamento de +/-100V. Além disso, imponha o limite de 1 mA para a corrente no diodo.

Tabela 6 – Tensão de rompimento

Diodo BV [V]D4 -31.2VD7 <-100VD8 <-100V

A tensão de rompimento BV obtida acima pode ser ocasionada devido a dois dos fenômenos perguntados acima. No presente caso, qual seria o fenômeno responsável pelo valor obtido de BV? Qual o critério utilizado para esta distinção? Explique qualitativamente o fenômeno em questão.

Sabido a natureza do fenômeno, como poderia ter sido previsto a ordem das magnitudes obtidas (em módulo), por exemplo, BVD7 > BVD4 > BVD8? Respalde sua previsão, ou melhor, sua constatação, com base no leiaute do chip didático e na fórmula a seguir.

38

Além dos quesitos até aqui estudados, a característica ID x VD e o comportamento na região reversa, os diodos também possuem aplicação como capacitor de junção. Um exemplo disto é encontrado nos circuitos geradores de FM.

Para a caracterização desta capacitância é necessário o conhecimento da capacitância de junção CJ0, ou seja, o conhecimento do valor da capacitância sem a aplicação de tensão no diodo.

Sob esta condição, VD =0, meça CJ0 com o medidor de capacitância.

Tabela 7 – Caracterização da capacitância

Diodo CJ0 [pF]D4 10D7 8D8 7

Explique os resultados obtidos. Utilize os resultados obtidos para as tensões de BV, os dados das áreas dos diodos e a fórmula a seguir como auxílio:

AD4 = 100x100 m2, AD7 = 100x100 m2 e AD8 = 84x84 m2

figura 7 - Estrutura do diodo

b) Comportamento do diodo sob aplicação de luz

b.1) Característica ID x VD

Os parâmetros estudados anteriormente o foram sob a ausência de luz. Agora, a título de comparação, trace a característica do diodo D5, no escuro e sob a luz de maior intensidade da fonte luminosa. Utilize o HP 4145B.

Explique as diferenças observadas.

b.2) Potência gerada

Uma vez que pares elétron-lacuna podem ser gerado pelo processo conhecido como fotogeração, a análise da potência gerada pode ser feita conectando o diodo D5 à um resistor R = 1M, segundo o circuito abaixo:

39

figura 8 - Fotogeração

Anote o valor de tensão medido VR nas duas condições. Na condição com luz, utilize a máxima intensidade da fonte luminosa:

Tabela 8 – FotogeraçãoCondição VR [V]Sem luz 0,6μCom luz 0,6

Calcule a potência gerada Pg.

Sem luz: 6fW

Com luz:

0.36W

Sabendo que a área do diodo D5 é de A = 6000 m x 40 m = 2,4.10-7m2, calcule a potência por m2 P.

1.5

Calculado P, encontre a área necessária A1W para que uma potência de 1W seja gerada.

1m2 - P A1W = (2/3)m2

A1W - 1W

c) Influência da polarização reversa em ID

40

Uma vez analisado o efeito da luz, agora será estudado o comportamento da corrente ID variando-se a tensão de polarização reversa.

Para isto, utilize o analisador de parâmetros HP 4145B e complete a tabela abaixo:

Tabela 9 – Polarização reversa

VD [V]ID

Sem luz Com luz0 -0.09pA -466uA-4 -5pA -468uA-7 -6pA -492uA

Explique os resultados obtidos.

1.4) Oscilador em Anel (chip 4)