hpbl/relat%F3rio%20SD%20(falta%20... · Web viewAlém da ULA, implementaremos um somador BCD capaz...

Transcript of hpbl/relat%F3rio%20SD%20(falta%20... · Web viewAlém da ULA, implementaremos um somador BCD capaz...

UNIVERSIDADE FEDERAL DE PERNAMBUCO

CENTRO DE INFORMÁTICA

Projeto de Sistemas Digitais:

ULA e BCD

Bruno Henrique Lima Vieira de Melo (BHLVM)

Gustavo Gonçalves Borges (GGB)

Hilton Pintor Bezerra Leite (HPBL)

Renan de Freitas Lins (RFL3)

Ricardo Rossiter Barioni (RRB)

Victor Miranda de Melo (VMM)

Monitora Responsável:

Raíssa Gabrielle da Cunha Andrade (RGCA)

Recife, Pernambuco, Brasil.

2014

SUMÁRIO

1- INTRODUÇÃO...............................................................................2- DESENVOLVIMENTO....................................................................

2.2 CarryOut.............................................................................3.2

3- CONCLUSÃO.................................................................................

INTRODUÇÃO

Neste projeto visamos construir uma Unidade Lógica e Aritmética para realizar operações com vetores de 4bits (A e B) como a soma, subtração, complemento a 2, igualdade, comparação de menor e maior que, and e xor. Essas operações serão escolhidas de acordo com um vetor seletor de 3bits (S). O resultado dessas operações podem ser um vetor de 4bits (F) com um bit de overflow, caso a base estoure o limite, ou um outro bit que indica se a operação é verdadeira ou falsa.

Além da ULA, implementaremos um somador BCD capaz de somar números de dois dígitos quando na base 10. Assim como a Unidade, o BCD recebe dois vetores de 4bits sendo que o bit mais significativo não representa mais o sinal do vetor, possibilitando assim valores maiores. A saída consiste de um vetor resultante da soma e um bit de overflow.

Para a construção de cada um dos módulos componentes tanto do BCD quanto da ULA utilizaremos técnicas como a tabela verdade e o mapa de Karnaugh a fim de conseguir a forma mais reduzida do circuito a ser implementado.

Usaremos a plataforma QuartusII 9.1sp2 para a elaboração dos circuitos lógicos tomando proveito de suas funcionalidades como as portas lógicas básicas já existentes (AND, OR, XOR, ...) e a possibilidade de criar WaveForms que servem como teste do funcionamento dos circuitos.

DESENVOLVIMENTO

CarryOut:O CarryOut é um dos dois componentes do FullAdder, sendo composto

de três bits de entrada (A, B e CarryIn), e sua função é determinar se haverá estouro na soma de dois bits (A e B). Se houver estouro no FullAdder, o bit que sobrar (output “CarryOut” do FullAdder) será 1, o qual será aproveitado no FullAdder seguinte, entrando no parâmetro CarryIn. Porém, se tal FullAdder for o último da sequência, o CarryOut determinará se haverá estouro de bits ou não, a partir do output Overflow existente nas funções “Add/Subtract” e “Complemento a 2 de B”.

Fórmula reduzida : ((A + B).Cin) + (A.B)

Abaixo segue o WaveForm, a tabela verdade e o mapa de Karnaugh:

- WaveForm:

- Tabela Verdade:

- Mapa de Karnaugh:

Saída:A Saída é o segundo componente do FullAdder, sendo composto de três

bits de entrada (A, B e CarryIn), e sua função é realizar a soma de dois ou três bits (desconsiderando o estouro) sendo o terceiro bit o CarryIn se existente (este quando possuir valor 1).

Fórmula reduzida : (B xor Cin) xor A

Abaixo segue o WaveForm, a tabela verdade e o mapa de Karnaugh:

- WaveForm:

- Tabela Verdade:

- Mapa de Karnaugh:

Full Adder:O FullAdder é a unidade básica de soma de bits. Composto por três bits

de entrada (A, B e CarryIn), sua função é somar os três bits de entrada. Sua estrutura é basicamente a junção das funções “CarryOut” e “Saída”, que será utilizado na soma bit a bit das funções “Add/Subtract” e “Complemento a 2 de B”.

Vale ressaltar que, no FullAdder do bit menos significativo, o CarryIn é sempre 0, uma vez que não há um FullAdder anterior; logo, não há estouro. Já no FullAdder do bit mais significativo, seu output CarryOut será utilizado para determinar se há estouro (Overflow) nas funções “Add/Subtract” e “Complemento a 2 de B”. (Já enfatizado no tópico “CarryOut”).

Abaixo segue o WaveForm e a tabela verdade:

- WaveForm:

- Tabela Verdade:

Add/Subtract: Uma das funções-chave da ULA, o Add/Subtract é composto por dois

vetores de 4 bits de entrada (A[3..0] e B[3..0]) e um bit de entrada (AddSubtract). Sua função é realizar a soma ou a subtração, sendo selecionado pelo bit AddSubtract (0 para realizar soma e 1 para realizar subtração), dos dois vetores de entrada. Sua estrutura é formada por quatro FullAdder’s (um para cada bit correspondente dos vetores). O AddSubtract irá interagir com cada bit do vetor B a partir de um XOR, possibilitando a entrada do bit resultante do XOR no seu respectivo FullAdder.

Para a função Add/Subtract, temos duas saídas:

a) Soma[3..0] : vetor resultante da composição dos bits “resultado” da função FullAdder;

b) OVERFLOW : bit que determina se houve ou não estouro de bit na operação.

Obs: assim como dito no tópico “FullAdder”, o “CarryIn” do FullAdder do bit menos significativo da função “Add/Subtract” sempre terá o valor 0, uma vez que não há um FullAdder anterior, não existindo estouro.

Abaixo segue o WaveForm:

- WaveForm:

AandB:

O AandB é composto de dois vetores de entrada (A, B) tendo como função determinar a operação lógica AND entre os respectivos bits dos vetores de entrada. Se pelo menos um dos bits for 0, o bit resultante também será 0, caso contrário será 1. A saída será um vetor de quatro bits, composto pelo resultado do AND dos bits dos vetores de entrada.

Fórmula reduzida : { (A[0].B[0]) , (A[1].B[1]) , (A[2].B[2]) , (A[3].B[3]) }

Abaixo segue o WaveForm, a tabela verdade e o mapa de Karnaugh:

WaveForm:

Tabela Verdade:

Mapa de Karnaugh:

AxorB:O AxorB é composto de dois vetores de entrada (A, B) tendo como

função determinar a operação lógica XOR entre os respectivos bits dos vetores de entrada. Se os bits forem iguais, o bit resultante será 0, caso contrário será 1. A saída será um vetor de quatro bits, composto pelo resultado do XOR dos bits dos vetores de entrada.

Fórmula reduzida : { (A[0] xor B[0]) , (A[1] xor B[1]) , (A[2] xor B[2]) , (A[3] xor B[3]) }

Abaixo segue o WaveForm, a tabela verdade e o mapa de Karnaugh:

- WaveForm:

- Tabela Verdade:

- Mapa de Karnaugh:

Igualdade:Para comprovar a igualdade de dois vetores (A, B), precisamos

compará-los pelos seus respectivos bits. Se os bits forem iguais, o XNOR retornará 1, caso contrário, 0. Ao fazer a operação AND com os 4 bits saídos do XNOR, teremos como output 1 se todos os bits forem 1, ou seja, são iguais (A[x] = B[x]) e 0 se houver pelo menos um que seja diferente (A[x] != B[x]).S

Fórmula reduzida : (A[0] xnor B[0]) + (A[1] xnor B[1]) + (A[2] xnor B[2]) + (A[3] xnor B[3])

Abaixo segue o WaveForm, a tabela verdade e o mapa de Karnaugh:

- WaveForm:

- Tabela Verdade:

- Mapa de Karnaugh:

Complemento a 2:O Complemento a 2 de B é uma das operações principais da ULA, e sua função é, como já diz no seu nome, determinar o Complemento a 2 de B. Ele possui como entrada um vetor de 4 bits (B[3..0]), e tem como saída um vetor de 4 bits e um bit para determinar se há Overflow ou não.

A ideia do complemento a 2 de B segue a seguinte fórmula:

Complemento a 2 de B = + 1

Para realizar tal função, fazemos a negação do vetor de entrada(B[3..0]) e somamos a ele, utilizando FullAdder’s, o vetor “0001” (semelhante à operação de somar do “Add/Subtract”).

Para a função Complemento a 2 de B, temos duas saídas:

a) Complemento2[3..0] : vetor resultante da composição dos bits “resultado” dos FullAdder’s existentes na função “Complemento a 2 de B”;

b) OVERFLOW : bit que determina se houve ou não estouro de bit na operação.

Obs: assim como dito no tópico “FullAdder”, o “CarryIn” do FullAdder do bit menos significativo da função “Add/Subtract” sempre terá o valor 0, uma vez que não há um FullAdder anterior, não existindo estouro.

Abaixo segue o WaveForm:

WaveForm:

A < B (comparador de bit):Tal função é uma subexpressão da função “A < B”, e possui a função de

comparar, bit a bit, qual deles possui valor menor. Possui uma saída “Dout” que é levada para o “A < B (comparador de bit)” do bit seguinte, a fim de indicar se o vetor A[3..0], naquele instante, é menor que o vetor B[3..0].

OBS: essa função não é utilizada entre os últimos bits dos vetores A[3..0] e B[3..0].

Fórmula reduzida : (¬(A).Din) + (¬(A).B) + (B.Din)

Abaixo segue o WaveForm, a tabela verdade e o mapa de Karnaugh:

WaveForm:

Tabela Verdade:

Mapa de Karnaugh:

A < B (comparador de Sinal):Tal função é uma subexpressão da função “A < B”, e possui a função de comparar, bit a bit, qual deles possui valor menor. Possui uma saída “Dout” que é levada para o “A < B (comparador de bit)” do bit seguinte, a fim de indicar se o vetor A[3..0], naquele instante, é menor que o vetor B[3..0].

OBS: essa função não é utilizada entre os últimos bits dos vetores A[3..0] e B[3..0].

Fórmula reduzida : (¬(A).¬(B).DinSinal) + (A.¬(B).¬(DinSinal)) + (B.DinSinal)

Abaixo segue o WaveForm, a tabela verdade e o mapa de Karnaugh:

WaveForm:

Tabela Verdade:

Mapa de Karnaugh:

A < B:A função A < B é uma das operações da ULA, e possui a função de

comparar se a entrada A[3..0] é menor que a entrada B[3..0]. Possui em sua estrutura três comparadores de bit para os três bits menos significativos dos vetores A[3..0] e B[3..0] e um comparador de sinal para o bit mais significativo desses vetores, retornando o bit “AmenorB”, que indica se A[3..0] é menor que B[3..0].

OBS: No comparador de bit do bit menos significativo, a entrada “Din” é sempre 0, uma vez que não há comparadores de bits anteriores.

Abaixo segue o WaveForm:

WaveForm:

A > B (comparador de Bit):Tal função é uma subexpressão da função “A > B”, e possui a função de

comparar, bit a bit, qual deles possui valor maior. Possui uma saída “Dout” que é levada para o “A > B (comparador de bit)” do bit seguinte, a fim de indicar se o vetor A[3..0], naquele instante, é maior que o vetor B[3..0].

OBS: essa função não é utilizada entre os últimos bits dos vetores A[3..0] e B[3..0].

Fórmula reduzida : (¬(A).¬(B).D) + (A.¬(B)) + (A.B.D)

Abaixo segue o WaveForm, a tabela verdade e o mapa de Karnaugh:

WaveForm:

Tabela Verdade:

Mapa de Karnaugh:

A > B (comparador de Sinal):

Tal função é uma subexpressão da função “A > B”, usada apenas para o bit mais significativo dos vetores A[3..0] e B[3..0], e possui como saída um bit “Dout” que indica se o bit A[3] é maior que o bit B[3].

OBS: a) para a posição [3], 1 = negativo e 0 = positivo

Fórmula reduzida : (¬(A).¬(B).DinSinal) + (¬(A).B.¬(DinSinal)) + (B.DinSinal)

Abaixo segue o WaveForm, a tabela verdade e o mapa de Karnaugh:

- WaveForm:

- Tabela Verdade:

- Mapa de Karnaugh:

A > B:A função A > B é uma das operações da ULA, e possui a função de

comparar se a entrada A[3..0] é maior que a entrada B[3..0]. Possui em sua estrutura três comparadores de bit para os três bits menos significativos dos vetores A[3..0] e B[3..0] e um comparador de sinal para o bit mais significativo desses vetores, retornando o bit “AmaiorB”, que indica se A[3..0] é maior que B[3..0].

OBS: No comparador de bit do bit menos significativo, a entrada “Din” é sempre 0, uma vez que não há comparadores de bits anteriores.

Abaixo segue o WaveForm:

- WaveForm:

Mux(4:1) Vetores:O Mux(4:1) Vetor é um multiplexador, utilizado na ULA, para selecionar

qual vetor de 4 bits deverá ser retornado, caso a operação realizada na ULA possua pelo menos um vetor de 4 bits como retorno. Possui como entradas os vetores A[3..0], B[3..0], C[3..0] e D[3..0], os quais representam, respectivamente, as funções “Add/Subtract”, “Complemento a 2 de B”, “AandB” e “AxorB”. Além desses vetores, há um vetor de entrada S[2..0] o qual determinará qual operação será realizada. Caso nenhuma das operações de retorno vetorial seja escolhida, implicará num retorno de vetor “0000” (falso).

Fórmula reduzida : (A.¬(S[2]).¬(S[1])) + (B.¬(S[2]).S[1].¬(S[0])) + (C.S[2].S[1].¬(S[0])) + (D.S[2].S[1].S[0])

Abaixo segue a tabela verdade:

- Tabela Verdade:

Mux(2:1) Overflow :O Mux(2:1) Overflow é um multiplexador, utilizado na ULA, para

selecionar qual bit de overflow deverá ser retornado, caso a operação realizada na ULA possua pelo menos um bit de overflow como retorno. Possui como entradas os vetores A[3..0], B[3..0], os quais representam, respectivamente, as funções “Add/Subtract” e “Complemento a 2 de B”. Além desses vetores, há um vetor de entrada S[2..0] o qual determinará qual operação será realizada. Caso nenhuma das operações de retorno vetorial seja escolhida, implicará num retorno de bit 0 (falso).

Fórmula reduzida : (A.¬(S[2]).¬(S[1])) + (B.¬(S[2]).S[1].¬(S[0]))

Abaixo segue o WaveForm e a tabela verdade:

- WaveForm:

- Tabela Verdade:

Mux(3.1) bits:

O Mux(3:1) Bit é um é um multiplexador, utilizado na ULA, para selecionar qual bit booleano deverá ser retornado, caso a operação realizada na ULA possua um bit booleano como retorno. Possui como entradas os bits A, B e C, os quais representam, respectivamente, as funções “Igualdade”, “AmaiorB”, “AmenorB”. Além desses vetores, há um vetor de entrada S[2..0] o qual determinará qual operação será realizada. Caso nenhuma das operações de retorno vetorial seja escolhida, implicará num retorno de bit 0 (falso).

Fórmula reduzida : (A.¬(S[2]).S[1].S[0]) + (B.S[2].¬(S[1]).¬(S[0])) + (C.S[2].¬(S[1]).S[0])

Abaixo segue o WaveForm e a tabela verdade:

- WaveForm:

- Tabela Verdade:

ULA:A ULA é a denominada Unidade Lógica e Aritmética. Ela possui como entrada dois vetores de 4 bits A[3..0] e B[3..0] e um vetor de 3 bits para seleção S[2..0]. De acordo com a entrada do vetor S[2..0], podemos selecionar uma das 8 operações lógicas da ULA:

a) A + B;b) A – B;c) Complemento a 2 de B;d) Igualdade;e) AmaiorB;f) AmenorB;g) AandB;h) AxorB

A ULA também possui em sua composição os seguintes Mux’s:

a) Mux(4:1)Vetor : Seleciona o vetor-resposta de saída correspondente à operação realizada (caso a operação não retorne um vetor-resposta, terá como saída o vetor “0000” [falso]).

b) Mux(2:1)Overflow : Seleciona o bit de overflow de saída correspondente à operação realizada (caso a operação não retorne um bit de overflow, terá como saída o bit 0 [falso]).

c) Mux(3:1)Bit : Seleciona o bit booleano de saída correspondente à operação realizada (caso a operação não retorne um bit booleano, terá como saída o bit 0 [falso]).

OBS: Cada “Mux” gerará seu tipo de saída correspondente:

a) Mux(4:1)Vetor Vetor-respostab) Mux(2:1)Overflow Bit de overflowc) Mux(3:1)Bit Bit booleano

Abaixo segue o WaveForm, a tabela verdade e o mapa de Karnaugh:

- Tabela Verdade:

- Mapa de Karnaugh:

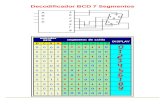

AdderBCD: O Somador BCD (sigla para Binary Code Decimal) é representada pela

adição de dois vetores, porém é característico de sua estrutura lidar com o estouro da base 10 (caso o número, em binário, ultrapasse 9). Caso ultrapasse 9, precisamos separar os dígitos.

Quando temos uma soma de números os quais são maiores que 9 e menores que 20, temos que subtrair 10 do resultado (considerando o estouro) e após isso somamos 6 para corrigir o resultado. Porém, só subtraímos 10 nos casos dos números de formato 11XX, 1X1X e 1XXXX (afinal, são números maiores que 10). Logo, além do usual somador de 4 bits (encontrado na função AddSubtract da ULA), inserimos os FullAdder que farão a subtração de 10 caso haja estouro.

Após disso, usamos um OR para tratar os três casos de estouro de base ditos anteriormente (esse estouro pode ser interpretado como um Overflow). Além disso, é colocado um XOR entre a saída da última caixa extra e a saída da ultimo FullAdder normal, a fim de se determinar o último dígito do resultado.

Abaixo segue o WaveForm:

- WaveForm:

CONCLUSÃO

A implementação de uma ULA e um BCD nos proporcionou um maior contato com operações lógicas e montagens de circuitos computacionais que são essenciais para o funcionamento de qualquer computador, mas muitas vezes são esquecidos por alunos de cursos da área de tecnologia que se prendem a programação de mais alto nível, sem saber o que está acontecendo por trás do código, possibilitando sua execução.

O projeto exigiu grande dedicação e comprometimento dos integrantes do grupo, levando a horas de imersão no ambiente do QuartusII para atingir o melhor resultado possível. Vale ressaltar o aprendizado que o grupo adquiriu em relação à portas logicas e vetores de entrada e saída.

![Código BCD [Autoguardado]](https://static.fdocumentos.com/doc/165x107/55cf947e550346f57ba26289/codigo-bcd-autoguardado.jpg)